用于测试电路的通用压缩器架构的制作方法

1.当前公开的技术涉及电路测试。所公开技术的各种实施方式对于抑制电路测试响应中的x状态是特别有用的。

背景技术:

2.测试数据压缩被广泛认为有助于降低基于扫描的半导体器件测试的总体成本。利用积极的技术扩展,与测试刺激压缩协同工作的测试响应压缩在处理测试数据量增长中起到关键作用。对于压缩方案的开发反映了许多应用的不断变化的需求,并且解决了消费者对于以较低成本获得更高性能的永不满足的需求。最近再次出现了与片上测试压缩集成的逻辑内建自测试(logic built-in self-test,lbist),作为可行的系统内测试替代方案。在许多情况下,这种混合技术被认为是安全的机制,其可以在器件的运行时间期间被周期性地应用,以检测车辆集成电路和其它安全关键性应用中的故障。该混合技术提供在非常短的时间段内可达到的高测试覆盖率,包括现场测试过程。由于测试压缩与lbist之间的架构差异逐渐模糊,可测性设计(design for test,dft)实施方式可以在两种方法之间有效地共享测试逻辑,包括测试响应压缩器。因此,对于可靠的压缩器的重要要求是保持扫描单元的可观测性,同时(1)维持非常高的压缩率,(2)提供对在实际硅中发现的各种故障进行检测的能力,以及(3)确保设计简单性。

3.测试响应压缩易受未知(x)状态的影响,这会使测试变得无用。由于未初始化的存储器元件、非扫描的触发器、总线争用、浮动的总线、未包装的模拟模块、内部三态逻辑、跨时钟域信号、时序异常、或在生成速度测试时的多周期和错误路径,因此在复杂的设计中会出现x值。这些状态一旦在扫描单元中被捕获到,随后可能被注入到测试响应压缩器中,在这里它们将严重影响测试结果。特别地,由于通过时间压缩器(例如,多输入特征寄存器(multiple-input signature register,misr))部署的反馈,x状态可以激增。虽然模块化时间压缩器通过循环寄存器来防止未知状态的大量增加,但是循环寄存器只能部分地减少x状态的负面影响。组合式压缩器保持相对不受x状态的影响,但是为了避免掩蔽(masking),它们需要在两个或更多个输出端上观察每个扫描链。有限存储器压缩器在多个扫描移位周期中将x状态从其寄存器中清空。然而,即使测试压缩器被设计成容忍一定数量的x状态,这些x状态也可能快速占上风,从而妨碍了许多扫描单元的可观测性,并导致故障覆盖率下降。因此,压缩器需要能够通过例如部署扫描链选择方案来有效地掩蔽x状态的保护机制。

4.选择性地观察扫描链的能力已被广泛研究多年。所提出的方案提供了片上逻辑复杂度、附带损害(表示非x值的无意掩蔽)和控制x-掩蔽所需的测试数据之间的各种权衡。例如,一种被称为opmisr的方案使电路具有掩蔽所选卸载值的特征,使得x状态不会到达压缩器。在另一种方案中,选择性压缩器被用作嵌入式确定性测试(embedded deterministic test,edt)技术的组成部分。其通过部署寄存器文件以对目标扫描链进行编码来掩蔽给定数量的扫描链。在又一种方案中,使用lfsr(linear-feedback shift register,线性反馈

移位寄存器)重播来每周期门控扫描链。以这种方式获得的掩蔽信号可以通过“与(and)”移相器输出来进一步形成,以降低阻断非x响应的概率。在又一种方案中,每个输入端连接到两个输出端,并且每两个输出端在x耐受确定性bist的两级选择器中共享单独的输入端。其允许观察小部分的扫描链。在又一种方案中,x-掩蔽逻辑允许一定量的过度掩蔽,同时它是被作为无关的逻辑合成的实例而获得的,其中输入是由任何lbist或测试压缩方案提供的。在又一种方案中,通道掩蔽或者禁用所有扫描链,或者以可能过度掩蔽的代价来选择属于两个组中的一组的扫描链。在又一种方案中,采用两级扫描选择机制和顺序的过驱动部分。这些模块使用用于处理宽范围的x状态配置文件(profile)和引导抑制x状态的扫描链排序算法而连接在一起。在又一种方案中,执行对扫描链的类似bist的选择性掩蔽以在每周期阻断x状态。这依赖于一个发现:基于扫描的设计中的许多测试响应具有相同或相似的x状态模式,这些x状态模式发生在扫描链的连续区域和相邻区域中。

5.不同类别的解决方案试图使测试响应压缩器是容忍x的。例如,可以使用加权的伪随机模式发生器(weighted pseudorandom pattern generator,prpg)来实施容忍x的多输入特征寄存器。在该方案中,存储元件之间没有数据传输和高x掩蔽概率是x容忍度的基础。在另一种方案中,x过滤器从由纠错码压缩的测试响应中去除x状态的影响,同时保留它们的基本功能。类似地,基于misr的方案能够处理给定数量的x状态。该方案周期性地应用x过滤以抵消多个x并恢复原始特征的所有位(bit),该原始特征随后被卸载。还可以通过利用施泰纳(steniner)系统作为特定种类的系统组合块设计过程来设计卷积压缩器,该卷积压缩器容忍单个时间帧中的一定数量的x值。然而,尽管尽了最大努力,容忍x的压缩器仍可能需要采用对扫描链的掩蔽。实际上,在许多应用中,x容忍度不足以防止对测试结果的损坏,除非部署昂贵且复杂的测试逻辑来有效地应对未知值的大量激增(large burst)。因此,扫描链选择仍然是x-掩蔽领域中的主流技术。

6.用于测试压缩和逻辑bist的收敛应用的x-掩蔽方案必须响应现场和系统内测试的多个挑战和严格要求。首先,对于宽范围的x状态配置文件,控制扫描选择至关重要,并且附加信息量最少,使得该数据不会危害有效的测试压缩率。此外,由于x-掩蔽硬件在许多扫描选择方案中仍然占据不可忽略的空间,因此必须减少这种开销,特别是在具有可能需要可编程和非常灵活的选择算法的数百个(甚至数千个)扫描链的设计中。因此,需要开发新的扫描链选择方案,该扫描链选择方案包括简单的和模块化的扫描选择逻辑,该扫描选择逻辑允许在可重新限定的扫描链组和指定的扫描移位周期内掩蔽x状态。

技术实现要素:

7.所公开技术的各个方面涉及用于测试响应压缩的基于扫描选择的x-掩蔽。在一个方面,具有一种电路,其包括:包括扫描单元的扫描链,所述扫描链被配置以移入测试模式、将所述测试模式应用到所述电路、捕获所述电路的测试响应、以及移出所述测试响应;测试响应压缩器,其被配置以压缩所述测试响应;和扫描门控装置,其插置在所述扫描链的输出端与所述测试响应压缩器的输入端之间,所述扫描门控装置将所述扫描链划分成扫描链组,所述扫描门控装置中的每一者从所述扫描链组中的一者的输出端接收信号,并且基于第一信号以启用模式或禁用模式进行操作,其中,以所述启用模式操作的扫描门控装置基于第二信号阻断、仅在一个或更多个时钟周期处阻断、或不阻断由扫描链组中的扫描链捕

获的并从该扫描链输出的测试模式的测试响应的一部分到达所述测试响应压缩器,其中,所述扫描链组中的所述扫描链耦合到所述以所述启用模式操作的扫描门控装置,以及其中,以所述禁用模式操作的扫描门控装置不阻断、或基于第三信号阻断或不阻断由所述扫描链组的每一者中的所有扫描链捕获的并从所述所有扫描链输出的测试模式的测试响应的一部分到达所述测试响应压缩器,其中,所述扫描链组的每一者中的所述所有扫描链耦合到以所述禁用模式操作的扫描门控装置。

8.所述电路还可以包括:地址转换和解码电路,所述地址转换和解码电路被配置以基于地址信号、或所述地址信号和第四信号的组合、或所述地址信号、第四信号和第五信号的组合来生成所述第一信号,其中,所述第四信号的位能够覆盖所述地址信号的位,以增加正被启用的扫描门控装置的数量,并且其中,所述第五信号允许启用扫描门控装置的直接邻近扫描门控装置。可替代地,该电路还可以包括:配置寄存器,该配置寄存器被配置以存储第一信号并且将第一信号提供给所述扫描门控装置中的每一者。

9.所述电路还可以包括:选择器,所述选择器被配置以基于选择信号和阻断接通信号以及阻断关断信号来生成所述第二信号,其中,所述选择信号限定要阻断的时钟周期,并且其中,所述阻断接通信号和所述阻断关断信号的组合确定哪个扫描链输出要被阻断、要不被阻断、或基于所述选择信号要被阻断。

10.所述电路还可以包括:伪随机模式发生器,其被配置以生成测试模式;和解压缩器,其被配置以提供信号,至少基于该信号来生成所述第一信号和所述第二信号。

11.所述电路还可以包括:比较装置,其被配置以将来自测试响应压缩器的输出信号与参考信号进行比较。

12.所述电路还可以包括:解压缩器,其被配置以将压缩的测试模式解压缩成测试模式。所述解压缩器可以包括铃流发生器和移相器。

13.每个扫描门控装置可以包括多个子单元,所述子单元中的每一者包括用于耦合到所述扫描门控装置中的每一者的所述扫描链组中的每个扫描链的多路复用器和与门。

14.所述测试响应压缩器可以包括异或门网络或反相器网络。

15.在另一方面,具有一种或多种存储有计算机可执行指令的计算机可读介质,所述计算机可执行指令用于使一个或多个处理器执行方法,所述方法包括:创建电路设计中的电路,用于测试根据所述电路设计制造的芯片。

16.在所附独立权利要求和从属权利要求中阐述了某些发明方面。来自从属权利要求的特征可以与独立权利要求的特征和其它从属权利要求的特征适当地结合,而不仅仅是如权利要求中明确阐述的那样。

17.以上已描述了各个发明方面的某些目的和优点。当然,应当理解,所有这些目的或优点并不一定都可以根据所公开技术的任何特定实施例来实现。因此,例如,本领域技术人员将认识到,可以以实现或优化如本文所教导的一个优点或一组优点的方式来体现或实施所公开的技术,而不必实现如本文所教导或建议的其他目的或优点。

附图说明

18.图1例示了所公开的技术的各个实施例可采用的可编程计算机系统。

19.图2例示了根据所公开的技术的各个实施例的测试响应压缩系统的示例。

20.图3例示了由第一信号启用的扫描门控装置的示例。

21.图4a例示了由第一信号禁用的扫描门控装置的示例,其基于第三信号允许由扫描链组中的扫描链捕获的测试响应通过。

22.图4b例示了由第一信号禁用的扫描门控装置的示例,其基于第三信号阻断由扫描链组中的扫描链捕获的测试响应通过。

23.图5例示了根据所公开的技术的各个实施例的具有提供控制信号(第一信号、第二信号和第三信号)的电路的扫描门控装置的框图的示例。

24.图6例示了用于控制对配置寄存器的访问的配置插入位电路的示例。

25.图7例示了根据所公开的技术的各个实施例的具有提供控制信号(第一信号、第二信号和第三信号)的电路的扫描门控装置的框图的另一示例。

26.图8例示了根据所公开的技术的各个实施例的地址转换器的示例。

27.图9例示了有助于邻近扫描门控装置的同时选择的地址解码器的示例。

28.图10例示了使用两条附加控制线来启用扫描门控装置gk以及g

k+1

、或g

k+1

和g

k+2

、或g

k+1

、g

k+2

和g

k+3

的地址解码器的示例。

29.图11例示了包括用于从g3到g9的扫描门控装置的逻辑的地址解码器的详细架构的示例。

30.图12例示了根据所公开的技术的各个实施例的被配置以生成第二信号的选择器的示例。

31.图13例示了根据所公开的技术的各个实施例的测试压缩逻辑的示例,该测试压缩逻辑采用配置寄存器来向扫描门控装置提供第一信号。

32.图14例示了根据所公开技术的各个实施例的测试压缩逻辑的示例,该测试压缩逻辑采用地址转换器来向扫描门控装置提供第一信号。

33.图15例示了利用所公开技术实施的逻辑bist方案的示例。

34.图16例示了用于提供用于帮助产生控制信号的信号的小型解压缩器的架构的示例。

具体实施方式

35.总体考虑

36.所公开技术的各个方面涉及用于测试响应压缩的基于扫描选择的x-掩蔽。在下面的描述中,出于解释的目的而阐述了许多细节。然而,本领域普通技术人员将认识到,可以在不使用这些特定细节的情况下来实践所公开的技术。在其他情况下,为了避免混淆所公开的技术,并未详细描述已知特征。

37.本文描述的一些技术可以以存储在计算机可读介质上的软件指令、在计算机上执行的软件指令、或这两者的某种组合来实施。例如,所公开的一些技术可以被实施为电子设计自动化(electronic design automation,eda)工具的一部分。这些方法可以在单独的计算机上或在联网的计算机上执行。

38.虽然为了便于呈现所公开的方法的操作是以特定的顺序来描述的,但是应当理解,除非下面所述的特定语言需要特定的顺序,否则这种描述方式包括重新排序。例如,在一些情况下,可以重新排序或同时执行按顺序描述的操作。此外,为了简单起见,所公开的

流程图和框图通常并未示出可以结合其他方法来使用特定方法的各种方式。

39.对方法或装置的详细描述有时使用诸如“阻断”和“生成”的术语来描述所公开的方法或装置的功能/结构。这些术语是高级描述。对应于这些术语的实际操作或功能/结构将根据具体实施方式而变化,并且对于本领域普通技术人员是容易识别的。

40.另外,如本文所使用的,术语“设计”旨在涵盖描述整个集成电路装置的数据。该术语还旨在涵盖描述整个装置的一个或多个部件(例如集成电路装置的一部分)的较小的数据组。

41.说明性操作环境

42.可以通过由计算装置(例如可编程计算机)执行软件指令来实施所公开技术的各个示例。相应地,图1示出了计算装置101的说明性示例。如该图所示,计算装置101包括具有处理单元105和系统存储器107的计算单元103。处理单元105可以是用于执行软件指令的任何类型的可编程电子装置,但其通常是微处理器。系统存储器107可以包括只读存储器(rom)109和随机存取存储器(ram)111。如本领域普通技术人员所理解的,只读存储器(rom)109和随机存取存储器(ram)111都可以存储用于由处理单元105执行的软件指令。

43.处理单元105和系统存储器107通过总线113或替代性通信结构直接地或间接地连接到一个或多个外围装置。例如,处理单元105或系统存储器107可以直接地或间接地连接到一个或多个附加存储器存储装置,例如“硬”磁盘驱动器115、可移动磁盘驱动器117、光盘驱动器119、或闪存卡121。处理单元105和系统存储器107还可以直接地或间接地连接到一个或多个输入装置123和一个或多个输出装置125。输入装置123可以包括例如键盘、指点装置(例如鼠标、触摸板、触控笔、轨迹球或操纵杆)、扫描仪、相机和麦克风。输出装置125可以包括例如监视器显示器、打印机和扬声器。在计算机101的各种示例中,一个或多个外围装置115-125可以与计算单元103一起容纳在内部。可替代地,一个或多个外围装置115-125可以在计算单元103的外壳的外部并且例如通过通用串行总线(usb)连接与总线113连接。

44.在一些实施方式中,计算单元103可以直接地或间接地连接到一个或多个网络接口127,用于与构成网络的其他装置进行通信。网络接口127根据一个或多个通信协议(例如传输控制协议(tcp)和因特网协议(ip))将来自计算单元103的数据和控制信号转换成网络消息。此外,接口127可以采用任何合适的连接代理(或代理的组合)来连接到网络,所述连接代理包括例如无线收发器、调制解调器或以太网连接。这种网络接口和协议是本领域已知的,因此在此不再详细讨论。

45.应当理解,计算机101仅被例示为示例,并且并不旨在对其进行限制。可以使用包括图1所例示的计算机101的部件的一个或多个计算装置来实施所公开技术的各个实施例,所述一个或多个计算装置仅包括图1所例示的部件的子集,或者包括未在图1中示出的部件的各部件的替代性组合。例如,可以使用多处理器计算机、布置在网络中的多个单处理器和/或多处理器计算机、或这两者的某种组合来实施所公开技术的各个实施例。

46.用于测试的设计、测试模式生成、及测试

47.特征尺寸的减小增加了集成电路中的制造缺陷导致故障芯片的可能性。非常小的缺陷可导致有故障的晶体管或有故障的互连线。即使是单个有故障的晶体管或线也会导致整个芯片工作不正常。然而,制造缺陷是不可避免的,无论制造过程是处于原型阶段还是大批量制造阶段。因此,必须在制造过程中对芯片进行测试。还需要诊断故障芯片以提升产能

并维持制造良率。

48.测试通常包括对被测试电路施加一组测试刺激(测试模式),并然后分析由被测试电路产生的响应。功能性测试试图验证被测试电路是否是根据其功能性规范操作的,而结构性测试试图确定被测试电路是否已经如结构网表中所指定的那样由一些低级构造块正确地组装而成,并且这些低级构造块及其接线连接已经被制造而不存在缺陷。对于结构性测试,假设如果功能性验证已经示出了网表的正确性并且结构性测试已经确认了结构性电路元件的正确组装,则电路应该正确地工作。结构性测试至少部分地被广泛采用,因为它使得测试(测试模式)生成能够聚焦于测试有限数量的相对简单的电路元件,而不必处理指数级爆增的功能状态和状态转换的多重性。

49.为了更容易开发和应用测试模式,将某些可测试性特征添加到电路设计中,该电路设计被称为用于测试的设计或用于可测试性(dft)的设计。扫描测试是最常见的dft方法。在基本的扫描测试方案中,所有或大部分内部顺序状态元件(锁存器、触发器等)通过串行接口在电路设计中是可控制的和可观察的。这些功能性状态元件经常由被称为扫描单元的两用状态元件代替。扫描单元连接在一起以形成扫描链-串行移位寄存器,用于移入测试模式和移出测试响应。扫描单元可以操作为原始意图以用于功能性目的(功能性/任务模式)并且操作为用于扫描(扫描模式)的扫描链中的单元。一种广泛使用类型的扫描单元包括边沿触发的触发器,带有用于数据输入的双向多路复用器。该双向多路复用器通常由被称为scan_enable的单控制信号进行控制,该控制信号从扫描信号输入端口或系统信号输入端口选择用于扫描单元的输入信号。该扫描信号输入端口通常连接到另一扫描单元的输出端,而系统信号输入端口连接到功能性逻辑。扫描单元可以用作控制点和观察点。该控制点可用于在被测试电路的某些位置处设置某些逻辑值,以激励(激活)故障并将错误值传播到观测点。扫描测试允许测试设备访问通过主输入端/输出端和/或某些物理测试点深度嵌入的门,并且可以在试图控制或观察在某些内部电路元件处发生的情况时,消除对复杂状态转换序列的需要。

50.用于扫描测试的测试模式通常通过自动测试模式生成(automatic test pattern generation,atpg)过程来生成。atpg经常聚焦于从门级故障模型导出的一组故组。缺陷是在制造过程中在装置中引起的缺陷或物理瑕疵。故障模型(或简言之故障)是对缺陷如何改变设计行为的描述。对于给定的目标故障,atpg包括两个阶段:故障激活和故障传播。故障激活在故障部位建立一个与故障产生的信号值相反的信号值。故障传播通过将从故障部位到扫描单元或主输出端的路径敏感化来向前传播故障效应。如果由扫描单元或主输出端捕获的测试响应值不同于期望值,则部位处的故障被称作由测试模式检测的。atpg的目的是找到这样一种测试模式:当被施加到电路时,使测试器能够区分正确的电路行为和由一个或多个特定故障引起的故障电路行为。atpg的有效性是通过针对故障模型实现的故障覆盖率和所生成的向量的数量(测试模式计数,其应当与测试应用时间成正比)来测量的。这里,故障覆盖率被定义为检测到的故障数与故障总数的比率。

51.在实践中使用的最流行的故障模型是单固定型(single stuck-at)故障模型。在该模型中,假定电路中的信号线中的一者被固定在固定逻辑值,而不考虑提供给电路的输入。该固定型故障模型是逻辑故障模型,因为没有延迟信息与故障定义相关联。延迟故障引起基于其时序的电路运行中的错误。它们是由门中的信号的有限的上升和下降时间周期以

trans.cad)》的第23卷第776页至792页)中找到,以及在美国专利号6,327,687;6,353,842;6,539,409;6,543,020;6,557,129;6,684,358;6,708,192;6,829,740;6,874,109;7,093,175;7,111,209;7,260,591;7,263,641;7,478,296;7,493,540;7,500,163;7,506,232;7,509,546;7,523,372;7,653,851中找到,这些文献的全部内容通过引用并入本文。

56.逻辑内建自测试(逻辑bist)是这样的dft技术,其允许电路使用嵌入式测试逻辑来测试自身,而无需外部测试器。经典的逻辑bist应用包括在老化测试期间检测早期失效性缺陷,使得能够使用仅提供功率和时钟信号的低成本和/或低速测试器,以及使用系统内自测试,来提高系统在航空/国防、车辆、电信和医疗保健行业中的可靠性。典型的逻辑bist系统包括用于自动生成测试模式的测试模式发生器、用于将测试响应压缩成特征的测试响应分析器(压缩器)以及用于协调bist操作并用于提供通过/失败指示的逻辑bist控制器。伪随机模式发生器(pseudo-random pattern generator,prpg)(即通常使用的测试模式发生器)可以根据线性反馈移位寄存器(linear feedback shift register,lfsr)或单元化自动机来构建。为了提高故障覆盖率,可以采用加权的lfsr。另一种方法是以某些方式将随机测试模式与确定性模式组合,因为bist逻辑可用于处理确定性生成的并存储在芯片中的压缩测试模式。

57.所有上述过程、用于测试的设计插入、测试模式生成和逻辑诊断是通常由各种电子设计自动化工具来执行的,所述电子设计自动化工具例如是可从俄勒冈州威尔逊维尔的明导公司(mentor graphics corporation)获得的tessent系列的软件工具中的那些工具。

58.通过低成本、精细粒度扫描选择进行x-掩蔽

59.图2例示了根据所公开技术的各个实施例的测试响应压缩系统200的示例。系统200包括扫描链210、测试响应压缩器230、和扫描门控装置220。包括扫描单元的扫描链210被配置成测试模式以移入测试模式、将测试模式应用到电路、捕获电路的测试响应、以及移出测试响应。测试响应压缩器230被配置以压缩测试响应。测试响应压缩器230可以是诸如多输入特征寄存器(misr)的时间压缩器、诸如xor(异或)门网络的组合式压缩器、或这两者的组合。扫描门控装置220(也称为扫描选通器)被插置在扫描链210的输出端与测试响应压缩器230的输入端之间。扫描门控装置220将扫描链210划分成扫描链组。这些扫描链组可以具有相等或几乎相等的大小。每个扫描门控装置220从扫描链组中的一者的输出端接收信号,并且基于第一信号221以启用模式或禁用模式进行操作。在所公开技术的一些实施方式中,只有扫描门控装置220中的一者以启用模式进行操作。在所公开的技术的一些其它实施方式中,扫描门控装置220中的多于一者可以以启用模式进行操作。以启用模式操作的扫描门控装置基于第二信号(图2中的222)阻断、仅在一个或更多个时钟周期处阻断、或不阻断由扫描链组中的扫描链捕获的并从该扫描链输出的测试模式的测试响应的一部分到达压缩器,其中,所述扫描链组中的所述扫描链耦合到所述以启用模式操作的扫描门控装置。以禁用模式操作的扫描门控装置可以被配置以不阻断由扫描链组的每组中的所有扫描链捕获的并从该扫描链输出的测试模式的测试响应的一部分到达测试响应压缩器,其中,所述扫描链组的每组中的所有扫描链耦合到所述以禁用模式操作的扫描门控装置。第三信号223可以与第一信号221结合使用,以允许禁用的扫描门控装置阻断或不阻断测试响应,如下面将详细描述的。

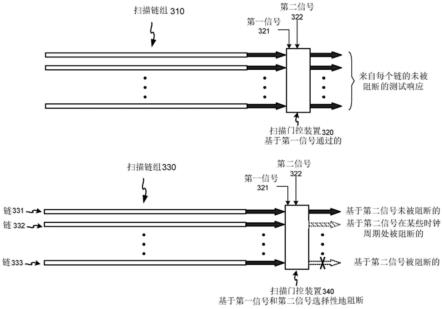

60.图3示出了由第一信号321启用的扫描门控装置340。基于第二信号322,扫描门控

装置340使由扫描链331捕获的测试响应通过,阻断由扫描链333捕获的测试响应,仅在某些时钟周期处阻断由扫描链332捕获的测试响应。因此,耦合到启用的扫描门控装置340的扫描链组330中的扫描链可被划分为三类:被阻断的、被周期选择性阻断的、和不被阻断的。

61.还在图3中示出的是由第一信号321禁用的扫描门控装置320。由耦合到扫描门控装置320的扫描链组310中的每个扫描链捕获的测试响应被允许通过该扫描门控装置320。第三信号可用于允许禁用的扫描门控装置阻断或不阻断由相关联的扫描链组捕获的测试响应。图4a例示了由第一信号421禁用的扫描门控装置410的示例,该扫描门控装置410基于第三信号423允许由扫描链组420中的扫描链捕获的测试响应通过。图4b例示了由第一信号421禁用的相同的扫描门控装置410的示例,该扫描门控装置410基于第三信号423阻断由扫描链组420中的扫描链捕获的测试响应通过。这种布置可以使仅一组中的扫描链对测试响应压缩器进行馈送,而剩余的扫描链被阻断。这种功能允许对扫描链的非常积极的掩蔽,包括仅观察到单一链的情形。

62.作为第一信号、第二信号和第三信号(图2中的221-223,图3中的321-322)可以随测试模式而变化,可以将不同的扫描门控装置选择为启用的/禁用的,并且可以针对不同的测试模式来阻断或部分阻断与启用的扫描门控装置相关联的扫描链组中的不同的扫描链。这使得能够在可重新限定的扫描链组和指定的扫描移位周期内掩蔽x状态。

63.应当注意,耦合到启用的扫描门控装置的扫描链组中的扫描链不需要总是被划分为三个类别。它们可以被划分为两个类别(例如,周期选择性阻断的+阻断的),或者基于第二信号在一些情况下全部属于一个类别(例如,周期选择性阻断的)。

64.图5例示了根据所公开技术的各个实施例的具有提供控制信号(第一信号、第二信号和第三信号)的电路的扫描门控装置500的框图的示例。扫描门控装置500具有多个子单元。子单元的数量等于耦合到扫描门控装置500的扫描链组530中的扫描链的数量。每个子单元包括与门510和多路复用器520。与门510的一个输入端耦合到扫描链组530中的扫描链的输出端。与门510的其他输入端耦合到多路复用器520的输出端。由寄存器的触发器580提供的用于启用/禁用扫描门控装置500的第一信号540耦合到多路复用器520的选择输入端。多路复用器520的两个输入端分别耦合到第二信号560和第三信号550。第二信号560由选择器570生成,并且具有用于扫描链组530中的不同扫描链的不同的信号线。当第一信号540生效(“1”)时,扫描门控装置500被启用,并且扫描链组530中的每个扫描链的输出由第二信号560的信号线中的一者控制。扫描链的输出可以根据特定信号线被阻断、不被阻断、在选择性时钟周期被阻断。当第一信号540未被生效(“0”)时,扫描门控装置500被禁用,并且扫描链组530中的所有扫描链由第三信号550控制。根据第三信号550是未生效的还是生效的,所有扫描链的输出被阻断或不被阻断。

65.包括触发器540的寄存器(也称为配置寄存器)可以被偶尔重新加载,因为相同的内容通常可以用于成行的几个测试模式。其可以被隔离在配置插入位(configuration insertion bit,cib)610后面,如图6所示。配置插入位610被部署成允许对配置寄存器620按需访问,并使相同的寄存器与单个ate输入通道交互。如果触发器630输出0,则将cbi 610设置成旁通配置寄存器620,并且仅允许以菊花链形式与其连接的其它寄存器被更新。在该模式中,由于时钟门控640,配置寄存器620不受任何数据传输的影响。一旦生效,触发器630将附加测试数据路由到配置寄存器,同时启用时钟信号,以促进配置寄存器的移位寄存器

功能。然后建立从ate输入通道经过一些寄存器(如果有的话)到配置寄存器,然后经过一些其它寄存器(如果有的话)回到解压缩器的移位路径。触发器630的状态中的所有变化通过允许捕获输入序列的第一控制位的cib启用输入来完成。该位指示以下序列是用于更新x-掩蔽逻辑配置,还是仅仅是另一寄存器的新内容。

66.图7例示了根据所公开技术的各个实施例的具有提供控制信号(第一信号、第二信号和第三信号)的电路的扫描门控装置700的框图的另一示例。类似于图5中的扫描门控装置500,扫描门控装置700具有多个子单元,每个子单元包括与门703和多路复用器705。同样类似于图5中的扫描门控装置500,第三信号790耦合到多路复用器705的选择输入端,由选择器730生成的第二信号760耦合到多路复用器705的两个输入中的一者,并且扫描链组720中的扫描链的输出耦合到与门703的输入端中的一者。图5和图7中的设置之间的差异是第一信号750不是从触发器提供的,而是从地址解码器740提供的。这里,地址解码器740本质上是这样的与门,其将地址转换器720的输出作为其输入,并将输入转换为第一信号750。用于扫描门控装置700的地址解码器740通常使用地址转换器720的输出的组合,该输出不同于用于另一扫描门控装置的地址解码器所使用的输出。

67.如果地址位a*(地址转换器720的输出组770)被视为地址位a的反相(地址转换器720的其他输出组780),则地址解码器(如地址解码器740)确保每次只能启用一个扫描门控装置。为了同时启用两个或更多个扫描门控装置,地址转换器可以使用另一信号,如图8所例示的。地址转换器800接收常规二进制编码地址a(810)并将其存储在地址寄存器830中。另外,地址转换器800接收相同量的支配位d(820),并将它们存储在支配位寄存器840处。支配位d(820)指示哪个地址位以及它们的逆相都应该用逻辑值1代替。换句话说,如果需要,支配位寄存器840的内容可以覆盖任何地址位。例如,如果在地址转换器800的输入处ai=1且di=0,则在地址转换器800的输出处ai=1且ai*=0。然而,di的有效(1)电平将在地址转换器800的输出处将位ai和ai*都设置为1。结果,只要两个扫描门控装置对仅在位i上不同(分别设置为0和1)的两个地址进行解码,这两个扫描门控装置将同时被启用。使用地址转换器800,可以通过使支配位寄存器840的相应位生效来启用各组扫描门控装置。启用的扫描门控装置的数量将等于2的幂。将所有支配位设置为1可以启用所有扫描门控装置。在这种情况下,现在取决于从选择器(例如,选择器730)输出的第二信号来决定掩蔽哪些扫描链。

68.图8所示的地址转换器800以由支配控制位820确定的粒度来促进若干扫描门控装置的同时选择。然而,不能同时启用扫描门控装置及其相关联的扫描链组的某些组合。例如,地址位a=00001和支配位d=00010允许选择扫描门控装置g1和g3,但是除非通过选择a=00000并设置两个最低有效支配位(即d=00011)使得也包括有扫描门控装置g0,否则同时启用扫描门控装置g2与g1和g3是不可能的。

69.图9例示了地址解码器ga(940)的示例,其能够克服上述缺点,并且使得扫描门控装置的选择更灵活。除了基于地址变量和它们的逆相生成唯一信号920的地址与门930之外(如图7),地址译码器ga(940)具有三个由附加控制线n

3-1

(950)驱动的二输入与门931、932和933,以及来自三个地址译码器的地址与门的输出,所述三个地址译码器耦合到三个之前的扫描门控装置g

a-1

、g

a-2

和g

a-3

(假定扫描门控装置是串联连接的)。因此,只要相应的控制线n1是生效的,则启用g

a-1

也可以选择ga。类似地,如果线n2或线n3分别被设置为1,则选择ga-2

或g

a-3

可以启用ga。

70.图8所示的地址转换器800可以以线n3n2n1只能假定为以下组合之一的方式而被重新设计:000,001,011或111。图10例示了这种地址解码器1000的示例。这里,两个附加控制线1010用于产生信号n3、n2和n1。因此,如果线n允许,则给定的扫描门控装置gk可以与g

k+1

、或g

k+1

和g

k+2

、或g

k+1

、g

k+2

和g

k+3

并行地启用。

71.例如,为了启用g0、g1和g2,可以选择g0,然后将用于启用相邻扫描门控装置的两个控制线1010设置为值10。这最终产生启用g1和g2两者的控制信号n3n2n1=011。地址解码器的详细架构如图11所例示,该地址解码器包括用于从g3到g9的扫描门控装置的地址解码逻辑(可以以类似的方式设计该图中未示出的解码器的其余部分)。可以看出,主地址解码与门驱动位于随后的三个扫描门控装置中的对应的二输入与门(由相同的符号表示)。所公开技术可以以附加二输入与门和控制数据的代价在其相邻模块阻断方面容易地覆盖给定扫描门控装置的任何邻域。

72.图12例示了根据所公开技术的各个实施例的被配置以生成第二信号的选择器的示例。第二信号确定耦合到启用的扫描门控装置的扫描链组中的哪些扫描链应该被掩蔽。图12所例示的选择器架构假设每组由八条扫描链组成。有两组选择器输入。除非配置寄存器b-off(1220)和b-on(1230)的内容决定其他内容,否则表示为s*(1210)的输入用于在每个周期模式中单独地门控相应的扫描链。凭借阻断输入b(这里是16个输入)(1240)通常以每个模式或模式组将这些寄存器重新加载一次。可以看出,每个扫描链分配有配置控制位对,该配置控制位对确定该扫描链的掩蔽状态,如下所示。如果寄存器1220和寄存器1230的位bk都被设置为0,则扫描链k在整个扫描卸载期间(选择器输出k被设置为0)是被无条件阻断的。使寄存器b-on(1230)的位bk生效使得扫描链k是完全可观测的。最后,根据输入s*k的当前状态的需要,将b-on(1230)的位bk设置为0,并将b-off(1220)的对应位设置为1,以允许掩蔽扫描链k。在图12中的表1250中概述了上述内容。

73.图13例示了根据所公开技术的各个实施例的测试压缩逻辑的示例,该测试压缩逻辑采用配置寄存器来向扫描门控装置提供第一信号。扫描门控装置1310位于扫描链输出端与测试响应压缩器1320之间,并将扫描链划分成大小几乎相等的扫描链组1350。基于控制信号(第一信号、第二信号和第三信号),在测试结果可能进入测试响应压缩器1320之前,扫描门控装置1310选择性地阻断离开每个组内的链的测试结果。第一信号是由配置寄存器1330提供的。类似于图6中所示的配置插入位装置1380控制是否加载/更新配置寄存器1330。第二信号是由选择器1340提供的。类似于图12中所示的选择器1340基于由b寄存器1390提供的b-on信号和b-off信号以及来自测试数据解压缩器1360的选择信号来产生第二信号。第三信号是由两个辅助缓冲器1373和1375提供的。其中一个辅助缓冲器1375用作影子寄存器,其允许保存该特定控制,同时与下一测试模式的移入并行地重新加载其新值。类似的缓冲技术可适用于选择数据。用于选择器1340的影子寄存器可以是如图12所示的选择器的一部分。主输入寄存器1373、1380和1390是菊花链式的,使得可以凭借用于向解压缩器1360传递数据的常规ate通道来更新主输入寄存器1373、1380和1390。

74.图14例示了根据所公开技术的各个实施例的测试压缩逻辑的示例,该测试压缩逻辑采用地址转换器来向扫描门控装置提供第一信号。除了两个差异,图14所示的测试压缩逻辑与图13所示的测试压缩逻辑类似。第一个差异是图14中所示的测试压缩逻辑采用地址

转换器1420以及一系列地址解码器(未示出),而不是配置寄存器,以向扫描门控装置1410提供第一信号。地址转换器1420类似于图8中所示的地址转换器,其基于由地址寄存器1440提供的地址位和由支配位寄存器1430提供的支配位来产生地址输出位。同样,包括1430和1440的主输入寄存器是菊花链式的,使得可以凭借用于向解压缩器传递数据的常规ate通道来更新包括1430和1440的主输入寄存器。应当注意的是,也可以使用其它类型的地址转换器,例如图10中所示的地址转换器。

75.图13与图14之间的第二个差异是图14中的测试压缩逻辑具有比较装置1450和粘贴位装置1460。可以使用所公开的技术而不是扫描输出的测试结果并通过外部测试器对测试结果进行处理,来容易地执行实际测试响应与预期测试响应的片上比较。因此,可以用图14中所示的比较装置1450来代替输出ate通道。这里,将参考数据的附加流r与离开测试响应压缩器的输出流进行比较(被异或),并且如果检测到任何差异,则通过粘贴位装置1460锁存为值1。

76.图15例示了利用所公开技术实施的逻辑bist方案的示例。由于扫描链1510是由伪随机模式发生器(pseudorandom pattern generator,prpg)1520生成的伪随机模式馈送的,所以选择器1540不能从测试模式(如图14中的测试模式)的源接收其每周期数据。因此,除了包括地址(a)、支配(d)、阻断(b)和e寄存器的内容的数据之外,还通过用于播种prpg1520的相同输入来提供小型解压缩器1530的种子(s),该小型解压缩器153以在每周期模式产生实际选择器输入。本示例中的压缩器包括组合逻辑(例如,异或网络)1560和misr1550。

77.图16例示了小型解压缩器1530的架构的示例。除了铃流发生器1610和驱动选择器输入的移相器1630之外,在这两个装置之间还设置保持寄存器1620。该保持寄存器1620捕获铃流发生器1610的某些状态,同时发生器1610继续进行到解码另一组选择位所需的下一状态。结果,可以针对多个连续的扫描移位周期,重复给定的小型解压缩器状态并将其传递给选择器1540。小型解压缩器1530还容纳小型环形模板寄存器1640,该小型环形模板寄存器1640在每个扫描移位周期向保持寄存器提供控制位,以指示是否应该用铃流发生器1610的当前内容来重新加载该寄存器。由于非常相同的短模板的大小,在相同测试模式的持续时间内通常多次使用所述非常相同的短模板。

78.小型解压缩器1530能够利用附加的重新加载点(所述附加的重新加载点在模板寄存器1640中出现为1秒)对选择模式(多维立方体)进行解码,并且指示关于何时更新保持寄存器的适当时间。值得注意的是,与基于edt的压缩类似,选择解算器假定相同等式与由给定保持时段覆盖的所有选择位相关联。结果,如果在时段内存在至少一个指定位,则该时段的第一选择位成为编码的对象。如实验结果所示,(平均)高达50%的指定位通常由保持时段的恒定值来处理而不是由直接编码来处理,从而确保高的编码效率。

79.结论

80.在例示和描述了所公开的技术的原理之后,对于本领域技术人员明了的是,可以在不背离这些原理的情况下在布置和细节上对所公开的实施例进行修改。鉴于可以应用所公开的技术的原理的许多可能的实施例,应当认识到所例示的实施例仅仅是所述技术的优选的示例,并且不应当将其视为对所公开的技术的范围的限制。相反,所公开的技术的范围由所附权利要求及其等同物来限定。因此,我们将所有落入这些权利要求的范围和精神内

的技术作为我们公开的技术。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1