一种高速串行信号丢失检测电路的制作方法

[0001]

本发明属于集成电路设计领域,特别涉及一种高速串行信号丢失检测电路。

背景技术:

[0002]

高速串行信号具有其特殊性,正常信号电压幅度较宽,可以从50mv到1600mv的范围,当正常信号丢失(loss of signal,简称los)时,输入信号线可能与其他电压平面短路,则会导致正常信号内存在直流电平,也可能存在较大的噪声。输入正常信号时包含的直流电平可能与正常信号较强的电压幅度相当,噪声可能与正常信号较弱时的电压幅度相当,直接用电平比较的方法会造成误判。当正常信号较弱时,管脚输入信号的电压幅度极低,不能直接使用数字电路进行处理,因此难以得到准确的los告警输出。

[0003]

图1是传统的信号丢失检测电路,如图1所示,峰值检测电路检测出输入电平峰值,峰值与参考的阈值电平比较,比较结果延时后得出alos信号。当peakh-peakl<refp-refn时,比较器输出为低,信号传输至延时电路后输出alos信号。由于峰值检测电路的特点是跟踪快,衰减慢。因此,当接收信号突然丢失,峰值检测电路的输出需要经过一段时间之后才能衰减到报警电平以下,致使电路不能实时的检测输入信号,以输出正确的alos信号,延迟了报警时间。

[0004]

本发明的高速串行信号丢失检测电路与传统的信号丢失检测电路相比,去掉了峰值检测电路,增加了翻转率计数和比较器电路,由于采用了电压幅度比较器和翻转率计数和比较器的双重判断,避免了单独使用电压幅度比较器时对输入信号短路到高电平的丢失状态误判为正常的情况出现;同时,本发明的检测电路能够直接处理低幅度的正常信号,所包含的电路模块在高频率信号输入时均可工作,检测结果输出延迟极小,可以满足各种通信协议的低延时报警要求。

技术实现要素:

[0005]

有鉴于此,本发明的主要目的是提供一种高速串行信号丢失检测电路,实现了对高速串行信号实时和精确检测。

[0006]

本发明提供了一种高速串行信号丢失检测电路,如图2所示,其包括电压幅度比较器、翻转率计数和比较器;其中,电压幅度比较器用于对输入的差分信号rx

p

和rx

n

与电压阈值v

th

比较,当输入rx

p

或者输入rx

n

电压幅值低于电压阈值v

th

时,电压幅度比较器输出为低电平,逻辑“0”;当输入rx

p

或者输入rx

n

电压幅值高于电压阈值v

th

时,电压幅度比较输出为高电平,逻辑“1”,电压幅度比较器可以由2个单端比较器或1个差分比较器构成。

[0007]

翻转率计数和比较器对电压幅度比较器输出的“0”“1”跳变上升沿变化(简称翻转)进行计数,将计数结果与翻转率阈值d

th

进行比较。例如,在1000个时间单位内,电压幅度比较器输出的翻转数量小于设定的翻转率阈值d

th

数量,则认为输入rx

p

或者输入rx

n

没有正常信号,los状态输出为1,表示信号丢失,呈los状态;如果电压幅度比较器输出的翻转数量大于等于设定的翻转率阈值d

th

数量,则认为输入rx

p

或者输入rx

n

信号正常,los状态输出为

0,表示信号正常,无los。

[0008]

发明的有益效果:由于采用了电压幅度比较器和翻转率计数和比较器的双重判断,避免了单独使用电压幅度比较器时对输入信号短路到高电平的丢失状态误判为正常的情况出现;同时,由于低幅度的正常信号不能直接驱动数字逻辑电路的翻转,本发明的检测电路避免了单独使用信号翻转率计数和比较器而不能直接处理低幅度的正常信号的情况;本发明的所有电路模块均可以工作在高频率情况,检测结果输出延迟极小,可以满足各种通信协议的低延时报警要求。

附图说明

[0009]

图1是传统的信号丢失检测电路结构图;

[0010]

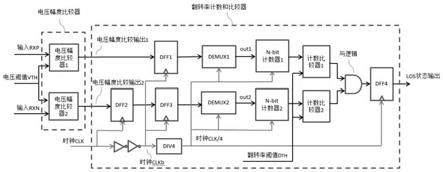

图2是本发明的高速串行信号丢失检测电路结构示意图;

[0011]

图3是本发明的高速串行信号丢失检测电路原理图;

具体实施方式

[0012]

下面结合附图对本发明的一种高速串行信号丢失检测电路进行详细的说明。

[0013]

图3是本发明的高速串行信号丢失检测电路原理图,如图3所示,其包括电压幅度比较器和翻转率计数和比较器;其中,所述电压幅度比较器由电压幅度比较器1和电压幅度比较器2组成,所述翻转率计数和比较器包括1到d型触发器dff1、1到d型触发器dff2、1到d型触发器dff3、1到d型触发器dff4、时钟分频器div4、解复用器demux1和demux2、n-bit计数器1、n-bit计数器2、计数比较器1、计数比较器2、与门。

[0014]

输入rxp和输入rxn为待检测信号,电压阈值vth通过寄存器设置不同的阈值,电压幅度比较输出1信号和电压幅度比较输出2信号分别对应输入rxp和输入rxn与电压阈值vth的比较结果,电压幅度比较器1输出信号至1到d型触发器dff1的数据端d端;电压幅度比较器2输出信号至1到d型触发器dff2的数据端d端,1到d型触发器dff2输出信号至1到d型触发器dff3,时钟clk延迟后的时钟clkb作为dff1和dff3的时钟脚,对电压幅度比较输出1和输出2进行上升沿采样,dff1的采样结果输出至demux1,dff3的采样结果输出至demux2;demux1和demux2为解复用器,由于输入rxp和输入rxn是高速信号,不适合直接使用复杂的数字逻辑处理,经过demux 1和demux2解复用器处理之后,后级电路只需工作在输入rxp和输入rxn四分之一的速率即可,降低了后级数字电路的设计难度,解复用器demux1也可以根据分频需求采用合适的解复用比率,例如1:4、1:8、1:16等,时钟分频器div4对延迟后的时钟clkb进行分频,设置为与解复用器相同的分频比。

[0015]

解复用器demux1和解复用器demux2分别输出out1信号和out2信号至n-bit计数器1和n-bit计数器2,n-bit计数器1和n-bit计数器2对解复用器demux1的输出out1信号和解复用器demux2的输出out2信号的上升沿进行计数,计数器计满后,清0重新开始计数。

[0016]

n-bit计数器1和n-bit计数器2分别输出计数结果至计数比较器1和计数比较器2,并与翻转率阈值dth进行比较,如果n-bit计数器的计数值小于翻转率阈值dth,则输出高电平即逻辑“1”;如果n-bit计数器的计数值大于等于翻转率阈值dth,则输出低电平即逻辑“0”。

[0017]

计数比较器1和计数比较器2输出比较结果至逻辑与门,进行逻辑“与”运算,与门

输出逻辑运算结果至d型触发器dff4,dff4对与门的输出信号进行整形,dff4的输出即为los状态输出。当计数比较器1和计数比较器2的输出结果都为逻辑“1”时,与门输出逻辑“1”,即正常信号丢失los状态;当计数比较器1和计数比较器2的输出结果不都为逻辑“1”时,与门输出为逻辑“0”,即信号正常。计数比较器1和计数比较器2输出均为逻辑“1”时,才判定为正常信号丢失状态,因为电路工作时存在输入rxp或者输入rxn只有其中之一丢失的情况,但此时芯片内部通常可以正常处理并继续工作。

[0018]

作为本发明的另一并列技术方案,将逻辑与门替换为或门,输入rxp或者输入rxn其中之一异常,或者两者都异常时,los状态输出都会显示正常信号丢失,判决条件更加严苛,电路工作原理与使用逻辑与门相同。

[0019]

以上仅为发明的优选实施例而已,并不用以限制本发明,凡在本发明的思想原则内所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1