一种桥梁拉索断丝声信号采集系统及方法与流程

[0001]

本发明涉及桥梁拉索技术领域,特别是涉及一种桥梁拉索断丝声信号采集系统及方法。

背景技术:

[0002]

本部分的陈述仅仅是提供了与本发明相关的背景技术信息,不必然构成在先技术。

[0003]

拉索是斜拉桥、系杆拱桥、悬索桥等拉索体系桥梁的关键受力构件,拉索由于受到环境腐蚀和老化作用,会发生锈蚀、断丝、断裂等损伤,所以需要对桥梁拉索进行安全检测。

[0004]

对桥梁拉索的断丝信号进行采集,通过对断丝声信号的分析实现桥梁拉索断丝的健康监测,目前采集桥梁拉索断丝声信号的系统主要分为通用型声发射采集系统和专用型声发射采集系统,通用型声发射系统应用范围广,功能齐全,但是成本较高,且需要对系统中参数进行修正后才能达到使用标准;专用型声发射采集系统是专用于某种特定的材料或者某种特定的领域,要根据测试领域产生声发射信号的特点进行专用设计,无法实现声信号采集的兼容性与通用性。

技术实现要素:

[0005]

为了解决上述问题,本发明提出了一种桥梁拉索断丝声信号采集系统及方法,对初始断丝声信号经放大和滤波处理后,经fifo存储器将数字断丝声信号通过千兆以太网发送至上位机,且在传输过程中采用循环冗余校验码进行校验,保证以太网传输通道的可靠性以及保证断丝声信号的完整、准确。

[0006]

为了实现上述目的,本发明采用如下技术方案:

[0007]

第一方面,本发明提供一种桥梁拉索断丝声信号采集系统,包括:采样模块、处理模块和校验模块;

[0008]

所述采样模块包括对接收的初始断丝声信号采用放大电路和滤波电路进行放大处理和滤波处理后,经模数转换电路得到的数字断丝声信号发送至处理模块;

[0009]

所述处理模块包括对数字断丝声信号采用fifo存储器进行存储,经fifo存储器将数字断丝声信号通过千兆以太网模块发送至上位机;

[0010]

所述校验模块包括采用循环冗余校验码对千兆以太网模块传输数字断丝声信号时进行校验。

[0011]

第二方面,本发明提供一种桥梁拉索断丝声信号采集方法,包括:

[0012]

对接收的初始断丝声信号采用放大电路和滤波电路进行放大处理和滤波处理后,经模数转换电路得到的数字断丝声信号;

[0013]

对数字断丝声信号采用fifo存储器进行存储,经fifo存储器将数字断丝声信号通过千兆以太网模块发送至上位机;

[0014]

采用循环冗余校验码对千兆以太网模块传输数字断丝声信号时进行校验。

[0015]

与现有技术相比,本发明的有益效果为:

[0016]

本发明对断丝声信号进行前期调理处理,通过放大和滤波,将断丝声信号进行15倍放大,达到adc输入采集范围;通过低通滤波器,且截止频率为700khz,滤波频率较大的噪声信号,避免噪声的干扰。

[0017]

本发明对断丝声信号的采样精度高,采样频率大,使用千兆以太网传输,传输稳定且传输速率快;在使用千兆以太网传输断丝声信号时,采用循环冗余校验码crc校验传输过程中的所可能发生的数据丢失或数据错误,crc校验误码率低,保证以太网传输通道的可靠性。

[0018]

本发明采用pcb布局,以fpga为核心元件,断丝声信号经过传感器流通到前端调理电路,然后流向adc,经过模数转换流通到fpga中,在电源和芯片周围放置去耦电容和滤波电容,提高了抗干扰能力;且通过零欧电阻或者磁珠隔离模式部分和数据部分,减少互相的干扰。

附图说明

[0019]

构成本发明的一部分的说明书附图用来提供对本发明的进一步理解,本发明的示意性实施例及其说明用于解释本发明,并不构成对本发明的不当限定。

[0020]

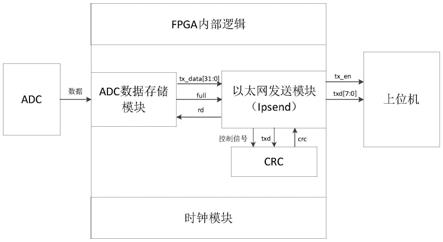

图1为本发明实施例1提供的桥梁拉索断丝声信号采集系统结构图;

[0021]

图2为本发明实施例1提供的放大电路原理图;

[0022]

图3为本发明实施例1提供的放大仿真结果示意图;

[0023]

图4为本发明实施例1提供的低通滤波器原理图;

[0024]

图5为本发明实施例1提供的低通滤波器仿真结果示意图;

[0025]

图6为本发明实施例1提供的adc硬件电路原理图;

[0026]

图7为本发明实施例1提供的adc与fpga引脚连接原理图;

[0027]

图8(a)-8(b)为本发明实施例1提供的ads1675时序图;

[0028]

图9为本发明实施例1提供的ads1675编程架构原理图;

[0029]

图10为本发明实施例1提供的fpga主动并行模式配置示意图;

[0030]

图11为本发明实施例1提供的fifo配置示意图;

[0031]

图12为本发明实施例1提供的phy芯片与fpga和网络变压器连接图;

[0032]

图13为本发明实施例1提供的rtl8211eg硬件电路原理图;

[0033]

图14为本发明实施例1提供的ipsend发送模块状态机示意图;

[0034]

图15为本发明实施例1提供的pcb布局示意图;

[0035]

图16为本发明实施例1提供的电源设计转换关系示意图;

[0036]

图17为本发明实施例1提供的信号源发送100khz信号采集结果示意图;

[0037]

图18为本发明实施例1提供的以太网传输验证数据处理结果示意图;

[0038]

图19(a)-19(b)为本发明实施例1提供的实验验证结果示意图。

[0039]

图19(c)为本发明实施例1中图19(a)的断铅信号波形局部放大示意图。

[0040]

图19(d)为本发明实施例1中采用m2p.59xx-x4系统得到的波形信号示意图。

具体实施方式:

[0041]

下面结合附图与实施例对本发明做进一步说明。

[0042]

应该指出,以下详细说明都是例示性的,旨在对本发明提供进一步的说明。除非另有指明,本文使用的所有技术和科学术语具有与本发明所属技术领域的普通技术人员通常理解的相同含义。

[0043]

需要注意的是,这里所使用的术语仅是为了描述具体实施方式,而非意图限制根据本发明的示例性实施方式。如在这里所使用的,除非上下文另外明确指出,否则单数形式也意图包括复数形式,此外,还应当理解的是,术语“包括”和“具有”以及他们的任何变形,意图在于覆盖不排他的包含,例如,包含了一系列步骤或单元的过程、方法、系统、产品或设备不必限于清楚地列出的那些步骤或单元,而是可包括没有清楚地列出的或对于这些过程、方法、产品或设备固有的其它步骤或单元。

[0044]

在不冲突的情况下,本发明中的实施例及实施例中的特征可以相互组合。

[0045]

实施例1

[0046]

如图1所示,本实施例提供一种桥梁拉索断丝声信号采集系统,包括采样模块、处理模块和校验模块;

[0047]

所述采样模块包括对接收的初始断丝声信号采用放大电路和滤波电路进行放大处理和滤波处理后,经模数转换电路得到的数字断丝声信号发送至处理模块;

[0048]

所述处理模块包括对数字断丝声信号采用fifo存储器进行存储,经fifo存储器将数字断丝声信号通过千兆以太网模块发送至上位机;

[0049]

所述校验模块包括,采用循环冗余校验码对千兆以太网模块传输数字断丝声信号时的校验。

[0050]

所述采样模块包括传感器、放大电路、滤波电路和adc模数转换电路;

[0051]

在本实施例中,初始断丝声信号由谐振传感器采集,谐振传感器位于声源处;由于桥梁拉索断丝信号微弱且频率范围在43khz~500khz,而谐振式传感器在中心频率下对信号较为灵敏并且频率响应范围较窄;所以,本实施例选取中心频率分别是40khz、150khz、500khz 的sr40m窄带传感器、sr150m中频带传感器和wg500宽频传感器,确保采集到有效的声信号。

[0052]

由于桥梁拉索断丝声信号在100mv以内,而模数转换器adc输入电压范围为-3v~+3v,故本实施例采用放大电路对声信号进行放大处理,实现15倍放大,以达到adc输入采集范围;

[0053]

本实施例采用亚德诺(adi)公司的低噪声放大器ada4896-2,ada4896-2单位增益稳定、低噪声、轨对轨输出、无杂散动态范围为-80db,桥梁断丝声发射信号在1mhz以内,芯片的带宽230mhz能够满足需求;本实施例的放大电路如图2所示,两个运算放大器分别通过电阻r1、r2与电容并联构造负反馈,并通过电阻r3连接两个电容的负输入端,根据电路可知:

[0054][0055]

放大电路增益g为:

[0056][0057]

通过电路仿真软件multisim进行仿真,仿真结果如图3所示,当输入信号是96mv时,输出信号为1.47v,将输入信号放大了15倍。

[0058]

由于桥梁拉索断丝声信号频率范围为43khz~500khz,本实施例通过低通滤波器进行滤波处理,截止频率为700khz,避免噪声干扰;对滤波电路中放大器ths4503采用二阶巴特沃斯低通滤波器,滤波频率较大的噪声信号,低通滤波器如图4所示:

[0059]

二阶巴特沃斯低通滤波的网络传递函数为:

[0060][0061][0062]

式中,w

r

是-3db带宽角频率,δ是滤波设计系数;

[0063]

由式(3)和式(4)可得:

[0064][0065]

其中,r1=1kω,r2=1kω,c1=2nf,c2=1nf。

[0066]

在本实施例中,桥梁拉索断丝信号小于700khz,设置-3db带宽为700khz,通过multisim 仿真确定低通滤波电路中电阻电容的值,仿真结果如图5所示,可知仿真结果的-3db带宽为 700khz。

[0067]

所述adc模数转换电路中,选取24位分辨率、4msps采样率的ads1675作为数据采集芯片,信号经过放大滤波之后输入到ads1675中,经过adc模数转换之后输出到fpga中, adc硬件电路如图6所示。

[0068]

ads1675需要提供5v的模拟供电电压和3v的数字供电电压,功率为575mw、双极性

±

3v输入电压范围,该器件在工业温度范围内具有完整的规格,并采用tqfp-64封装; ads1675通过i/o引脚控制,内部没有要编程的寄存器;start引脚可直接控制转换,控制 start引脚以开始模数转换,数据通过dout引脚差分输出;不使用时,pdwn引脚可用于关闭所有器件电路的电源;与fpga相连的管脚如图7所示,引脚的具体功能如表1所示:

[0069]

表1 ads1675引脚功能

[0070]

[0071]

ads1675通过start引脚控制采样的开始以及结束,其时序如图8(a)-8(b)所示, vhdl语言编写分为两个进程,ads1675上电之后默认低速模式,在clk时钟进程中负责由低速转到高速的配置,当sclk时钟倍频到clk时钟三倍时,start电平变高且出现 drdy脉冲,说明已经配置到高速采集模式,转到sclk进程;在sclk时钟进程中负责数据采集,在sclk进程中只需要给start引脚一个正脉冲即可启动a/d转换。在drdy信号上升沿,模拟信号开始采样,此时dout开始串行发出数据。

[0072]

编程架构如图9所示,adc配置过程如下所示。

[0073]

init:初始化状态;pdwn=1进行上电,drate[2:0]=010配置成采样频率500khz, fpata=0设置成宽频滤波器,进行延时,如果到达延时时间,进行低速配置lowspeed状态。

[0074]

lowspeed:低速模式采集状态;经过init状态配置后start进行跳变以锁存住配置,判断decide_1状态。

[0075]

decide_1:判断低速模式是否配置成功状态;如果出现drdy脉冲,说明配置成功,低速模式sclk时钟速率等于clk速率,经过pdwn=1进行上电,drate[2:0]=101配置成采样频率4mhz,fpath=0设置成宽频滤波器,进行延时,如果到达延时时间,进行高速配置 highspeed状态。

[0076]

highspeed:高速模式采集状态;再次经过start进行跳变以锁存住配置,判断decide_2 状态。

[0077]

decide_2:判断高速模式是否配置成功状态;如果出现drdy脉冲,高速模式sclk时钟速率是clk速率的三倍,说明配置成功,进入data状态。

[0078]

data:数据采集状态;将start一直置1,根据sclk脉冲进行24位数据输出。

[0079]

所述处理模块采用fpga处理模块,利用fpga的主从配置模式,在本实施例中采用双通道同步adc+fpga+千兆以太网的处理方式,选取spartan-6系列xc6slx150作为核心控制芯片,根据香农采样定理,采样频率大于采集信号频率的2倍,即选取24位分辨率、4msps 采样率的ads1675作为数据采集芯片;为了实现声信号数据全部输出到上位机,实现高速通信,本实施例采取千兆以太网传输模式。

[0080]

所述spartan-6系列芯片的配置通过ise软件生成的程序数据以比特流的形式加载进入到 fpga内部存储器,spartan-6fpga有专用于配置的引脚,引脚功能如表2所示;xc6slx150 可以主动的从外部非易失性存储器加载数据进行配置,也可以被动的由外部微处理等加载数据进行配置,本实施例通过xilinx公司专用芯片xcf32pvog48主动配置fpga, xcf32pvog48是xc6slx150专用配置芯片。

[0081]

表2 fpga配置引脚具体功能

[0082][0083]

m[1:0]引脚的状态决定fpga的配置方式,japg配置模式下,m[1:0]引脚的xx状态表明只要fpga上电,即可以使用japg模式,易于对板卡的软件代码调试,其配置方式如表 3所示。

[0084]

表3配置方式

[0085][0086]

本实施例采用主动并行模式实现fpga配置,并行数据模式下具有程序下载成功率高的特点,预留tdi、tdo、tck、tms边界扫描引脚,上电后数据从xcf32pvog48芯片加载到fpga内部sram,主动并行模式电路如图10所示。

[0087]

所述处理模块中包括adc数据存储模块,实现adc数据的存储并当数据存储满后,将数据发送到千兆以太网ipsend模块中;由于adc数据的位宽是24位,采样率是4mbps,以太网发送速度是125mhz,因此adc的数据不能直接发送给以太网,需要使用存储器进行时钟同步;

[0088]

本实施例使用fifo实现存储,fifo(first input first output)指先进先出存储器,将adc 数据按照采集顺序存储到fifo中;为了保证以太网帧有效带宽,将fifo深度设置成1024,当adc数据满后,fifo会发出full信号,指示ipsend模块开始发送以太网帧,fifo再根据此模块的读信号进行数据输出,将adc数据发送到以太网,fifo使用如图11所示,为了上位机解析数据方便,adc数据位宽是24比特,因此将adc数据在加上8比特(5a)用于表示每个adc数据,因此每个adc数据是32比特。

[0089]

本实施例adc采样精度4msps,精度24位,每秒传输数据量96mbps,双通道每秒传输数据量为192mbps,为了使数据完成传输到上位机进行信号分析,选择千兆以太网进行数据

传输;

[0090]

本实施例选用瑞昱(realtek)公司的高集成的网络接收rtl8211eg以太网phy芯片,符合10base-t,100base-tx,1000base-t的标准,能够实现10m/s、100m/s、1000m/s数据传输,可通过五类双绞线和三类双绞线传输数据,支持gmii、rgmii、mii接口;此外,采用 64脚qfn封装,具有0.5nw的功耗,支持半双工、全双工工作,支持掉电模式,通过将e_col 串联一个10k电阻并且接地,本实施例配置成gmii接口,传输时钟是125mhz;

[0091]

当需要发送以太网数据时,fpga首先把数据发送给rtl8211eg以太网phy芯片进行数据编码,通过网络变压器hr911130a,即网线接口rj-45,将数据加载到网线上,数据经由网络传递到接收方;远端通过网络发送过来的数据,经由网线加载传递给网络变压器,网络变压器的将数据输出到rtl8211eg以太网phy芯片上进行解码,得到实际的数据,然后将数据传递给fpga芯片;phy芯片与fpga和网络变压器连接如图12所示,rtl8211eg 硬件电路如图13所示,与fpga相连引脚具体功能如表4所示:

[0092]

表4 rtl8211eg引脚具体功能

[0093][0094][0095]

所述千兆以太网模块包括以太网组包发送模块(ipsend)、crc生成模块(crc)和adc数据存储模块(adc_data_memory)。

[0096]

其中,所述ipsend发送模块实现udp包的组帧和发送功能,状态机状态转换如图14所示,状态机共分为8个状态:

[0097]

idle状态:发送状态机的空闲状态;此时数据全部清空,恢复初始值。

[0098]

start状态:开始发送状态;当idle状态此时计数到以太网最小帧间隙10后,且adc数据存储模块数据满后,以太网发送状态机跳转到start状态,开始发送以太网帧。

[0099]

make状态:udp帧头计算状态;当发送状态机处于start状态后,下一个时钟进入make 状态,为了保证以太网帧的准确性,在帧头位置增加帧编号,同时要重新计算udp帧头校验码。

[0100]

send55状态:以太网发送以太网的前导码和帧导码(55_55_55_55_55_55_d5)状态,进入以太网帧发送状态,将以太网发送数据有效信号(tx_en)置1,计算以太网校验码。

[0101]

sendmac状态:发送以太网mac地址状态;当发送状态机处于send55状态,且i=7时,即前导码和帧导码发送完毕后,即进入此状态,用于发送预设的mac地址。

[0102]

sendheader状态:发送以太网udp帧帧头状态;当发送状态机处于sendmac状态,且i=13 时,即mac地址发送完毕后,即进入此状态,用于发送预设和计算的udp帧头。

[0103]

senddata状态:发送以太网udp数据状态;当发送状态机处于sendheader状态,且i=6 时,即以太网udp帧帧头发送完毕后,即进入此状态,用于发送adc数据,当senddata状态结束后,停止计算以太网校验码。

[0104]

sendcrc状态:发送以太网帧校验码状态,当发送状态机处于senddata状态,且i=data_length 时,即待发送数据完毕后,即进入此状态,用于发送以太网帧校验码,当i=4时,停止发送,将以太网发送数据有效信号(tx_en)置0,并将发送状态机返回idle状态,等待下次发送以太网帧。

[0105]

所述检验模块采用crc校验方式;为保证以太网传输通道的可靠性,采用一定的检错和纠错方式,以太网使用的循环冗余校验码(crc)中crc-32校验码作为以太网帧的最后4个字节用于传输,生成表达式为:

[0106][0107]

在fpga中,crc实现方式分为串行方式和并行方式,串行方式每个时钟仅处理一个比特,此种实现方式实现简单,资源占用少;但是此种方式实现速度慢,不适合处理千兆以太网数据。并行方式是一个时钟处理多个比特,千兆以太网每个时钟8个比特,与千兆以太网的gmii接口协议相吻合,故千兆以太网的crc校验码生成和校验中使用并行方式。

[0108]

crc校验码计算时加法使用的是模2加,即0+0=0,0+1=1,1+1=0,因此crc的生成表达式可以用简单的异或运算和移位寄存器即可实现。串行方式是当每一个时钟输入1bit数据后,通过生成表达式经过异或和移位计算即可实现当前比特的crc值,即计算crc的值只与当前输入bit和当前crc有关。并行运算可以看做多个串行同时输入,将生成的crc进行带入,可以8比特并行输入,crc-32部分表达式为:

[0109][0110]

fpga计算crc的过程简单,以太网帧中mac地址和udp首部和帧数据需要进行crc 计算,在ipsend模块中状态转换时计算以太网校验码标志信号已经置1,在此信号置1时即进行crc计算,当计算结束后,将crc结果恢复到初始值ffffffff。

[0111]

在本实施例中,该系统还包括pcb设计:印制线路板pcb实现各个元件之间的电气互联,决定整个声发射采集系统的可靠性和稳定性,本实施例pcb设计采用cadence公司的 allegro软件;pcb布局如图15所示,围绕以fpga为核心元件进行布局,元件均匀整齐紧凑布局在pcb中,pcb中信号流通方向从左到右,信号经过传感器流通到前端调理电路,然后流向

adc,经过模数转换流通到fpga中,在电源和芯片周围放置了去耦电容和滤波电容,提高了抗干扰能力;

[0112]

另外本实施例是高速采集系统,数字信号的高频噪声很大,如果模拟信号和数字信号混合,会把噪声传到模拟部分,图15中的折线表明将模拟地与数字地分割,折线左部分是模拟信号,右部分是数字信号,中间通过零欧电阻或者磁珠进行连接,从而减少噪声干扰。

[0113]

在本实施例中,该系统还包括电源电路,确保电源的功率大于总器件功耗,使系统稳定工作。本实施例分为数字电源和模拟电源,其中数字电源主要给adc、fpga、通信模块等数字器件进行供电;模拟电源主要是放大器、滤波器等供电,如图16所示;本实施例采用两种类型电源芯片,即线性稳压电源(ldo)和直流转直流电压(dc/dc);ldo电源芯片稳定性好,负载响应快,输出纹波小,仅能使用在降压应用中;dc/dc电源芯片效率高,输入电压范围较宽。因此,外接12v电源经过dc/dc电源芯片转化为数字电源3.3v、1.2v、1.8v以及模拟电源的+6v和-6v,然后经过ldo电源芯片将+6v和-6v转化为数字的+5v和+3v以及模拟+5v、-5v、+2.5v。

[0114]

在本实施例中,桥梁拉索断丝采集系统主要包括adc数据采集软件设计、千兆以太网通信模块、crc校验模块、adc数据存储模块和fpga内部ip核的应用,即采用vhdl语言在fpga中实现,异步fifo通过添加fpga内部ip核方式实现,时钟分配通过fpga内部 pll核实现;所有程序文件及功能如表5所示:

[0115]

表5采集系统程序文件及实现功能

[0116][0117]

为了验证adc数据采集的性能,将adc理想值输出和实际值输出进行对比,数值相同或者接近说明adc数据采集准确性高。通过ads1675数据手册得知,此芯片的输出24位,模拟输入0v~+3v时,用16进制表示转化为数字输出是0x000000~0x7fffff,用10进制表示转化为数字输出是0~8388607。模拟输出电压和理想值数字输出电压转化关系为:

[0118][0119]

其中,v

out

是理想值数据输出,v

in

是模拟输入电压,即adc输入,直流信号测试如表6 所示,信号源输入指信号发生器发出的电压,adc输入指信号进入adc时的电压,用万用表测

出,实际值与理想值均用10进制表示,理想值经过运算得到的值,adc输出值经过 chipscope转化为10进制得到的值,理想值减去adc输出值的绝对值除以理想值就是误差,在百万级的数字中实际值与理想值最大不超过1000,误差低于0.02%,精度很高。

[0120]

表5-1 adc直流测试表

[0121][0122]

测试直流性能后,通过信号源发送频率分别为100khz、200khz、300khz的交流正弦信号验证硬件电路有效性,将adc程序软件通过ise软件烧入到pcb板卡中,打开chipscope 软件进行信号采集,得到正确的正弦波形,如图17是信号源发送100khz正弦波得到的采集结果,为标准的正弦波,因此设计的硬件电路是有效的;当信号源输入200khz、300khz正弦波时,输入100khz采集波形一样,验证硬件电路有效且adc数据采集准确。

[0123]

验证以太网传输正确性需要wireshark软件和netassist软件的支持,wireshark是一个网络封包分析软件,能够撷取网络封包,并尽可能显示出最为详细的网络封包资料;netassist 是网络串口调试软件,可以用来网络的串口间的通信,实行串口的监控、调试,该工具支持 udp与tpc协议,只需输入相应的主机与监听的ip地址,为用户提供多链接与多数据格式解析的功能;

[0124]

将adc和以太网合在一起的全部程序下载到板卡中,通过信号源输入100khz正弦波信号,当打开wireshark软件能看到传输的udp协议包时,说明pcb板卡和pc端链接成功,

打开netassist软件进行接收数据,将所得到的数据导入matlab中进行数据处理;netassist 软件接收的数据保存到txt中,此时使用matlab按照字符读取此txt,txt中每个数据为16 进制的数据,每8个数据为一个adc的数据,在matlab中读取了2000个数据进行分析,这2000个数据是每个adc采集的数据,16进制;然后将16进制的adc采集数据转化为 10进制,因为每个adc数据的高8位为0x5a,因此在数据分析中需要将5a减掉;如图18 是信号源发送100khz正弦波为例通过matlab所得的采集结果,即标准的正弦波,因此以太网传输是有效的;当信号源输入200khz、300khz正弦波时,matlab处理结果和输入100khz 正弦波形一样,验证以太网传输是准确有效的。

[0125]

为验证系统集成之后的整体性能,本实施例通过断铅实验模拟产生声发射信号,将声发射传感器用胶带固定在一块平坦的钢板上面,将铅笔与钢板平面置于30

°

的夹角进行折断,铅笔折断位置距离传感器5厘米,传感器采集到声发射信号通过前端电路处理、adc模数转换、千兆以太网将数据传输到上位机、上位机在matlab中进行波形处理,将所得到的波形和在同样的实验条件下与m2p.59xx-x4得到的结果进行对比分析;

[0126]

通过将铅笔芯折断,采集到16进制数据通过matlab进行处理,每个adc数据的高8 位为0x5a,因此在数据分析中需要将5a减掉,然后将16进制的adc采集数据转化为10 进制,如图19(a)所示,能够明显看到有两个高幅值信号,如图19(b)所示是利用德国 spectrum数字化仪m2p.59xx-x4进行断铅信号采集数据,并通过该公司自带的matlab程序处理,图19(a)和图19(b)采集处理结果波形一致,图中显示的这两个高幅值信号就是铅笔芯折断产生的声发射信号,说明本系统能够正确采集到信号且能够区分出断铅信号;

[0127]

将图19(a)采集到的断铅信号波形局部放大如图19(c)所示,图19(d)表示的是m2p.59xx-x4系统采集,经过该系统自带的软件处理的波形信号,通过对比可以发现采集到的波形一致,说明本系统能够正确采集到信号且能够区分出断铅信号,在未来的桥梁实际应用中,当桥梁拉索出现断丝时本系统性能是可行的,能够正确检测桥梁断丝声发射信号;

[0128]

实施例2

[0129]

本实施例提供一种桥梁拉索断丝声信号采集方法,包括:

[0130]

对接收的初始断丝声信号采用放大电路和滤波电路进行放大处理和滤波处理后,经模数转换电路得到的数字断丝声信号;

[0131]

对数字断丝声信号采用fifo存储器进行存储,经fifo存储器将数字断丝声信号通过千兆以太网模块发送至上位机;

[0132]

采用循环冗余校验码对千兆以太网模块传输数字断丝声信号时进行校验。

[0133]

以上仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

[0134]

上述虽然结合附图对本发明的具体实施方式进行了描述,但并非对本发明保护范围的限制,所属领域技术人员应该明白,在本发明的技术方案的基础上,本领域技术人员不需要付出创造性劳动即可做出的各种修改或变形仍在本发明的保护范围以内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1