自举型半桥驱动器共模电压变化率耐受测试装置及方法与流程

1.本发明涉及电子技术领域,特别涉及一种自举型半桥驱动器共模电压变化率耐受测试装置及方法。

背景技术:

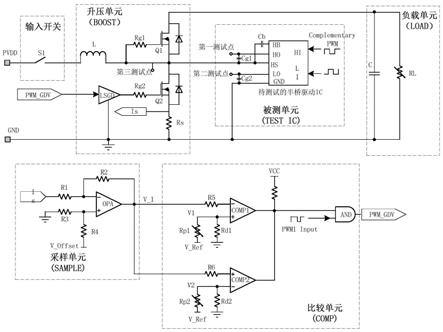

2.如图1所示,自举型半桥驱动ic(integrated circuit集成电路)因为需要连接到半桥的桥臂中点,会工作在高dv/dt(共模电压变换率)的条件下,因此,自举型半桥驱动ic对dv/dt的耐受能力是一个非常重要的指标。目前业内测试该耐受能力最常用的方法通过如图1所示的测试电路来进行的。

3.图1中的测试电路包含电感l、二极管d1、nmos管q1,低压门驱动器(lsgd low side gate driver)、电阻rg2以及待测试的自举型半桥驱动ic(以下简称为半桥驱动ic)。其中,半桥驱动ic包含hb脚、ho脚、hs脚、lo脚、gnd脚、hi脚、li脚。hi和li脚用于输入互补的pwm信号。hb脚连接电容cb第一端,ho脚连接电容cg1第一端,lo脚与gnd脚之间通过电容cg2连接。功率电源pvdd连接电感l的第一端、二极管d1的负极,电感l的第二端、二极管d1的正极、nmos管q1的漏极、hs脚、电容cb第二端、电容cg1第二端互相连接。lsgd的输入端用于输入nmos管q1的驱动信号pwm_gdv,lsgd的输出端通过电阻rg2连接nmos管q1的栅极,nmos管q1的源极接地。

4.通过快速的开关n型场效应管q1(若关断电流足够大),则在测试点3也能够产生高的dv/dt,若将半桥驱动ic的hs脚(共模输入端)接至测试点3,则半桥驱动ic就工作于高的dv/dt条件下,在高的dv/dt条件下,半桥驱动ic的ho和lo脚的输出可能会发生电平异常。

5.图1所示的测试电路还具有如下局限性:

6.局限1)电感l的电流不受控;没有引入电流侦测,导致开环的pwm控制会使电感l的电流不受控而不断增大,最终导致电感饱和而使nmos管q1损坏。因此,为了避免这一状况,此电路只能工作很短的时间,否则n型场效应管q1会因为过流而损坏;

7.局限2)nmos管q1的占空比不好选择:占空比太大,则电流上升很快,容易烧管;占空比太小,又导致电流爬升慢,导致关断电流小,在测试点3产生的dv/dt不够;

8.局限3)不能自动测试dv/dt临界耐受点,因局限1和局限2限制,导致该测试电路只能多次反复的试验来确定半桥驱动ic对dv/dt的耐受点。

9.专利cn106468757a提到的测试ipm(intelligent power module智能功率模块)模块(其内部集成了6个igbt和3个半桥驱动ic)抗干扰能力的方法,是通过high side(高边)的igbt(insulated gate bipolar transistor绝缘栅双极型晶体管)的开关来产生dv/dt噪声。由于ipm将芯片和igbt(mosfet)封装在一起,因此其内部寄生的电容较大,ipm内部的driver(驱动器)进行igbt(mosfet)的驱动,就可能产生足以干扰其内部半桥驱动ic工作的dv/dt噪声。但这种方式不适应于单体半桥驱动ic的dv/dt测试,因为单体的半桥驱动ic寄生电容相对小,因此需要更大的dv/dt才能导致其工作失效。

10.专利cn102109573a提到的一种dv/dt耐受能力的测试方法,是通过一个附加电路,

来实时改变被测芯片的共模电压承受端vs脚与gnd脚的dv/dt,这种方式和实际芯片的应用场景并不一致,因此测试出来的结果可能会有偏差。

技术实现要素:

11.本发明的目的是提供一种自举型半桥驱动器共模电压变化率耐受测试装置及方法,通过升压单元为待测半桥驱动电路生成冲击电流,进而测试得到共模电压变化率dv/dt失效点和恢复点,获得待测半桥驱动电路对共模电压变化率的耐受能力,同时通过设置采样单元和比较单元,保证了在测量的过程中升压单元工作在安全工作电流范围内,并且保证了待测半桥驱动电路hs脚的电压不会过冲,有效的保护了测试装置,防止元件损坏。

12.为了达到上述目的,本发明提供一种自举型半桥驱动器共模电压变化率耐受测试装置,包含:待测试的自举型半桥驱动电路、采样单元、比较单元、升压单元;

13.所述待测试的自举型半桥驱动电路包含:hb脚、ho脚、hs脚、lo脚、gnd脚、hi脚、li脚,gnd脚接地;

14.所述升压单元的输入端连接功率电源pvdd,升压单元的输出端连接所述hs脚;通过升压单元生成用于测试半桥驱动电路共模电压变换率的冲击电流;通过测试升压单元输出端与hs脚之间的连接点的共模电压变化率获取半桥驱动电路的共模电压变化率耐受范围,并通过升压单元保证半桥驱动电路的共模电压变化率在安全耐受范围;

15.所述采样单元的输入端连接升压单元,采集升压单元的工作电流is,通过采样单元用于对所述工作电流is进行采样,生成采样电流v_1;

16.所述比较单元的输入端连接采样单元的输出端,比较单元的输出端连接升压单元;当比较单元判断v_1落在升压单元安全工作电流范围内,时,比较单元生成用于驱动升压单元工作的驱动信号pwm_gdv;比较单元还用于调节所述升压单元安全工作电流范围。

17.优选的,所述采样单元包含运算放大器opa,电阻r1、r2、r3;电阻r1的第一端连接升压单元,获取所述工作电流is,电阻r1的第二端连接运算放大器opa输入端的负极、电阻r2的第一端;电阻r3的第一端接地,电阻r3的第二端、电阻r4的第一端连接运算放大器opa输入端的正极;电阻r2的第二端连接运算放大器opa的输出端;电阻r4的第二端连接偏移电压v_offset。

18.优选的,所述比较单元包含比较器comp1、comp2,电阻r5、r6、r7、rd1、rd2,可调电阻rp1、rp2,与门and;电阻r5连接设置在运算放大器opa的输出端与比较器comp1输入端的负极之间;电阻rd1的第一端接地,可调电阻rp1的第一端接参考电压v_ref;电阻rd1的第二端、可调电阻rp1的第二端连接比较器comp1输入端的正极;电阻r6连接设置在运算放大器opa的输出端与比较器comp2输入端的正极之间;电阻rd2的第一端接地,可调电阻rp2的第二端接参考电压v_ref,电阻rd2的第二端、可调电阻rp2的第二端连接比较器comp2输入端的负极;比较器comp1、comp2的输出端通过电阻r7连接电压vcc;比较器comp1、comp2的输出端均连接与门and的第一输入端,与门and的第二输入端连接脉宽调制信号pwm1;当v_1落在所述升压单元安全工作电流范围内,与门and生成所述驱动信号pwm_gdv。

19.优选的,所述电压vcc和与门and的电压匹配,所述调制信号pwm1的占空比为50%。

20.优选的,所述升压单元包含:电感l,电阻rg1、rg2,采样电阻rs,nmos管q1、q2,驱动单元lsgd;

21.电感l的第一端连接功率电源pvdd,电感l的第二端通过电阻rg1连接nmos管q1的栅极,电感l的第二端连接nmos管q1的源极、nmos管q2的漏极和所述hs脚;

22.驱动单元lsgd的第一端连接与门and的输出端,驱动单元lsgd的第二端通过电阻rg2连接nmos管q2的栅极,驱动单元lsgd的第三端接地;nmos管q2的源极连接采样电阻rs的第一端、电阻r1的第一端;采样电阻rs的第二端接地;nmos管q2的源极电流为所述工作电流is。

23.优选的,所述自举型半桥驱动器共模电压变化率耐受测试装置,其特征在于,还包含输入开关s1,连接设置在功率电源pvdd与电感l的第一端之间。

24.优选的,所述自举型半桥驱动器共模电压变化率耐受测试装置,还包含负载单元;所述负载单元包含母线电容c和可调电阻rl;母线电容c的第一端、可调电阻rl的第一端连接nmos管q1的漏极,母线电容c的第二端、可调电阻rl的第二端接地。

25.优选的,所述半桥驱动电路还包含:电容cb、cg1、cg2;电容cb连接设置在hb脚与hs脚之间,电容cg1连接设置在ho脚与hs脚之间,电容cg2连接设置在lo脚与gnd脚之间;hi脚和li脚用于输入互补的带宽调制信号pwm。

26.本发明还提供一种自举型半桥驱动器共模电压变化率耐受测试方法,采用本发明所述的自举型半桥驱动器共模电压变化率耐受测试装置实现的,包含步骤:

27.f1、将第一测量点设置在ho脚与电容cg1之间,将第二测量点设置在lo脚与电容cg2之间,将第三测量点设置在nmos管q1的源极与电阻rg1的第一端之间;通过示波器连接第一、第二测量点,测量半桥驱动电路的带宽调制信号pwm是否为异常状态;通过示波器连接第三测量点,测量升压单元向半桥驱动电路hs脚输出的母线冲击电流;

28.f2、断开输入开关s1,调整电阻rp1、rp2,使rp1、rp2满足在功率电源pvdd向所述测试装置供电时,rp1的电流v1大于rp2的电流v2;

29.f3、闭合输入开关s1,观察带宽调制信号pwm的波形;当带宽调制信号pwm的波形出现丢波,通过示波器读出半桥驱动电路共模电压变换率的失效点,进入f4;否则进入f2;

30.f4、断开输入开关s1,调节rp1实现增大rp1的电流v1,调节rp2实现增大或降低rp2的电流v2;

31.f5、闭合输入开关s1,观察示波器,判断带宽调制信号pwm的波形是否不再丢波;若是,进入f6;若否,进入f4;

32.f6、从示波器读出半桥驱动电路共模电压变换率的恢复点。

33.优选的,步骤f2中:

[0034][0035][0036]

r

p1

为电阻rp1调整后的电阻值,r

p1

为电阻rp1调整后的电阻值,r

s

为采样电阻rs的阻值,r1、r2为电阻r1、r2的阻值,r

d1

为电阻rd1的阻值,r

d2

为电阻rd2的阻值,且(r

p1

+r

d1

)=(r

p2

+r

d2

)=r

p

。

[0037]

与现有技术相比,本发明的有益效果在于:

[0038]

1)本发明的自举型半桥驱动器共模电压变化率耐受测试装置能够有效测试得到共模电压变化率dv/dt失效点和恢复点,从而获得待测半桥驱动电路对共模电压变化率的耐受能力;

[0039]

2)本发明通过设置采样单元和比较单元,保证了在测量的过程中升压单元工作在安全工作电流范围内,并且保证了待测半桥驱动电路hs脚的电压不会过冲,有效的保护了测试装置,防止元件损坏;

[0040]

3)本发明中通过设置负载单元,平衡测试装置对待测试半桥驱动电路、升压模块的输入功率,防止功率管因为过压或过流发生损坏;

[0041]

4)本发明中能够通过调整比较单元的电阻rp1、rp2来调节升压单元的工作电流的范围,不必在每次测试中更换测试装置中的nmos管。

附图说明

[0042]

为了更清楚地说明本发明技术方案,下面将对描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本发明的一个实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图:

[0043]

图1为现有技术中的半桥驱动ic共模电压变化率的测试电路示意图;

[0044]

图2为本发明的自举型半桥驱动器共模电压变化率耐受测试装置示意图;

[0045]

图3为本发明的自举型半桥驱动器共模电压变化率耐受测试方法流程图;

[0046]

图4为本发明的实施例中,nmos管q1的工作区间示意图;

[0047]

图5为本发明的实施例中,通过在第一测试点、第三测试点采集的pwm波、hs脚电压波形判断dv/dt失效点和恢复点示意图;

[0048]

图6为本发明的实施例中,在第一测试点、第三测试点所采集的pwm波、hs脚电压波形示意图;

[0049]

图7为本发明的实施例中,在第一、第二测试点所采集的pwm波以及在第三测试点采集的电压波形示意图。

具体实施方式

[0050]

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

[0051]

如图1所示,本发明提供一种自举型半桥驱动器共模电压变化率耐受测试装置,包含:待测试的自举型半桥驱动电路、采样单元、比较单元、升压单元,输入开关s1,负载单元。

[0052]

所述待测试的自举型半桥驱动电路包含:hb脚、ho脚、hs脚、lo脚、gnd脚、hi脚、li脚,gnd脚接地;所述半桥驱动电路还包含:电容cb、cg1、cg2;电容cb连接设置在hb脚与hs脚之间,电容cg1连接设置在ho脚与hs脚之间,电容cg2连接设置在lo脚与gnd脚之间;hi脚和li脚用于输入互补的带宽调制信号pwm。将第一测量点设置在ho脚,将第二测量点设置在lo脚,将第三测量点设置在hs脚;通过示波器连接第一、第二测量点,测量半桥驱动电路的带宽调制信号pwm是否为异常状态(丢波);通过示波器连接第三测量点,根据pwm波形的状态

测量结果,通过示波器观察升压单元向hs脚输出的母线冲击电流(也可简称为冲击电流),获得半桥驱动电路dv/dt的耐受失效点和耐受恢复点。

[0053]

所述升压单元的输入端连接功率电源pvdd,升压单元的输出端连接所述hs脚。输入开关s1设置在升压单元与功率电源pvdd之间,当s1从断开状态变为闭合状态时,升压单元内会产生瞬时的冲击电流。通过测试升压单元与所述hs脚之间的连接点(第三测量点)的共模电压变化率dv/dt获取半桥驱动电路的dv/dt耐受范围,并通过控制升压单元的冲击电流,保证半桥驱动电路的dv/dt在安全耐受范围。

[0054]

如图2所示,所述升压单元包含:电感l,电阻rg1、rg2,采样电阻rs,nmos管q1、q2,驱动单元lsgd;

[0055]

输入开关s1,连接设置在功率电源pvdd与电感l的第一端之间;电感l的第一端连接功率电源pvdd,电感l的第二端通过电阻rg1连接nmos管q1的栅极,电感l的第二端连接nmos管q1的源极、nmos管q2的漏极和所述hs脚;

[0056]

驱动单元lsgd的第一端连接与门and的输出端,驱动单元lsgd的第二端通过电阻rg2连接nmos管q2的栅极,驱动单元lsgd的第三端接地;nmos管q2的源极连接采样电阻rs的第一端、电阻r1的第一端;采样电阻rs的第二端接地;

[0057]

所述采样单元的输入端连接升压单元nmos管q2的源极,将nmos管q2的源极电流作为升压单元的工作电流is,通过采样单元对所述工作电流is进行采样,生成采样电流v_1。当然在其他实施例中,升压单元的工作电流不仅仅限于从nmos管q2的源极获取,此仅为本发明的示例,不应作为本发明的限制。

[0058]

如图2所示,所述采样单元包含运算放大器opa,电阻r1、r2、r3;电阻r1的第一端连接升压单元nmos管q1的源极,获取所述工作电流is;电阻r1的第二端连接运算放大器opa输入端的负极、电阻r2的第一端;电阻r3的第一端接地,电阻r3的第二端、电阻r4的第一端连接运算放大器opa输入端的正极;电阻r2的第二端连接运算放大器opa的输出端;电阻r4的第二端连接偏移电压v_offset。所述偏移电压v_offset为采样偏置电压,用来消除gnd脚上的噪声对采样信号造成影响,同时将负电流信号转化成正电压信号,所述偏移电压v_offset电压一般为所述电压vcc的一半。运算放大器opa的输出端输出采样电流v_1。

[0059]

所述比较单元的输入端连接采样单元的输出端,比较单元的输出端连接升压单元。所获得的采样电流v_1被比较单元用于侦测升压单元的工作状态。当比较单元判断v_1落在升压单元安全工作电流范围内时,比较单元向nmos管q1的栅极生成用于驱动q1工作的高电平驱动信号pwm_gdv;否则pwm_gdv为低电平,nmos管q1停止工作,升压单元失电。比较单元还用于调节所述升压单元安全工作电流范围,进而控制所述冲击电流的大小,防止hs脚产生过高的dv/dt。

[0060]

如图2所示,所述比较单元包含比较器comp1、comp2,电阻r5、r6、r7、rd1、rd2,可调电阻rp1、rp2,与门and;电阻r5连接设置在运算放大器opa的输出端与比较器comp1输入端的负极之间;电阻rd1的第一端接地,可调电阻rp1的第一端接参考电压v_ref;电阻rd1的第二端、可调电阻rp1的第二端连接比较器comp1输入端的正极;电阻r6连接设置在运算放大器opa的输出端与比较器comp2输入端的正极之间;电阻rd2的第一端接地,可调电阻rp2的第二端接参考电压v_ref,电阻rd2的第二端、可调电阻rp2的第二端连接比较器comp2输入端的负极;比较器comp1、comp2的输出端通过电阻r7连接电压vcc;比较器comp1、comp2的输

出端均连接与门and的第一输入端,与门and的第二输入端连接脉宽调制信号pwm1;当v_1落在所述升压单元安全工作电流范围内,与门and生成所述驱动信号pwm_gdv。

[0061]

在本发明的实施例中,通过调节可调电阻rp1、rp2确定nmos管q1工作的安全电流范围。若给nmos管q1预设的安全电流范围为[v1,v2],通过调节可调电阻rp1使得rp1的电流为v1,通过调节可调电阻rp2使得rp2的电流为v2。当v_1落在[v1,v2]的范围内,与门and的第一输入端才能够获得一个高电平信号,当pwm1也为高电平时,比较单元输出高电平的驱动信号pwm_gdv用于驱动nmos管q1工作。显然,可以通过调整pwm1的占空比,调节升压单元所生成的冲击电流的大小(也即平衡pvdd的输入功率,防止nmos管q1、q2因过流、过压产生损坏)。在本发明的实施例中,所述电压vcc和与门and的电压匹配,所述调制信号pwm1的占空比为50%。

[0062]

所述负载单元包含母线电容c和可调电阻rl;母线电容c的第一端、可调电阻rl的第一端连接nmos管q1的漏极,母线电容c的第二端、可调电阻rl的第二端接地。通过负载单元平衡功率电源pvdd的输入功率,使整个测试装置达到稳态工作,避免nmos管q1、q2因过流、过压产生损坏。

[0063]

本发明的基本原理为:当s1闭合时,功率电源pvdd通过q1的体内二极管,直接对母线电容c充电,会在输入端产生很大的冲击电流。若q2在某一个电流区间工作,则会有选择性的切断电感l的电流,并产生合适的冲击电流以供待测驱动半桥驱动电路的共模电压变化率耐受测试。由于本发明的测试装置具有电流选择性,因此nmos管q2的占空比可任意配置,且通过负载单元的可变电阻rl,使得本发明的测试装置在稳态条件下的电流不大,能够长时间工作。本发明可以克服现有技术中测量半桥驱动电路dv/dt中电感电流不受控、q1的占空比不好选择等弊端。

[0064]

如图4所示,在本发明的实施例中,nmos管的最大工作电流i1和最小工作电流i2是通过调节可调电阻rp1和rp2来实现的,当母线冲击电流在此范围以内,则q2的pwm处于工作状态(pwm on),否则为关断状态(pwm off)。在母线电流爬升的过程中,t1时刻,dv/dt已经到达了ic的失效点a,此时半桥驱动电路会出现丢波的现象。在母线电流下降的t2时刻,dv/dt回落到b,则半桥驱动电路不再丢波恢复正常。

[0065]

当母线冲击电流过大时,可以调节i1,使nmos管q1的关断电流处于安全的区域,避免q1、q2管损坏,同时也避免半桥驱动电路在过大的dv/dt下损坏。

[0066]

实施例一

[0067]

如图5所示,图5中的ch2通道(对应第三测试点)的峰值包络波形反映了母线冲击电压的变化曲线。而在dv/dt失效点之前,ch1通道(对应于第一测试点)显示待测半桥驱动电路的pwm为正常状态(50%占空比上叠加共模信号),在dv/dt的失效点和恢复点之间,待测半桥驱动电路的pwm为异常状态(丢波),dv/dt恢复点之后,则待测半桥驱动电路又恢复到正常状态(50%占空比上叠加共模信号)。因此,只需测试dv/dt失效点和dv/dt恢复点的dv/dt的数值,就可以获得待测半桥驱动电路的临界dv/dt耐受值,这是这一线路对业内传统方式最有效的改进。

[0068]

图6为测试dv/dt失效点时所采集的第一、第三测试点的波形,分别对应ho脚的pwm波形(ch1通道)和hs脚的电压波形(ch2通道)。通过观察该两个通道的波形,发现pwm波失波的过程中,母线冲击电压在2.2ns的时间内从66v(a点)上升到了203v(b点),因此计算得到

dv/dt的耐受失效点=(203

‑

66)/2.2=62v/ns。

[0069]

图7为测试dv/dt恢复点时所采集的第一至第三测试点的波形,其中第一、第二测试点的波形为ho、io脚的pwm波形(分别对应图7中ch1通道1和ch3通道的波形),第三测试点的波形为hs脚的电压波形(对应图7中ch2通道的波形)。发现pwm波恢复正常时,母线冲击电压在2.44ns的时间内从210v下降到了71v,因此计算得到dv/dt的耐受恢复点=(210

‑

71)/2.44=56v/ns。

[0070]

本发明还提供一种自举型半桥驱动器共模电压变化率耐受测试方法,采用本发明所述的自举型半桥驱动器共模电压变化率耐受测试装置实现的,如图3所示包含步骤:

[0071]

f1、将第一测量点设置在ho脚与电容cg1之间,将第二测量点设置在lo脚与电容cg2之间,将第三测量点设置在nmos管q1的源极与电阻rg1的第一端之间;通过示波器连接第一、第二测量点,测量半桥驱动电路的带宽调制信号pwm是否为异常状态;通过示波器连接第三测量点,测量升压单元向半桥驱动电路hs脚输出的母线冲击电流;

[0072]

f2、断开输入开关s1,调整电阻rp1、rp2,使rp1、rp2满足在功率电源pvdd向所述测试装置供电时,rp1的电流v1大于rp2的电流v2;

[0073]

步骤f2中:

[0074][0075][0076]

r

p1

为电阻rp1调整后的电阻值,r

p1

为电阻rp1调整后的电阻值,r

s

为采样电阻rs的阻值,r1、r2为电阻r1、r2的阻值,r

d1

为电阻rd1的阻值,r

d2

为电阻rd2的阻值,且(r

p1

+r

d1

)=(r

p2

+r

d2

)=r

p

。

[0077]

f3、闭合输入开关s1,观察带宽调制信号pwm的波形;当带宽调制信号pwm的波形出现丢波,通过示波器读出半桥驱动电路共模电压变换率的失效点,进入f4;否则进入f2;

[0078]

f4、断开输入开关s1,调节rp1实现增大rp1的电流v1,调节rp2实现增大或降低rp2的电流v2;

[0079]

f5、闭合输入开关s1,观察示波器,判断带宽调制信号pwm的波形是否不再丢波;若是,进入f6;若否,进入f4;

[0080]

f6、从示波器读出半桥驱动电路共模电压变换率的恢复点。

[0081]

在本发明的实施例中,为达到良好的测试效果,还对所述耐受测试装置的电感l,nmos管q1、q2,驱动单元lsgd还具有以下要求:

[0082]

1、关于电感l的选取

[0083]

本专利采用的是boost主电路拓扑作为升压单元,为了防止电感l饱和,导致电路损坏,必须选择合适的电感l,使测试装置最终工作到稳定状态。假设测试装置最终输出电压为v

o

,最终稳态电感电流为i

l

,pvdd的输入电压为v

in

,pwm1的占空比为d,纹波系数为δ,s1的开关频率为f

s

,则电感感量为:

[0084]

[0085]

电感的磁芯需选择具有一定直流偏置的磁芯,比如铁硅铝或者铁硅等环状磁芯。同时,电感的线径需满足稳态工作电流下持续运行。

[0086]

2、关于nmos管q1、q2的选取

[0087]

由于本测量装置需产生高dv/dt,因此nmos管q1和q2不仅需满足测试时的工作电压和工作电流需求,同时还必须能够耐受高dv/dt,以免因dv/dt太大,导致q1和q2的体内二极管发生损坏。同时,为了获得很快的开关速度,q1和q2必须选择具有非常小的qg(gate charge)的器件,一般情况下,其qg<15nc。

[0088]

2、关于驱动单元lsgd的选取

[0089]

本发明中只需要驱动处于低边(low side)的nmos管q1、q2工作,因此选择合适的底边驱动单元lsgd即可,为了使q1、q2快速的开关,必须选择具有高驱动电流的lsgd芯片,其峰值需大于5a。

[0090]

以上所述,仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到各种等效的修改或替换,这些修改或替换都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应以权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1