一种基于TDC的假目标增补系统的制作方法

一种基于tdc的假目标增补系统

技术领域

1.本发明属于时间数字转换器(tdc)领域,特别涉及一种基于tdc的假目标增补系统。

背景技术:

2.利用tdc芯片进行目标距离信息获取的方法,得到越来越广泛的应用,特别是在测距领域中,采用出光时刻作为时间计算的开始,第一个目标的回波信号作为停止时刻,两个时刻之间的时间差即为光的飞行时间,根据飞行时间可得到距离的方法。此方法广泛应用于测距领域。

3.专利201420829174.4及20192007354.0提供了在连接方式、测距方法,以及误差计算方面的应用方案。但该专利主要针对tdc芯片在多目标测量模式下,单目标补充为多目标,同时不影响多目标测距的方法,对该方法进行保护,未涉及数据的处理及测距系统连接方式等具体细节。

4.tdc多应用于高精度测距仪中,对可同时采集的目标数有一定限制,并且对目标数设定后只能采集固定的目标数,对少于设定目标数的目标不进行采集。目前市场上的tdc芯片可做到单目标和多目标测量。但在多目标测量模式下,若只返回单个目标,tdc芯片无法响应,不能实现单目标和多个目标的测量的精确测量。

技术实现要素:

5.本发明针对现有技术中存在的技术问题,提供一种基于tdc的假目标增补系统,在不影响真实目标的情况下,对目标的回波进行增补,使tdc芯片可以采集到所设定的目标数。

6.本发明采用的技术方案是:一种基于tdc的假目标增补系统,包括

7.光电采集电路模块,用于向逻辑门电路模块和tdc电路模块发出采样信号;

8.定时器电路模块,用于向逻辑门电路模块发出持续的脉冲信号;

9.逻辑门电路模块,用于利用采样信号和脉冲信号对回波信号进行目标数量增补,然后将增补后的回波信号发送到tdc电路模块;

10.tdc电路模块,用于接收逻辑门电路模块和光电采集电路模块发送的信号。

11.作为优选,所述逻辑门电路模块采用或门,利用采样信号和脉冲信号形成增补的假目标,增补的假目标在目标的回波信号之后。

12.作为优选,定时器电路模块发出的脉冲信号为方波。

13.作为优选,所述逻辑门电路模块的电路结构为:或门芯片n1引脚1和引脚2为输入引脚,分别接光电采集电路模块的采样信号和定时器电路模块的脉冲信号,或门芯片n1引脚5为电源引脚接+5v;或门芯片n1引脚3为接地引脚,直接与地相连,或门芯片n1引脚4为输出引脚,通过电阻r8与三极管q1的b极相连;所述三极管q1的e极接地,所述三极管q1的c极通过r6接+5v,同时通过r7与或门芯片n3引脚1相接;或门芯片n3引脚2为输入引脚,与接收

到的回波信号相接;或门n3芯片引脚4为输出引脚,接tdc电路模块;或门n3芯片引脚5为电源引脚接+5v;或门n3芯片引脚3为接地引脚,直接与地相连。

14.作为优选,所述定时器电路模块的电路结构为:定时器芯片n2引脚1接地,引脚5通过电容c1接地;所述定时器芯片n2引脚4、引脚8接+5v;所述定时器芯片n2引脚2与引脚6相接并通过电容c2接地;所述定时器芯片n2引脚7通过电阻r1接+5v,同时通过电阻r3与引脚2相接;所述定时器芯片n2引脚3为输出引脚;所述定时器芯片n2采用gcm7555。

15.作为优选,所述光电采集电路模块的电路结构为:单稳态芯片d4a的引脚3、引脚16接+5v;所述单稳态芯片d4a的引脚8、引脚1接地;所述单稳态芯片d4a的引脚15通过电容c47与引脚14相连并接地,通过电阻r52接+5v;所述单稳态芯片d4a的引脚2为单稳态芯片的输入引脚,引脚2通过电阻r58、c49与二极管d1阳极相连;所述二极管d1阴极通过电阻r50接+5v;发光二极管d6阳极与单稳态芯片d4a的引脚3相连;发光二极管d6阴极通过电阻r66与单稳态芯片d4a的引脚4相连;所述单稳态芯片d4a的引脚13为输出引脚;所述单稳态芯片d4a采用sn74ls123。

16.作为优选,所述tdc电路模块的电路结构为:tdc芯片u1引脚1为有源晶振输入引脚,与晶振b1的引脚3通过串联的电阻r9、c5相连;所述tdc芯片u1引脚3、引脚22为芯片io口引脚供电输入端,与+5v相连;所述tdc芯片u1引脚4、引脚16、引脚17、引脚21、引脚28与地相连;所述tdc芯片u1引脚7通过r11与地相连;所述tdc芯片u1引脚26通过电阻r2与3.3v相接;所述tdc芯片u1引脚32通过电阻r4与3.3v相接;所述tdc芯片u1引脚31接光电采集电路模块;所述tdc芯片u1引脚30接逻辑门电路模块;所述tdc芯片u1引脚14、引脚29为电源引脚接3.3v;所述tdc芯片u1引脚13通过电阻r10接3.3v,同时通过电容c6接地;所述tdc芯片u1引脚8、引脚9、引脚10、与主控芯片相接。

17.工作原理:在不影响目标信号返回时间的基础上,增加假目标。即在目标返回的回波信号一段时间后再出现一定数量的信号,作为返回的假目标。逻辑门电路模块,将光电采集电路模块信号cyo和定时器电路模块的信号out555通过或门计算形成信号q555,取反后与返回的回波信号sigback0再通过一个或门计算形成信号sigback1,将假目标增补到原返回目标之后。假目标的增补与原返回目标的数量无关,且不影响原返回目标。在tdc芯片设定为多目标采集的情况下,探测单目标时tdc芯片依旧可以正确探测目标,实现单目标与多目标的同时探测。并且信号响应的速度快,不依赖于数字产生信号时,由晶振引起的误差。定时器电路模块发出持续的频率一定的脉冲信号,脉冲信号的输出频率及占空比由内部的电容、电阻控制,不受晶振影响。

18.与现有技术相比,本发明所具有的有益效果是:

19.1.本发明在不影响真实目标的情况下,对返回的目标进行增补,使tdc芯片可以采集到所设定的目标数。

20.2.本发明通过模拟电路的搭建,信号响应时间快。

21.3.本发明相较于传统的嵌入式芯片产生增补信号,有稳定的信号输出,不依赖于晶振的产生,减小了晶振震荡过程中引入的误差。

附图说明

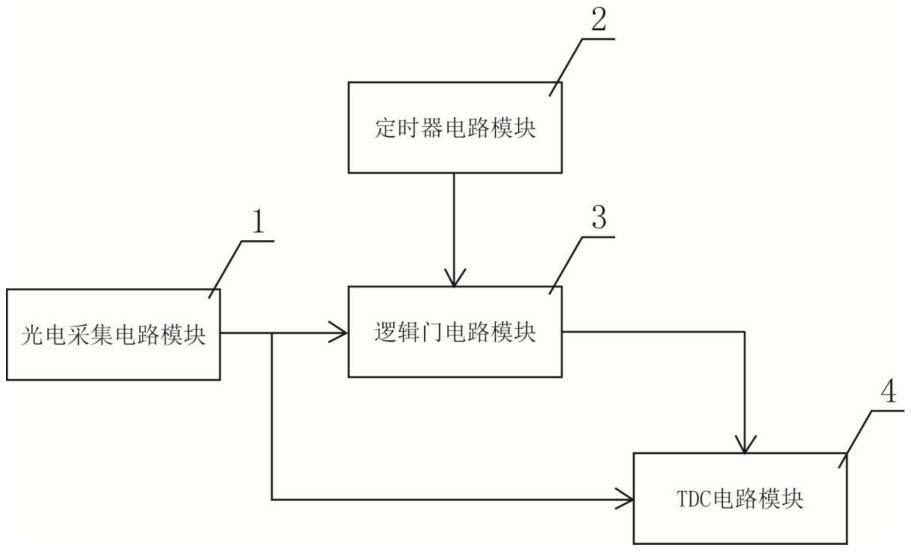

22.图1为本发明实施例的结构框图;

23.图2为本发明实施例的光电采集电路模块的电路图;

24.图3为本发明实施例的定时器电路模块的电路图;

25.图4为本发明实施例的逻辑门电路模块的电路图;

26.图5为本发明实施例的tdc电路模块的电路图;

27.图6为本发明实施例的信号增补过程时序图。

28.图中1-光电采集电路模块,2-定时器电路模块,3-逻辑门电路模块,4-tdc电路模块。

具体实施方式

29.为使本领域技术人员更好的理解本发明的技术方案,下面结合附图和具体实施例对本发明作详细说明。

30.本发明的实施例提供了一种基于tdc的假目标增补系统,如图1所示,其包括光电采集电路模块1,用于向逻辑门电路模块和tdc电路模块发出采样信号;

31.定时器电路模块2,用于向逻辑门电路模块发出持续的脉冲信号;定时器电路模块发出的脉冲信号为方波。

32.逻辑门电路模块3,用于利用采样信号和脉冲信号对返回信号进行目标数量增补,然后将增补后的信号发送到tdc电路模块;所述逻辑门电路模块采用或门,利用采样信号和脉冲信号形成增补的假目标,增补的假目标在目标的回波信号之后。

33.tdc电路模块4,用于接收逻辑门电路模块和光电采集电路模块发送的信号。

34.如图2所示,所述光电采集电路模块1的电路结构为:单稳态芯片d4a的引脚3、引脚16接+5v;所述单稳态芯片d4a的引脚8、引脚1接地;所述单稳态芯片d4a的引脚15通过电容c47与引脚14相连并接地,通过电阻r52接+5v;所述单稳态芯片d4a的引脚2为单稳态芯片的输入引脚,引脚2通过电阻r58、c49与二极管d1阳极相连;二极管d1阳极通过电阻r56接地;所述二极管d1阴极通过电阻r50接+5v,并通过电容c45接地;发光二极管d6阳极与单稳态芯片d4a的引脚3相连;发光二极管d6阴极通过电阻r66与单稳态芯片d4a的引脚4相连;所述单稳态芯片d4a的引脚13为输出引脚,输出信号cyo。所述单稳态芯片d4a采用sn74ls123。通过电阻r58、电阻r50、电容c49、电容c45可调整二极管d1采集到的信号上升速度。

35.如图3所示,所述定时器电路模块2的电路结构为:定时器芯片n2引脚1接地,引脚5通过电容c1接地;所述定时器芯片n2引脚4、引脚8接+5v;所述定时器芯片n2引脚2与引脚6相接并通过电容c2接地;所述定时器芯片n2引脚7通过电阻r1接+5v,同时通过电阻r3与引脚2相接。所述定时器芯片n2引脚3为输出引脚,输出信号out555。所述定时器芯片n2采用gcm7555。通过电阻r1、电阻r3、电容c1和电容c2可控制定时器芯片n2引脚3的信号输出频率及占空比。

36.如图4所示,所述逻辑门电路模块3的电路结构为:或门芯片n1引脚1为输入引脚,与定时器芯片n2引脚3相接,输入信号out555;所述或门芯片n1引脚2为输入引脚与单稳态芯片d4引脚13相连,输入信号cyo;所述或门芯片n1引脚4为输出引脚,通过电阻r8与三极管q1的b极相连,向三极管q1的b极输出信号q555;所述或门n1芯片引脚5为电源引脚接+5v;所述或门n1芯片引脚3为接地引脚,直接与地相连;所述三极管q1的e极接地;所述三极管q1的c极通过r6接+5v,同时通过r7与或门芯片n3引脚1相接,向或门芯片n3引脚1输出信号

q555n;所述或门芯片n3引脚2为输入引脚,与接收到的回波信号sigback0相接;所述或门n3芯片引脚4为输出引脚,输出信号sigback1;所述或门n3芯片引脚5为电源引脚接+5v;所述或门n3芯片引脚3为接地引脚,直接与地相连。或门芯片n1和或门芯片n2采用tc7s32f。

37.如图5所示,所述tdc电路模块4的电路结构为:tdc芯片u1引脚1为有源晶振输入引脚,与晶振b1的引脚3通过串联的电阻r9、c5相连;所述tdc芯片u1引脚3、引脚22为芯片io口引脚供电输入端,与+5v相连;所述tdc芯片u1引脚4、引脚16、引脚17、引脚21、引脚28与地相连;所述tdc芯片u1引脚7通过r11与地相连;所述tdc芯片u1引脚26通过电阻r2与3.3v相接;所述tdc芯片u1引脚32通过电阻r4与3.3v相接;所述tdc芯片u1引脚31与单稳态芯片d4a引脚13通过电阻r57相接,输入信号cyo;所述tdc芯片u1引脚30与或门n3引脚4相连,输入信号sigback1;所述tdc芯片u1引脚14、引脚29为电源引脚接3.3v;所述tdc芯片u1引脚13通过电阻r10接3.3v,同时通过电容c6接地;所述tdc芯片u1引脚8、引脚9、引脚10、与主控芯片相接。

38.信号增补过程中,信号cyo、out555、q555、q555n、sigback0、sigback1的波形如图6所示。sigback1为sigback0增补后的信号。tdc芯片从cyo信号上升沿到来开始工作,sigback1的信号只有虚线框内波形被tdc引脚31 stop1所识别,无论sigback0有几个脉冲,输入到tdc引脚31的脉冲一定多于所设定的脉冲数,完成对sigback0信号的增补。

39.上述各芯片也可选用同类型的芯片代替,电路结构做适应性调整。

40.以上通过实施例对本发明进行了详细说明,但所述内容仅为本发明的示例性实施例,不能被认为用于限定本发明的实施范围。本发明的保护范围由权利要求书限定。凡利用本发明所述的技术方案,或本领域的技术人员在本发明技术方案的启发下,在本发明的实质和保护范围内,设计出类似的技术方案而达到上述技术效果的,或者对申请范围所作的均等变化与改进等,均应仍归属于本发明的专利涵盖保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1