1.本发明涉及半导体技术领域,具体涉及一种感测装置及对应的测试方法。

背景技术:2.传统mems传感器的测试有很多难点,针对不同的mems传感器,由于传感器受到的激励不同,往往需要多样化的物理测试激励,目前工业上没有一种通用的解决方案,并且测试设备昂贵,测试过程耗时耗力,测试效率低,这无疑大大增加了传感器的成本。另外,压阻传感器使用时间一段后,性能可能会降低,需测试是否符合要求,然而,现有可以实现对已投入使用的压阻传感器进行测试的方法耗时耗力,提高测试成本的同时也很不方便。因此,提出一种测试方案,使传感器不依赖于传统测试设备即可实现功能的自测试是很有意义的。

技术实现要素:3.本发明的目的是提供一种感测装置及对应的测试方法,具有传感器性能自测功能。

4.本发明实施例提供了以下方案:

5.第一方面,本发明实施例提供一种感测装置,所述感测装置包括:

6.压阻传感器,所述压阻传感器包括:

7.依次堆叠设置的基底、敏感层及保护层,所述敏感层的一侧设有空腔结构,另一侧设有敏感薄膜;

8.压敏电阻,设置于所述敏感层内;

9.电极,设置于所述保护层一侧,且与所述压敏电阻相连;以及

10.自测结构,设置于所述保护层一侧;以及

11.控制模块包括:

12.磁性单元,所述磁性单元包括相对设置的磁体,所述磁体对称设置于所述压阻传感器的两侧,所述磁性单元用于提供均匀磁场,使得所述压阻传感器处于所述均匀磁场中;以及

13.cpu,与磁性单元及所述压阻传感器相连,所述cpu用于控制所述磁性单元产生所述均匀磁场,以及输出控制信号至所述自测结构,所述自测结构在磁场作用下产生压力,所述压力使得所述敏感层发生形变,进而使得所述压敏电阻的阻值发生变化,所述电极输出代表所述压敏电阻阻值变化的电压值,所述cpu接收所述电压值,并根据所述电压值判断所述压阻传感器的性能参数是否正常。

14.可选的,所述控制模块还包括连接至所述磁性单元与所述cpu之间的多路开关,所述多路开关的一端与所述磁性单元、所述自测结构及所述电极相连,另一端与所述cpu相连,所述多路开关用于控制所述磁性单元开启及关闭,以及控制所述压阻传感器在正常工作模式与测试模式之间切换。

15.可选的,所述控制模块还包括连接至所述多路开关及所述压阻传感器与所述cpu的数据处理单元,所述数据处理单元包括电性连接的连接至所述多路开关与所述cpu之间的第一a/d转换电路及第一i/o电路、电性连接至所述压阻传感器与所述cpu之间的第二a/d转换电路及第二i/o电路。

16.可选的,所述控制模块还包括连接至所述压阻传感器与所述cpu之间的温度补偿单元,所述温度补偿单元用于感测所述压阻传感器周边的温度,并根据所述温度对所述压阻传感器进行温度补偿。

17.可选的,所述自测结构位于所述电极的中间,且对应所述敏感层的空腔结构设置。

18.可选的,所述自测结构由多根并联的金属线绕制形成。

19.可选的,所述控制模块还包括电路板,所述压阻传感器及控制模块均设置于所述电路板上。

20.可选的,所述控制模块还包括固支结构,所述传感器设置于所述固支结构上,所述固支结构固定于所述电路板上。

21.第二方面,本发明实施例提供一种测试方法,用于对一种压阻传感器进行性能测试,所述压阻传感器包括:依次堆叠设置的基底、敏感层及保护层;压敏电阻,设置于所述敏感层内;电极,设置于所述保护层的一侧,且与所述压敏电阻相连;所述测试方法包括:

22.将自测结构设置于所述保护层的一侧;

23.提供均匀磁场,使得所述压阻传感器及所述自测结构处于所述均匀磁场中;

24.输出控制信号至所述压阻传感器的自测结构,控制所述自测结构在磁场作用下产生压力,使得所述敏感层发生形变,进而使得所述压敏电阻的电阻值发生变化;

25.接收所述压阻传感器的电极输出代表电阻值变化的电压值,以及

26.根据所述电压值判断所述压阻传感器的性能参数是否正常。

27.可选的,所述测试方法还包括:

28.感测所述压阻传感器周边的温度;以及

29.根据所述温度对所述压阻传感器进行温度补偿。

30.本发明与现有技术相比,具有如下的优点和有益效果:

31.本发明实施例感测装置通过在压阻传感器上设置自测结构,并通过测试装置对处于均匀磁场中的自测结构发送控制信号实现基于安培力的激励,来代替现有技术中通过物理激励,实现对压阻传感器的性能测试,从而使得所述感测装置具有感测性能自测功能,如此,即便将感测装置装配至电子装置后,也可方便地对其感测性能进行测试。

附图说明

32.为了更清楚地说明本说明书实施例或现有技术中的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本说明书的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

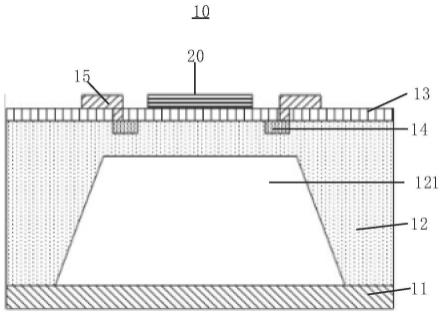

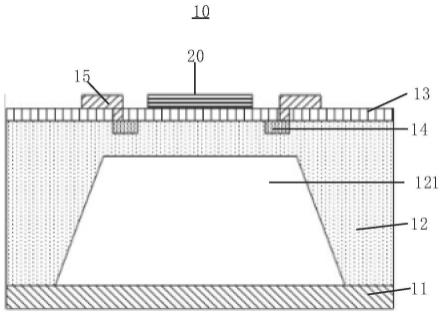

33.图1是本发明实施例提供的一种感测装置的压阻传感器的截面图。

34.图2是图1所示的压阻传感器的自测结构的平面示意图。

35.图3是本发明实施例提供的一种感测装置的控制模块的电路图。

36.图4是本发明实施例提供的一种感测装置的示意图。

具体实施方式

37.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整的描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例,基于本发明实施例,本领域普通技术人员所获得的所有其他实施例,都属于本发明实施例保护的范围。

38.请参阅图1,图1是本发明实施例提供的一种感测装置的压阻传感器的截面图。感测装置包括压阻传感器10、自测结构20及控制模块30(见图3)。

39.在本实施例中,压阻传感器10为绝压式mems(micro electronic mechanical system,微机电系统)压阻传感器。压阻传感器10包括基底11、敏感层12、保护层13、压敏电阻14、电极15。基底11、敏感层12、保护层13依次堆叠设置。压敏电阻14设置于敏感层12内。电极15设置于保护层13的一侧,且与压敏电阻14相连。

40.在本实施例中,基底11由玻璃制成。敏感层12的一侧设有空腔结构121,另一侧设有敏感薄膜。具体地,敏感层12由硅衬底形成,采用深硅刻蚀工艺,在硅衬底的一侧形成空腔结构121,同时,在硅衬底的另一侧形成敏感薄膜。保护层13由氮化硅或者二氧化硅制成。

41.绝压式mems压阻传感器在敏感薄膜通过离子注入技术或者掺杂形成压敏电阻14,再将硅衬底的底部与基底11键合形成真空封闭的空腔结构121,当敏感薄膜顶端受到外界施加压力时,敏感薄膜表面的压敏电阻14的压阻效应被放大,使得压敏电阻14的电阻率发生变化,连通薄膜表面的压敏电阻14形成惠斯通电桥,测量电桥输出电压值即可计算出敏感薄膜所受压力值,从而达到测量绝压的目的。在本实施例中,请参阅图2,所述压阻传感器10包括4个压敏电阻14,形成所述惠斯通电桥。

42.自测结构20设置于保护层13的一侧,当压阻传感器10处于均匀磁场内,且自测结构20接收到控制信号时,自测结构20产生压力,压力使得敏感层12发生形变,进而使得压敏电阻14的电阻值发生变化,电极15输出代表所述电阻值变化的电压值。

43.在本实施例中,所述自测结构20为线圈结构,线圈结构位于电极15的中间,且对应敏感层12的空腔结构121设置。请一并参阅图2,在一个实施例中,线圈结构呈正方形。

44.具体地,控制信号为预设电压,当预设电压连接至线圈结构的两端,线圈结构通电后,线圈结构产生安培力,进而产生按压敏感层12的压力。

45.具体地,线圈结构由多根并联的金属线绕制形成,设置在电极15之间,所述金属线可为铝、金、银等具有高导电性,且低电阻率的金属线。

46.在本实施例中,以线圈结构由多根并联的铝线绕制形成为例,加以说明。当压阻传感器10处于均匀磁场中,当线圈结构通电时,单根铝线受到的电磁力,也就是单根铝线上产生的安培力满足以下关系式

①

:

47.f=bil;

[0048][0049]

[0050]

其中,i表示流经单根铝线的电流;b表示匀强均匀磁场的均匀磁场密度;l表示单根铝线的长度;v表示预设电压;r表示单根铝线的电阻;a表示单根铝线截面的宽度;b表示单根铝线截面的高度;ρ表示铝线的电阻率。

[0051]

对应地,单根铝线产生的安培力与对应施加至敏感膜的压力p满足关系式

②

:

[0052]

f/al(n/m2)=p(pa)。

[0053]

由关系式

①

及

②

可知,当需要向线圈结构施加预设压力值,例如,1mpa时,可通过对单根铝线的长度l、单根铝线截面的宽度a及单根铝线截面的高度b进行调整直至线圈产生的压力为预设压力值。

[0054]

另外,当线圈结构通电时,线圈结构会产生一定的热量,单根铝线的功率满足关系式

③

:

[0055][0056]

其中,r表示单根铝线的电阻;a表示单根铝线截面的宽度;b表示单根铝线截面的高度;ρ表示铝线的电阻率;p表示单根铝线产生的功率;v表示预设电压。

[0057]

由关系式

③

可知,单根铝线的长度l越长、截面积越小时,单根铝线的功率越小。因此,在对单根铝线的长度l、单根铝线截面的宽度a及单根铝线截面的高度b进行调整时,可使得单根铝线的长度l尽可能大,且截面积尽可能小。

[0058]

请参阅图3,所述控制模块30用于压阻传感器10进行性能测试。控制模块30包括磁性单元31及cpu 32。所述磁性单元31包括相对设置的磁体31a,所述磁体31a对称设置于所述压阻传感器10的两侧,磁性单元31用于提供均匀磁场,使得压阻传感器10处于所述均匀磁场中。cpu 32与磁性单元31、自测结构20及压阻传感器10相连,cpu 32用于控制所述磁性单元31产生均匀磁场,以及输出控制信号至自测结构20,使得自测结构20产生压力,所述压力驱动敏感层12发生形变,进而使得压敏电阻14的电阻值发生变化,电极15输出代表电阻值的变化的电压值,cpu 32接收所述电压值,并根据所述电压值判断压阻传感器10的性能参数是否正常。

[0059]

具体地,性能参数包括敏感度及线性度等,可以通过压阻传感器10的压敏电阻的阻值的变化值表征的性能指标。

[0060]

具体地,磁体31a为电磁铁或者永久磁性单元。进行测试时,磁体31放置于压阻传感器10的两侧。

[0061]

具体地,控制模块30还包括连接至磁性单元31与cpu 32之间的多路开关33,多路开关33的一端与磁性单元31、自测结构20及电极15相连,另一端与cpu 32相连,多路开关33用于控制磁性单元31开启及关闭,以及控制所述压阻传感器10在正常工作模式与测试模式之间切换。其中,当自测结构20与cpu 32相连,则压阻传感器10进入测试模式,当自测结构20与cpu 32断开,则压阻传感器10进入正常工作模式。

[0062]

具体地,控制模块30还包括连接至多路开关33与cpu 32的数据处理单元34,数据处理单元34包括连接至所述多路开关33与所述cpu 32之间的第一a/d转换电路341a及第一i/o电路342a,连接至所述压阻传感器10与所述cpu 32之间的第二a/d转换电路342a及第二i/o电路342b。第一a/d转换电路341a用于对多路开关33与cpu 32之间传输的信号进行数模转换,第一i/o电路342a用于支持多路开关33与cpu 32之间数据的输入及输出。第二a/d转

换电路341b用于对压阻传感器10与cpu 32之间传输的信号进行数模转换,第二i/o电路342b用于支持压阻传感器10与cpu 32之间的数据的输入及输出。

[0063]

当周围环境温度变化时,压敏电阻14的阻值可能因温度变化而发生变化,因此,在本实施例中,控制模块30还包括温度补偿单元35,温度补偿单元35用于感测压阻传感器10周边的温度,并根据所感测的温度对压阻传感器10进行温度补偿,从而较少温度对压敏电阻14的阻值的变化的影响,提高测试的准确度。在本实施例中,温度补偿单元35采用热敏电阻和温度系数很小的电阻的并联电路。

[0064]

另外,控制模块30还包括连接至温度补偿单元35与多路开关33之间的放大器36,用于感测的温度信号的放大。

[0065]

请参阅图4,在一个实施例中,所述控制模块30设置于电路板40上,所述压阻传感器10通过固支结构50固定在电路板40上,磁体31a对称地设置于所述压阻传感器10的两侧,提供所述均匀磁场。

[0066]

基于与方法同样的发明构思,本发明实施例还提供了一种测试方法,用于压阻传感器10进行性能测试。

[0067]

所述测试方法包括以下步骤:

[0068]

步骤s1,将自测结构20设置于所述压阻传感器10的保护层13的一侧。

[0069]

步骤s2,提供均匀磁场,使得所述压阻传感器10及所述自测结构20处于所述均匀磁场中。

[0070]

步骤s3,输出控制信号至压阻传感器10的自测结构20,控制自测结构20产生压力,以使得敏感层12发生形变,进而使得压敏电阻14的阻值发生变化。

[0071]

步骤s4,接收压阻传感器10的电极15输出电阻的变化值。

[0072]

步骤s5,根据电阻的变化值判断压阻传感器10的性能是否正常。

[0073]

在另一实施例中,测试方法还包括:

[0074]

步骤s6,感测压阻传感器10周边的温度。

[0075]

步骤s7,根据所感测的温度对压阻传感器10进行温度补偿。

[0076]

本发明实施例中提供的技术方案,至少具有如下技术效果或优点:

[0077]

本发明实施例感测装置通过在压阻传感器10上设置自测结构20,并通过测试装置20对处于均匀磁场中的自测结构20发送控制信号实现基于安培力的激励,来代替现有技术中通过物理激励,实现对压阻传感器10的性能测试,从而使得所述感测装置具有感测性能自测功能,如此,即便将感测装置装配至电子装置后,也可方便地对其感测性能进行测试。

[0078]

尽管已描述了本发明的优选实施例,但本领域内的技术人员一旦得知了基本创造概念,则可对这些实施例作出另外的变更和修改。所以,所附权利要求意欲解释为包括优选实施例以及落入本发明范围的所有变更和修改。

[0079]

显然,本领域的技术人员可以对本发明进行各种改动和变型而不脱离本发明的精神和范围。这样,倘若本发明的这些修改和变型属于本发明权利要求及其等同技术的范围之内,则本发明也意图包括这些改动和变型在内。