数字电路延时测试方法、测试电路和集成电路芯片与流程

1.本发明涉及集成电路技术。

背景技术:

2.现有技术中,对数字电路延时的测量皆是依托外部测量电路,精度受外部电路制约,并且无法满足现场实时测量需求。

技术实现要素:

3.本发明所要解决的技术问题是,提供一种内置于芯片的数字电路延时测试技术,能够准确对功能模块的延时性能进行测试。

4.本发明解决所述技术问题采用的技术方案是,数字电路延时测试方法,其特征在于,包括下述步骤:

5.1)在起始时刻对待测模块的数据端口发送测试数据,相邻两个间隔的时长增量为t,所述间隔为相邻两次测试数据之间的时长;

6.2)对待测模块的输出数据和输入数据作比较,当二者不一致时,输出激励信号;

7.3)统计起始时刻到激励信号的发出时刻之间的测试数据发送次数,结合t值计算待测模块的时延。

8.本发明还提供一种数字电路延时测试电路,包括下述部分:

9.可调延时模块,用于生成相邻周期增量为t的可变时钟信号,并且向统计模块输出增量信息;

10.测试数据发生器,与可调延时模块连接,用于在收到可调延时模块的输出信号激励沿时,向待测模块发送测试数据;

11.数据比较器,其第一输入端接待测模块的数据输出端,其第二输入端接测试数据发生器的输出端,其输出端接统计模块的控制端;

12.统计模块,用于统计起始时刻到控制端收到激励信号时刻之间的测试数据发送次数。

13.所述数据发生器为随机数发生器。

14.本发明还提供一种内建前述数字电路延时测试电路的集成电路芯片。

15.本发明能够准确测试芯片内部功能模块的延时,采用内建方式降低了对外部仪器的依赖,减少了芯片封装、输入输出电路、pcb走线等对测试延时精度的影响。

附图说明

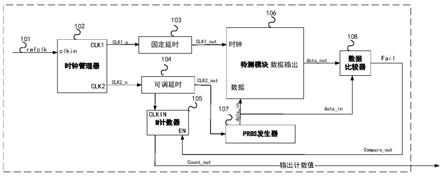

16.图1是本发明的测试电路结构示意图。

17.图2是本发明的时序图。

18.图3是本发明的可调延时模块原理图。

19.图4是待测模块的信号时序图。

具体实施方式

20.解释:

21.refclk基准时钟。

22.clk1_o 时钟管理单元clk1输出。

23.clk2_o 时钟管理单元clk2输出。

24.fixed_dly 固定延时单元。

25.vari_dly 可变延时单元。

26.clk1_out 经过固定延时输出。

27.clk2_out 经过可变延时输出。

28.compare_out 数据比较器输出。

29.en 计数器使能信号。

30.count_out 计数器输出。

31.参见图1,本发明的数字电路延时测试电路包括下述部分:

32.可调延时模块,用于生成相邻周期增量为t的可变时钟信号,并且向统计模块输出增量信息;

33.测试数据发生器,与可调延时模块连接,用于在收到可调延时模块的输出信号激励沿时,向待测模块发送测试数据;

34.数据比较器,其第一输入端接待测模块的数据输出端,其第二输入端接测试数据发生器的输出端,其输出端接统计模块的控制端;

35.统计模块,用于统计起始时刻到控制端收到激励信号时刻之间的测试数据发送次数。图1中以计数器作为统计模块。

36.所述数据发生器为随机数发生器(prbs发生器)。

37.本发明在芯片内部集成或者使用可编程资源,时钟管理器、prbs数据发生器、数据比较器、延时单元(包括固定延时单元和可调延时单元)、m计数器及相关控制信号。

38.数据比较器用于将待测模块输出的数据与prbs发生器生成的数据进行逻辑“异或”运算,在data_out与data_in数据不一致时,输出fail信号给计数器,计数器统计当前的延时模块的tap值并输出,根据tap值可得知内部参数的延时。

39.本发明总的结构分为7级:

40.第一级:基准时钟101。可以通过芯片内部电路产生,也可以通过芯片外部时钟。

41.第二级:时钟管理器102。其作用是将基准时钟倍频两路一样的时钟输出给延时模块。

42.第三级:延时模块,时钟经第二级输入给延时模块。其中,一路时钟的延时为固定延时单元103,另外一路的时钟为可调延时单元104,分别给待测单元时钟端口提供时钟和待测单元的数据提供时钟。可调延时单元的原理图参见图3。本发明将时钟管理器和可调延时单元合称为可调延时模块,其输出参见图2。固定延时是通过寄存器设定一个固定的值,可变延时是通过寄存器设定不同的调延时的大小。图2中,fixed_dly是指固定延时,vari_dly是指可变延时(可调延时)。

43.延时器tap由多个延时电路级联构成,tap的个数可通过寄存器设置调节。clk1_out为固定延时单元输出波形,clk2_out为可变延时单元输出波形,clk2_out的每一个在后

的时钟脉冲的周期比前一时钟脉冲的周期多一个tap的时间。在实际运用中,tap数和tap单元的延时时间由各待测件决定。

44.第四级:m计数器105,其作用是当en接收到第七级输出fail信号时,统计延时单元的tap个数并输出收到fail信号时的当前的tap个数。

45.第五级:待测模块106,其信号时序图参见图4。

46.第六级:prbs发生器107,伪随机二进制序列(pseudo random binary sequence,简称prbs发生器)。

47.第七级:数据比较器108,其作用是把第六级的数据与第五级待测单元输出的数据进行比较,数据不一致时输出fail信号给第四级计数器的en端口。

48.当待测件芯片使用内部逻辑产生一个refclk基准时钟(也可以通过芯片外部输入一个基准时钟),时钟管理器开始工作并输出clk1_o和clk2_o,经过固定/可变延时单元后输出clk1_out与clk2_out时钟,这时计数器开始计数,然后分别把clk1_out与clk2_out给待测单元提供时钟,待测模块输入待测数据后,待测模块的data_out输出到数据比较器中进行与期望值比较,当数据比较器输出fail信号时,计数器就输出当前计数值。

49.实例:设待测模块频率为100mhz,延时模块共有64个tap单元,每个tap的延时为50ps。

50.固定延时单元为tap1,可调延时模块的延时通过寄存器设置tap值,当数据比较器输出fail信号时,触发计数器的en信号,并输出计数器当前计数值为21,则说明待测单元的延时,在可变延时单元tap21时数据输出错误,说明待测模块可正常工作的延时时间为50*(21

‑

1)=1000ps=1ns。

51.其典型的测试结果如图2所示。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1