一种半导体器件用测试座的制作方法

1.本实用新型涉及一种测试座,尤其涉及一种用于半导体器件的测试座。

背景技术:

2.在半导体芯片大规模研发及生产过程中均需要各类性能检测,芯片测试座为测试中关键部件,测试座功能是将芯片定位后通过线路板之间电子信号电流传输从而达到测试效果,测试座的质量和匹配程度直接影响测试判断准确性.

3.目前常见的测试座产品定位为普通吸嘴自动校正对位定位及盖板定位,测试片单片安装以及直接在测试片上直接焊接电流传输及信号线。

4.但是在实际的使用中发现,这样的测试座具有如下缺点:

5.1、测试片单片安装装配,影响整体配合精度及测试效果,浪费维护维修费时。

6.2、产品测试时定位不准确,接触有偏差影响测试精准度。

7.3、在测试片上直接焊接,费时、接触性能不好,影响测试标准。

8.4、测试不稳定。

技术实现要素:

9.本实用新型目的是为了克服现有技术的不足而提供一种增强了测试片引脚与芯片管脚的接触性以及测试片与pcb的接触,从而使得测试稳定,测试良率高的半导体器件用测试座。

10.为达到上述目的,本实用新型采用的技术方案是:一种半导体器件用测试座,包括:

11.基座,在所述基座的顶部设有pcb基板;

12.在所述pcb基板上设有放置口,所述放置口内设有用于放置芯片的限位座;

13.在所述限位座底端设有用于芯片下压时缓冲的缓冲组件,且缓冲组件设置在基座内;

14.在所述放置口的两侧设有位于pcb基板上的多个平行设置的焊盘;

15.在所述放置口内设有位于基座上的左测试片座和右测试片座;所述左测试片座和所述右测试片座内各自设有多个测试片,且所述测试片分别与对应两侧的焊盘相连接;

16.其中,所述左测试座和右测试座内的测试片前端引脚分别与限位座内的芯片管脚相接触。

17.进一步的,在所述基座内还设有无磁线圈。

18.进一步的,所述缓冲组件包括升降杆,在所述升降杆的顶部设有与限位座相连的升降块;在所述升降杆内位于升降块的下方设有缓冲弹簧;所述缓冲弹簧的底部设有位于升降杆上的限位装置。

19.进一步的,所述pcb基板与线路引线转接器相连。

20.进一步的,所述焊盘的数量为十二个,每侧平行设置六个;所述左测试片座和所述

右测试片座内的测试片的数量为六个。

21.由于上述技术方案的运用,本实用新型与现有技术相比具有下列优点:

22.本实用新型方案的半导体器件用测试座,增强了测试片引脚与芯片管脚的接触性以及测试片与pcb的接触,提高了接触的可靠性,测试片一体式对称设计提高了使用寿命的同时节省了维修维护更换时间,整体的精度质量提高,测试稳定,测试良率高,提高了生产效率降低成本。

附图说明

23.下面结合附图对本实用新型技术方案作进一步说明:

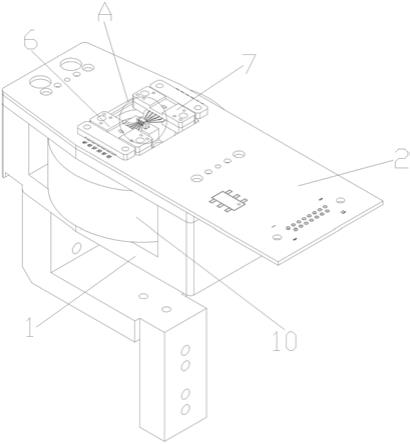

24.附图1为本实用新型的结构示意图;

25.附图2为附图1中a的局部放大图;

26.附图3为本实用新型的立体结构分解图;

27.附图4为附图3中b的局部放大图;

28.附图5为缓冲装置的结构示意图;

29.附图6为pcb基本与线路引线转接器相连的结构示意图

30.其中:基座1、pcb基板2、芯片3、限位座4、焊盘5、左测试片座6、右测试片座7、测试片8、线路引线转接器9、无磁线圈10、缓冲装置11、放置口20、升降杆30、升降块31、限位装置32。

具体实施方式

31.下面结合附图及具体实施例对本实用新型作进一步的详细说明。

32.请参阅附图1-6,本实用新型所述的一种半导体器件用测试座,包括:基座1,在所述基座1的顶部设有pcb基板2;在所述pcb基板2上设有放置口20,所述放置口20内设有用于放置芯片3的限位座4,其中限位座4的材质为陶瓷制成的;在所述限位座4底端设有用于芯片3下压时缓冲的缓冲组件,且缓冲组件设置在基座1内。

33.在所述放置口20的两侧设有位于pcb基板2上的六个平行设置的焊盘5,此时焊盘采用的是开尔文的设定,这样一共有十二个焊盘,左侧的六个焊盘以4f、4s、5f、5s、6f、6s作为标记依次排序,右侧的六个焊盘以1f、1s、2f、2s、3f、3s作为标记依次进行排序;在所述放置口20内设有位于基座1上的左测试片座6和右测试片座7.

34.所述左测试片座6和所述右测试片座7内各自设有六个测试片8,同时左测试座6内的六个测试片分别焊接在以4f、4s、5f、5s、6f、6s为标记的焊盘上,右测试片座7内的六个测试片分别焊接在以1f、1s、2f、2s、3f、3s为标记的焊盘上;同时以1f、1s、2f、2s、3f、3s为标记的焊盘上的测试片引脚与芯片的右端管脚相接触,以4f、4s、5f、5s、6f、6s为标记的焊盘焊盘上的测试片引脚与芯片的左端管脚相接触。

35.具体的,上述测试片分3组6片,每1组两片为一路开尔文,即对应相应的f、s焊盘,其中第一组与第三组为对称第二组两片为对称,测试片采取高精度设备整体切割不分离,通过设备一体化装配,使其切割装配中不分体,提高整体一致性,保证整体配合精度,测试片高精度能够更好的配合与芯片的接触从而保证和提高了测试的可靠性及有效性。

36.另外,pcb基板1采取线路曝光蚀刻成型,焊盘与测试片焊接后进行电接触,其中焊

盘还可以镀金,整体电测接触通过pcb基板线路连通后,再通过线路引线转接器引出连通设备。

37.作为进一步的优选实施例,所述缓冲组件包括升降杆30,在所述升降杆30的顶部设有与限位座4相连的升降块31;在所述升降杆30内位于升降块31的下方设有缓冲弹簧(图中未示出);所述缓冲弹簧的底部设有位于升降杆30上的限位装置32,这样当芯片3被下压时,升降杆30配合缓冲弹簧构成悬浮式的结构,从而能够很好的配合芯片3在下压时与测试片的接触缓冲提搞接触性能,限位座内的限位槽通过切割研磨达到所需定位精度,陶瓷制成的限位座绝缘耐磨,并通过限位槽可精准定位来保证芯片与测试片的接触精度。

38.作为进一步的优选实施例,在所述基座1内还设有无磁线圈10,对本测试座进行无磁处理,避免检测时影响测试的精度准,达到客户需求,保证检测的稳定性。

39.本实用新型的半导体器件用测试座,增强了测试片引脚与芯片管脚的接触性以及测试片与pcb的接触,提高了接触的可靠性,测试片一体式对称设计提高了使用寿命的同时节省了维修维护更换时间,整体的精度质量提高,测试稳定,测试良率高,提高了生产效率降低成本。

40.以上仅是本实用新型的具体应用范例,对本实用新型的保护范围不构成任何限制。凡采用等同变换或者等效替换而形成的技术方案,均落在本实用新型权利保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1