一种压力传感器在线标定系统

1.本实用新型属于压力传感器技术领域,具体涉及一种压力传感器在线标定系统。

背景技术:

2.压力传感器在众多行业中都有重要的应用,且压力传感器在市场中的需求量很大,因此提高压力传感器的生产效率尤为重要。

3.现有的压力传感器标定过程多为通过外接电阻箱或电位器进行重复性工作的调试,调试装置复杂,且调试过程繁琐且效率低,影响压力传感器的调试效率,进而影响压力传感器的生产效率。

技术实现要素:

4.本实用新型的目的:在于提供一种结构简单、操作方便且高效率的压力传感器在线标定系统。

5.技术方案:本实用新型提供的压力传感器在线标定系统,用于针对设置有调零电阻位和调幅电阻位的压力传感器进行标定;其特征在于,压力传感器在线标定系统包括调零电路、调幅电路、微处理器及控制电路、电阻表、开关k1、开关k2、开关k3、开关k4,以及用于为调零电路、调幅电路、微处理器及控制电路供电的电源变换电路;

6.调零电路的第一电阻端通过开关k3和电阻表的第一信号输入端相连,并且该相连位置通过开关k1和压力传感器中调零电阻位的一端相连;调零电路的第二电阻端和电阻表的第二信号输入端、压力传感器中调零电阻位的另一端相连;调零电路和微处理器及控制电路相连,进行数据交互;

7.调幅电路的第一电阻端通过开关k4和电阻表的第一信号输入端相连,并且该相连位置通过开关k2和压力传感器中调幅电阻位的一端相连;调幅电路的第二电阻端和电阻表的第二信号输入端、压力传感器中调幅电阻位的另一端相连;调幅电路和微处理器及控制电路相连,进行数据交互;调零电路的第二电阻端和调幅电路的第二电阻端相连;

8.压力传感器的信号输出端对接微处理器及控制电路的信号输入端;微处理器及控制电路和上位机通信连接。

9.作为本实用新型的一种优选方案,电源变换电路包括用于提供电压vcc1的第一电压输出端,以及用于提供电压vcc2的第二电压输出端。

10.作为本实用新型的一种优选方案,所述电源变换电路包括电源模块s1、基准源模块 s2、电容cs1、电容cs2、电解电容es1、二极管ds;

11.电源模块s1的输入端外接电源电压,电源模块s1的正向电压输出端分别和电容cs1 的一端、电解电容es1的正极、二极管ds的负极、基准源模块s2的信号输入端、电容 cs2的一端相连,连接点构成电源变换电路的第一电压输出端;

12.电源模块s1的负向电压输出端分别和电容cs1的另一端、电解电容es1的负极、二极管ds的正极相连,连接点接地;

13.基准源模块s2的接地端与电容cs2的另一端相连,连接点接地,基准源模块s2的输出端构成电源变换电路的第二电压输出端。

14.作为本实用新型的一种优选方案,所述微处理器及控制电路的din1端、din2端、 din3端、din4端、din5端、din6端、din7端、din8端分别与调零电路的din1端、 din2端、din3端、din4端,以及调幅电路的din5端、din6端、din7端、din8端一一对应连接;微处理器及控制电路的sclk1端、sclk2端、sync1端、sync2端分别与调零电路的sclk1端、sync1端,以及调幅电路的sclk2端、sync2端一一对应连接。

15.作为本实用新型的一种优选方案,所述微处理器及控制电路包括电容c6、电容c7、电容c8,电阻r12、晶体振荡器y1、微处理器芯片u1;

16.微处理器芯片u1的p1.1口构成微处理器及控制电路的信号输入端;微处理器芯片 u1的rst端和电容c6的一端、电阻r12的一端三者相连,电容c6的另一端对接电源变换电路的第二电压输出端,电阻r12的另一端接地;微处理器芯片u1的rxd端和txd 端构成微处理器及控制电路中用于与上位机通信连接的两个连接端,微处理器芯片u1的 xtal2端和晶体振荡器y1的一端、电容c7的一端三端相连,微处理器芯片u1的xtal1 端和晶体振荡器y1的另一端、电容c8的一端三端相连,电容c7的另一端和电容c8的另一端连接后接地;微处理器芯片u1的gnd端接地;微处理器芯片u1的vcc端对接电源变换电路的第二电压输出端;

17.微处理器芯片u1的p0.0口、微处理器芯片u1的p0.1口、微处理器芯片u1的p0.2 口、微处理器芯片u1的p0.3口、微处理器芯片u1的p0.4口、微处理器芯片u1的p0.5 口、微处理器芯片u1的p0.6口、微处理器芯片u1的p0.7口分别构成微处理器及控制电路的din1端、din2端、din3端、din4端、din5端、din6端、din7端、din8端;微处理器芯片u1的p2.1口、p2.3口、p2.0口、p2.2口分别构成微处理器及控制电路的sclk1 端、sclk2端、sync1端、sync2端。

18.作为本实用新型的一种优选方案,所述微处理器芯片u1为stc12c5a60s2。

19.作为本实用新型的一种优选方案,所述调零电路包括数字电位器芯片r1、数字电位器芯片r2、数字电位器芯片r3、数字电位器芯片r4、电容c1、电容c2、电容c3、电容 c4、电容c5、电解电容e1、电解电容e2、电解电容e3、电阻r9、电阻r10、电阻r11;

20.数字电位器芯片r1的第一电阻端和数字电位器芯片r2的第一电阻端两点相连,连接点构成调零电路的第一电阻端;数字电位器芯片r1的阻值调节端和数字电位器芯片r2的阻值调节端、数字电位器芯片r3的第一电阻端三端相连;数字电位器芯片r3的阻值调节端和数字电位器芯片r4的第一电阻端相连;数字电位器芯片r4的阻值调节端构成调零电路的第二电阻端;

21.数字电位器芯片r1的端和数字电位器r2的端、数字电位器芯片r3 的端、数字电位器芯片r4的端相连,同时数字电位器芯片r1的端连接电阻r9的一端、电容c1的一端,电阻r9的另一端对接电源变换电路的第二电压输出端,电容c1的另一端接地;数字电位器芯片r1的vss端和数字电位器芯片r2的vss 端、数字电位器芯片r3的vss端、数字电位器芯片r4的vss端相连,同时数字电位器芯片r2的vss端连接电解电容e1的正极、电容c2的一端;数字电位器芯片r1的第二电阻端和gnd端、数字电位器芯片r2的第二电阻端和gnd端、数字电位器芯片r3的第二电阻端和gnd端、数字电位器芯片r4的第二电阻端和gnd端分别接地;数字电位器芯片r1的vdd端、数字电位器芯片r2的vdd端、数

字电位器芯片r3的vdd端、数字电位器芯片r4的vdd端分别均对接电源变换电路的第一电压输出端,同时数字电位器芯片r2的vdd端连接电解电容e2的正极、电容c3的一端,电容c3的另一端、电解电容 e2的负极、电容c4的一端相连后接地,电容c4的另一端和数字电位器芯片r2的 ext_cap端相连,数字电位器芯片r2的ext_cap端和数字电位器芯片r1的ext_cap 端、数字电位器芯片r3的ext_cap端、数字电位器芯片r4的ext_cap端相连;数字电位器芯片r1的rdy端、数字电位器芯片r2的rdy端、数字电位器芯片r3的rdy 端、数字电位器芯片r4的rdy端四者相连,同时数字电位器芯片r1的rdy端对接电阻r11的一端,电阻r11的另一端和电阻r10的一端对接电源变换电路的第二电压输出端,电阻r10的另一端连接数字电位器芯片r1的sdo端,同时数字电位器芯片r1的sdo 端和数字电位器芯片r2的sdo端、数字电位器芯片r3的sdo端、数字电位器芯片r4 的sdo端相连;数字电位器芯片r1的端、数字电位器芯片r2的端、数字电位器芯片r3的端、数字电位器芯片r4的端四端相连,该连接点构成调零电路的sync端;数字电位器芯片r1的sclk端、数字电位器芯片r2的sclk端、数字电位器芯片r3的sclk端、数字电位器芯片r4的sclk端四端相连,该连接点构成调零电路的sclk1端;数字电位器芯片r1的din端、数字电位器芯片r2的din端、数字电位器芯片r3的din端、数字电位器芯片r4的din端分别构成调零电路的din1端、 din2端、din3端、din4端,数字电位器芯片r1的v_logic端、数字电位器芯片r2的 v_logic端、数字电位器芯片r3的v_logic端、数字电位器芯片r4的v_logic端分别对接电源转换电路的第二电压输出端;同时数字电位器芯片r2的v_logic端和电容c5的一端、电解电容e3的正极相连,电容c5的另一端和电解电容e3的负极相连后接地。

22.作为本实用新型的一种优选方案,所述调幅电路包括数字电位器芯片r5、数字电位器芯片r6、数字电位器芯片r7、数字电位器芯片r8;

23.数字电位器芯片r5的第一电阻端和数字电位器芯片r6的第一电阻端两点相连,连接点构成调幅电路的第一电阻端;数字电位器芯片r5的阻值调节端和数字电位器芯片r6的阻值调节端、数字电位器芯片r7的第一电阻端三端相连;数字电位器芯片r7的阻值调节端和数字电位器芯片r8的第一电阻端相连;数字电位器芯片r8的阻值调节端构成调幅电路的第二电阻端;

24.数字电位器芯片r5的端与数字电位器芯片r6的端、数字电位器芯片 r7的端、数字电位器芯片r8的端四端相连;数字电位器芯片r5的vss 端与数字电位器芯片r6的vss端、数字电位器芯片r7的vss端、数字电位器芯片r8的 vss端四端相连;数字电位器芯片r5的第二电阻端和gnd端、与数字电位器芯片r6的第二电阻端和gnd端、数字电位器芯片r7的vss端和gnd端、数字电位器芯片r8的 vss端和gnd端分别接地;数字电位器芯片r5的vdd端、数字电位器芯片r6的vdd端、数字电位器芯片r7的vdd端、数字电位器芯片r8的vdd端分别均对接电源变换电路的第一电压输出端;数字电位器芯片r5的ext_cap端、数字电位器芯片r6的ext_cap 端、数字电位器芯片r7的ext_cap端、数字电位器芯片r8的ext_cap端相连;数字电位器芯片r5的rdy端、数字电位器芯片r6的rdy端、数字电位器芯片r7的rdy 端、数字电位器芯片r8的rdy端相连;数字电位器芯片r5的sdo端、数字电位器芯片 r6的sdo端、数字电位器芯片r7的sdo端、数字电位器芯片r8的sdo端相连;数字电位器芯片r5的端、数字电位器芯片r6的端、数字电位器芯片r7的端、数

字电位器芯片r8的端四端相连,连接点构成调零电路的sync2端;数字电位器芯片r5的sclk端、数字电位器芯片r6的sclk端、数字电位器芯片r7的sclk 端、数字电位器芯片r8的sclk端四端相连,连接点构成调零电路的sclk2端;数字电位器芯片r5的din端、数字电位器芯片r6的din端、数字电位器芯片r7的din端、数字电位器芯片r8的din端分别构成调零电路的din5端、din6端、din7端、din8端;数字电位器芯片r5的v_logic端、数字电位器芯片r6的v_logic端、数字电位器芯片r7 的v_logic端、数字电位器芯片r8的v_logic端分别对接电源转换电路的第二电压输出端。

25.作为本实用新型的一种优选方案,所述调零电路包括数字电位器芯片r1、数字电位器芯片r2、数字电位器芯片r3、数字电位器芯片r4;所述调幅电路包括数字电位器芯片 r5、数字电位器芯片r6、数字电位器芯片r7、数字电位器芯片r8;

26.数字电位器芯片r1、数字电位器芯片r2、数字电位器芯片r3、数字电位器芯片r4、数字电位器芯片r5、数字电位器芯片r6、数字电位器芯片r7、数字电位器芯片r8的端相连;数字电位器芯片r1、数字电位器芯片r2、数字电位器芯片r3、数字电位器芯片r4、数字电位器芯片r5、数字电位器芯片r6、数字电位器芯片r7、数字电位器芯片r8的vss端相连;数字电位器芯片r1、数字电位器芯片r2、数字电位器芯片r3、数字电位器芯片r4、数字电位器芯片r5、数字电位器芯片r6、数字电位器芯片r7、数字电位器芯片r8的vdd端相连;数字电位器芯片r1、数字电位器芯片r2、数字电位器芯片r3、数字电位器芯片r4、数字电位器芯片r5、数字电位器芯片r6、数字电位器芯片r7、数字电位器芯片r8的ext_cap端相连;数字电位器芯片r1、数字电位器芯片 r2、数字电位器芯片r3、数字电位器芯片r4、数字电位器芯片r5、数字电位器芯片r6、数字电位器芯片r7、数字电位器芯片r8的v_logic端相连;数字电位器芯片r1、数字电位器芯片r2、数字电位器芯片r3、数字电位器芯片r4、数字电位器芯片r5、数字电位器芯片r6、数字电位器芯片r7、数字电位器芯片r8的gnd端相连;数字电位器芯片 r1、数字电位器芯片r2、数字电位器芯片r3、数字电位器芯片r4、数字电位器芯片r5、数字电位器芯片r6、数字电位器芯片r7、数字电位器芯片r8的rdy端相连;数字电位器芯片r1、数字电位器芯片r2、数字电位器芯片r3、数字电位器芯片r4、数字电位器芯片r5、数字电位器芯片r6、数字电位器芯片r7、数字电位器芯片r8的sdo端相连;

27.数字电位器芯片r4的阻值调节端和数字电位器芯片r8的阻值调节端相连。

28.作为本实用新型的一种优选方案,所述数字电位器芯片r1、数字电位器芯片r2、数字电位器芯片r5、数字电位器芯片r6均为ad5293bruz

‑

20;所述数字电位器芯片r3、数字电位器芯片r4、数字电位器芯片r7、数字电位器芯片r8均为ad5293bruz

‑

50。

29.有益效果:相对于现有技术,本实用新型提供的压力传感器在线标定系统,采用调零电路、调幅电路实现阻值调试,并根据微处理器及控制电路和接收压力传感器标定结果的上位机实现对压力传感器的在线标定,该系统结构简单,且标定效率高。

附图说明

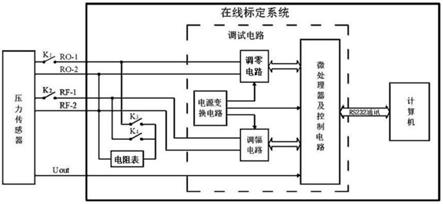

30.图1是本实用新型实施例提供的压力传感器在线标定系统框图;

31.图2是本实用新型实施例提供的电源变换电路的电路示意图;

32.图3是本实用新型实施例提供的微处理器及控制电路示意图;

33.图4是本实用新型实施例提供的数字电位器芯片r1及其外接电路示意图;

34.图5是本实用新型实施例提供的数字电位器芯片r2及其外接电路示意图;

35.图6是本实用新型实施例提供的数字电位器芯片r3的电路示意图;

36.图7是本实用新型实施例提供的数字电位器芯片r4的电路示意图;

37.图8是本实用新型实施例提供的数字电位器芯片r5的电路示意图;

38.图9是本实用新型实施例提供的数字电位器芯片r6的电路示意图;

39.图10是本实用新型实施例提供的数字电位器芯片r7的电路示意图;

40.图11是本实用新型实施例提供的数字电位器芯片r8的电路示意图。

具体实施方式

41.下面结合附图对本实用新型作进一步描述。以下实施例仅用于更加清楚地说明本实用新型的技术方案,而不能以此来限制本实用新型的保护范围。

42.参照图1,本实用新型提供的标定系统,是针对设置有调零电阻位和调幅电阻位的压力传感器进行标定,系统包括电源变换电路、调零电路、调幅电路、微处理器及控制电路、计算机、电阻表,以及开关k1、开关k2、开关k3、开关k4;其中电阻表为对调零电路或调幅电路接入压力传感器中的阻值进行实时测试的电阻表。

43.调零电路的第一电阻端ro

‑

1通过开关k3和电阻表的第一信号输入端相连,并且该相连位置通过开关k1和压力传感器中调零电阻位的一端相连;调零电路的第二电阻端ro

‑

2 和电阻表的第二信号输入端、压力传感器中调零电阻位的另一端相连;调零电路和微处理器及控制电路相连,进行数据交互。

44.调幅电路的第一电阻端rf

‑

1通过开关k4和电阻表的第一信号输入端相连,并且该相连位置通过开关k2和压力传感器中调幅电阻位的一端相连;调幅电路的第二电阻端rf

‑

2 和电阻表的第二信号输入端、压力传感器中调零电阻位的另一端相连;调幅电路和微处理器及控制电路相连,进行数据交互。

45.调零电路的第二电阻端和调幅电路的第二电阻端相连。

46.压力传感器的信号输出端对接微处理器及控制电路的信号输入端;微处理器及控制电路和上位机通信连接;在本实施例中,上位机为计算机。

47.在本实用新型实施例中,电阻表型号为agilent 34401a,用于测试在线标定完成后的调零、调幅电阻值。

48.参照图2,电源变换电路包括用于提供电压vcc1的第一电压输出端,以及用于提供电压vcc2的第二电压输出端,电源变换电路的第一电压输出端和第二电压输出端分别为调零电路和调幅电路中的对应模块,以及微处理器及控制电路中的对应模块供电;进一步的,具体的连接方式如下:

49.电源变换电路包括电源模块s1、电容cs1、电容cs2、电解电容es1、二极管ds;

50.电源模块s1的输入端外接电源电压,外接的电源电压为220vac,电源模块s1的正向电压输出端分别和电容cs1的一端、电解电容es1的正极、二极管ds的负极、基准源模块s2的信号输入端、电容cs2的一端相连,连接点构成电源变换电路的第一电压输出端;

51.电源模块s1的负向电压输出端分别和电容cs1的另一端、电解电容es1的负极、二极管ds的正极相连,连接点接地。

的端、数字电位器芯片r4的端相连,同时数字电位器芯片r1的端连接电阻r9的一端、电容c1的一端,电阻r9的另一端对接电源变换电路的第二电压输出端,电容c1的另一端接地;数字电位器芯片r1的vss端和数字电位器芯片r2的vss 端、数字电位器芯片r3的vss端、数字电位器芯片r4的vss端相连,同时数字电位器芯片r2的vss端连接电解电容e1的正极、电容c2的一端;数字电位器芯片r1的第二电阻端和gnd端、数字电位器芯片r2的第二电阻端和gnd端、数字电位器芯片r3的第二电阻端和gnd端、数字电位器芯片r4的第二电阻端和gnd端分别接地;数字电位器芯片r1的vdd端、数字电位器芯片r2的vdd端、数字电位器芯片r3的vdd端、数字电位器芯片r4的vdd端分别均对接电源变换电路的第一电压输出端,同时数字电位器芯片r2的vdd端连接电解电容e2的正极、电容c3的一端,电容c3的另一端、电解电容 e2的负极、电容c4的一端相连后接地,电容c4的另一端和数字电位器芯片r2的 ext_cap端相连,数字电位器芯片r2的ext_cap端和数字电位器芯片r1的ext_cap 端、数字电位器芯片r3的ext_cap端、数字电位器芯片r4的ext_cap端相连;数字电位器芯片r1的rdy端、数字电位器芯片r2的rdy端、数字电位器芯片r3的rdy 端、数字电位器芯片r4的rdy端四者相连,同时数字电位器芯片r1的rdy端对接电阻r11的一端,电阻r11的另一端和电阻r10的一端对接电源变换电路的第二电压输出端,电阻r10的另一端连接数字电位器芯片r1的sdo端,同时数字电位器芯片r1的sdo 端和数字电位器芯片r2的sdo端、数字电位器芯片r3的sdo端、数字电位器芯片r4 的sdo端相连。

65.数字电位器芯片r1的端、数字电位器芯片r2的端、数字电位器芯片 r3的端、数字电位器芯片r4的端四端相连,该连接点构成调零电路的sync 端;数字电位器芯片r1的sclk端、数字电位器芯片r2的sclk端、数字电位器芯片 r3的sclk端、数字电位器芯片r4的sclk端四端相连,该连接点构成调零电路的sclk1 端;数字电位器芯片r1的din端、数字电位器芯片r2的din端、数字电位器芯片r3 的din端、数字电位器芯片r4的din端分别构成调零电路的din1端、din2端、din3 端、din4端,数字电位器芯片r1的v_logic端、数字电位器芯片r2的v_logic端、数字电位器芯片r3的v_logic端、数字电位器芯片r4的v_logic端分别对接电源转换电路的第二电压输出端;同时数字电位器芯片r2的v_logic端和电容c5的一端、电解电容e3 的正极相连,电容r4的另一端和电解电容e3的负极相连后接地。

66.调幅电路包括数字电位器芯片r5、数字电位器芯片r6、数字电位器芯片r7、数字电位器芯片r8;

67.数字电位器芯片r5的第一电阻端和数字电位器芯片r6的第一电阻端两点相连,连接点构成调幅电路的第一电阻端;数字电位器芯片r5的阻值调节端和数字电位器芯片r6的阻值调节端、数字电位器芯片r7的第一电阻端三端相连;数字电位器芯片r7的阻值调节端和数字电位器芯片r8的第一电阻端相连;数字电位器芯片r8的阻值调节端构成调幅电路的第二电阻端;

68.数字电位器芯片r5的端与数字电位器芯片r6的端、数字电位器芯片 r7的端、数字电位器芯片r8的端四端相连;数字电位器芯片r5的vss 端与数字电位器芯片r6的vss端、数字电位器芯片r7的vss端、数字电位器芯片r8的 vss端四端相连;数字电位器芯片r5的第二电阻端和gnd端、与数字电位器芯片r6的第二电阻端和

gnd端、数字电位器芯片r7的vss端和gnd端、数字电位器芯片r8的 vss端和gnd端分别接地;数字电位器芯片r5的vdd端、数字电位器芯片r6的vdd端、数字电位器芯片r7的vdd端、数字电位器芯片r8的vdd端分别均对接电源变换电路的第一电压输出端;数字电位器芯片r5的ext_cap端、数字电位器芯片r6的ext_cap 端、数字电位器芯片r7的ext_cap端、数字电位器芯片r8的ext_cap端相连;数字电位器芯片r5的rdy端、数字电位器芯片r6的rdy端、数字电位器芯片r7的rdy 端、数字电位器芯片r8的rdy端相连;数字电位器芯片r5的sdo端、数字电位器芯片 r6的sdo端、数字电位器芯片r7的sdo端、数字电位器芯片r8的sdo端相连。

69.数字电位器芯片r5的端、数字电位器芯片r6的端、数字电位器芯片 r7的端、数字电位器芯片r8的端四端相连,连接点构成调零电路的sync2 端;数字电位器芯片r5的sclk端、数字电位器芯片r6的sclk端、数字电位器芯片 r7的sclk端、数字电位器芯片r8的sclk端四端相连,连接点构成调零电路的sclk2 端;数字电位器芯片r5的din端、数字电位器芯片r6的din端、数字电位器芯片r7 的din端、数字电位器芯片r8的din端分别构成调零电路的din5端、din6端、din7 端、din8端;数字电位器芯片r5的v_logic端、数字电位器芯片r6的v_logic端、数字电位器芯片r7的v_logic端、数字电位器芯片r8的v_logic端分别对接电源转换电路的第二电压输出端。

70.数字电位器芯片r1、数字电位器芯片r2、数字电位器芯片r3、数字电位器芯片r4、数字电位器芯片r5、数字电位器芯片r6、数字电位器芯片r7、数字电位器芯片r8的端相连;数字电位器芯片r1、数字电位器芯片r2、数字电位器芯片r3、数字电位器芯片r4、数字电位器芯片r5、数字电位器芯片r6、数字电位器芯片r7、数字电位器芯片r8的vss端相连;数字电位器芯片r1、数字电位器芯片r2、数字电位器芯片r3、数字电位器芯片r4、数字电位器芯片r5、数字电位器芯片r6、数字电位器芯片r7、数字电位器芯片r8的vdd端相连;数字电位器芯片r1、数字电位器芯片r2、数字电位器芯片r3、数字电位器芯片r4、数字电位器芯片r5、数字电位器芯片r6、数字电位器芯片r7、数字电位器芯片r8的ext_cap端相连;数字电位器芯片r1、数字电位器芯片 r2、数字电位器芯片r3、数字电位器芯片r4、数字电位器芯片r5、数字电位器芯片r6、数字电位器芯片r7、数字电位器芯片r8的v_logic端相连;数字电位器芯片r1、数字电位器芯片r2、数字电位器芯片r3、数字电位器芯片r4、数字电位器芯片r5、数字电位器芯片r6、数字电位器芯片r7、数字电位器芯片r8的gnd端相连;数字电位器芯片 r1、数字电位器芯片r2、数字电位器芯片r3、数字电位器芯片r4、数字电位器芯片r5、数字电位器芯片r6、数字电位器芯片r7、数字电位器芯片r8的rdy端相连;数字电位器芯片r1、数字电位器芯片r2、数字电位器芯片r3、数字电位器芯片r4、数字电位器芯片r5、数字电位器芯片r6、数字电位器芯片r7、数字电位器芯片r8的sdo端相连;数字电位器芯片r4的阻值调节端和数字电位器芯片r8的阻值调节端相连。

71.在本实施例中,各数字电位器芯片均为10位、1024抽头,其中数字电位器芯片r1、数字电位器芯片r2、数字电位器芯片r5、数字电位器芯片r6为精调电阻;数字电位器芯片r3、数字电位器芯片r4、数字电位器芯片r7、数字电位器芯片r8为粗调电阻。

72.数字电位器芯片r1、数字电位器芯片r2、数字电位器芯片r5、数字电位器芯片r6 的型号均为ad5293bruz

‑

20;数字电位器芯片r3、数字电位器芯片r4、数字电位器芯片r7、数字电位器芯片r8的型号均为ad5293bruz

‑

50。

73.本实用新型提供的压力传感器在线标定系统,用于对压力传感器进行标定,适用的标定对象包括压力传感器,当对压力传感器进行标定时,压力传感器传输至微处理器及控制电路的数据为电压数据。在对压力传感器进行标定时,采用数字电位器代替外接调试电阻,通过上位机软件直接采集压力传感器输出值,在线匹配合适的调零电阻和调幅电阻,系统结构简单,操作方便,可进行反复使用,提高了压力传感器的标定效率和标定的准确度。

74.以上所述仅是本实用新型的优选实施方式,应当清楚的是,对于本技术领域的普通技术人员来说,在不脱离本实用新型技术原理的前提下,还可以做出若干改进和变形,这些改进和变形也应视为本实用新型的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1