共模抑制比测试系统和方法与流程

共模抑制比测试系统和方法

背景技术:

1.共模抑制比(cmrr)是衡量放大器抑制放大两个放大器输入端共用电压的能力的指标。cmrr被计算为在两个不同共模电压下进行的两次偏移电压测量(vos)的差值除以共模电压的差值。在电子器件制造过程中,需要测试差分放大器、电流感测放大器、仪表放大器和其他电路的共模抑制性能。自动测试电路连接和开关电路的阻抗会影响施加到被测器件(dut)的共模信号,并导致在确定的cmrr中的误差。例如,接触器或插座针(socket pin)和晶圆探测针(probe needle)具有额外的寄生电阻,寄生电阻对于每次插入都不同。清洁测试设备有帮助,但每次插入后清洁触点是不切实际的。此外,开关电路具有寄生电阻,其可能不平衡并导致在确定的cmrr中的进一步的误差。此外,当dut是具有低输入阻抗的高输入偏置器件时,这些问题会加剧,其中不平衡的测试电路电流和寄生电阻会增加cmrr测量误差。

技术实现要素:

2.根据一个方面,一种系统包括接触器和耦合到接触器的测试电路。接触器包括探针对,其中第一导电探针和第二导电探针被布置为耦合到被测器件的相应导电特征部。测试电路包括电压源、第一缓冲器和第二缓冲器。电压源包括提供共模电压信号的第一输出端和耦合到参考节点的第二输出端。第一缓冲器包括耦合到电压源的第一输出端的第一输入端、耦合到第一探针对的第一导电探针的输出端以及耦合到第一探针对的第二导电探针的第二输入端。第二缓冲器包括耦合到电压源的第一输出端的第一输入端、耦合到第二探针对的第一导电探针的输出端以及耦合到第二探针对的第二导电探针的第二输入端。

3.在一个示例中,测试电路包括耦合在第一缓冲器和第一探针对之间的开关,以及耦合在第二缓冲器和第二探针对之间的另一个开关。在另一个示例中,测试电路包括耦合在第一缓冲器的输出端和第一探针对的第一导电探针之间的第一开关、耦合在第一缓冲器的第二输入端和第一探针对的第二导电探针之间的第二开关、耦合在第二缓冲器的输出端和第二探针对的第一导电探针之间的第三开关,以及耦合在第二缓冲器的第二输入端和第二探针对的第二导电探针之间的第四开关。

4.在一个示例中,测试电路包括以电压源的第一输出端为参考的缓冲器供电电路,其中缓冲器供电电路包括耦合到第一缓冲器和第二缓冲器的第一供应节点的第一输出端以及耦合到第一缓冲器和第二缓冲器的第二供应节点的第二输出端。在一个示例中,测试电路包括以参考节点为参考的第二供电电路,其中第二供电电路包括耦合到第三探针对的第一导电探针和第二导电探针的第一输出端,该第三探针对被布置为耦合到连接到dut的第一供应节点的导电特征部,以及耦合到第四探针对的第一导电探针和第二导电探针的第二输出端,该第四探针对被布置为耦合到连接到dut的第二供应节点的导电特征部。

5.在一个示例中,探针对的导电探针是引脚或触点,其被配置为接合集成电路dut的相应导电引脚或引线特征部。在另一个示例中,导电探针是被配置为接合半导体晶圆dut的相应键合焊盘的晶圆探测针。在一个示例中,第一缓冲器和第二缓冲器是运算放大器。

6.根据另一方面,提供了一种测试电路,其包括电压源、第一缓冲器和第二缓冲器以及缓冲器供电电路。电压源包括提供共模电压信号的第一输出端和耦合到参考节点的第二输出端。第一缓冲器包括耦合到电压源的第一输出端的第一输入端、被布置为耦合到接触器的第一导电探针的输出端、以及被布置为耦合到接触器的第二导电探针的第二输入端。第二缓冲器包括耦合到电压源的第一输出端的第一输入端、耦合到接触器的第三导电探针的输出端以及耦合到接触器的第四导电探针的第二输入端。缓冲器供电电路以电压源的第一输出端为参考。缓冲器供电电路包括耦合到第一缓冲器和第二缓冲器的第一供应节点的第一输出端,以及耦合到第一缓冲器和第二缓冲器的第二供应节点的第二输出端。

7.在一个示例中,测试电路包括耦合在第一缓冲器与第一导电探针和第二导电探针中的一个之间的开关,以及耦合在第二缓冲器与第三导电探针和第四导电探针中的一个之间的另一个开关。在另一个示例中,测试电路包括耦合在第一缓冲器的输出端和第一导电探针之间的第一开关、耦合在第一缓冲器的第二输入端和第二导电探针之间的第二开关、耦合在第二缓冲器的输出端和第三导电探针之间的第三开关,以及耦合在第二缓冲器的第二输入端和第四导电探针之间的第四开关。在一个示例中,第一缓冲器和第二缓冲器是运算放大器。

8.根据另一方面,提供了一种方法。该方法包括将接触器的探针对接合到被测器件(dut)的相应导电特征部,将第一缓冲器和第二缓冲器的输出端耦合到接触器的相应第一探针对和第二探针对,以第一幅度施加共模电压信号到第一缓冲器和第二缓冲器的非反相输入端,并且在以第一幅度施加共模电压信号时在接触器的另一探针对处测量dut的第一输出电压信号。该方法还包括将共模电压信号调整到不同的第二幅度,在以第二幅度施加共模电压信号时测量dut的输出电压信号,以及基于测量的输出电压信号以及共模电压信号的第一幅度和第二幅度计算dut的共模抑制比。

9.在一个示例中,该方法还包括闭合在第一缓冲器和第一探针对之间的开关以及闭合在第二缓冲器和第二探针对之间的另一个开关。在另一个示例中,该方法还包括闭合在第一缓冲器的输出端和第一探针对的第一导电探针之间的第一开关、闭合在第一缓冲器的反相输入端和第一探针对的第二导电探针之间的第二开关、闭合在第二缓冲器的输出端和第二探针对的第一导电探针之间的第三开关,以及闭合在第二缓冲器的反相输入端和第二探针对的第二导电探针之间的第四开关。

10.在一个示例中,该方法还包括用以共模电压信号为参考的供应电压为第一缓冲器和第二缓冲器供电。

附图说明

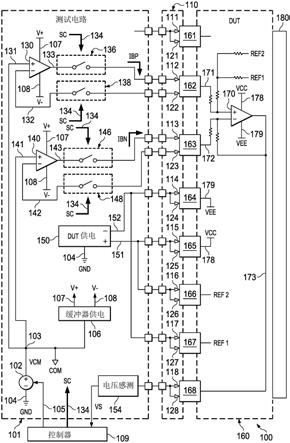

11.图1是测试系统的示意图,该系统包括测试电路、具有导电探针对的接触器、两个开关和用于每个dut输入连接的缓冲器,以自动测试封装电子器件或包含电子电路的晶圆管芯区域的共模抑制比。

12.图2是根据另一个实施例的具有导电探针对、一个开关和用于每个dut输入连接的缓冲器的另一测试系统的示意图。

13.图3是示出开关电阻和接触电阻的图1的测试系统的电气模型的示意图。

14.图4是用于测试集成电路电子器件的最终测试系统实施方式的系统图。

15.图5是用于测试集成电路电子器件的最终测试系统实施方式的另一系统图。

16.图6是根据另一方面的共模抑制比测试方法的流程图。

17.图7是用于测试经处理的半导体晶圆的电子器件的晶圆探针测试系统实施方式的系统图。

具体实施方式

18.在附图中,相同的附图标记始终指代相同的元件,并且各种特征部不一定按比例绘制。此外,术语“耦合”包括间接或直接的电或机械连接或其组合。例如,如果第一器件耦合到第二器件或与第二器件耦合,则该连接可以是通过直接电连接,或通过经由一个或多个中间器件和连接的间接电连接。各种电路、系统和/或部件的一个或多个操作特性在功能的上下文中被描述,这些功能在某些情况下由当电路被供电和操作时各种结构的配置和/或互连产生。

19.图1示出了具有包括的测试电路101的测试系统100。测试电路101包括电压源102,其具有提供共模电压信号vcm的第一输出端103,以及耦合到参考节点104的第二输出端。在一个示例中,参考节点104是接地参考,并且共模电压信号vcm是以参考节点104的电压(例如,gnd)为参考的dc电压。电压源102具有允许对共模电压信号vcm的幅度和/或极性进行外部控制的控制输入端105。测试电路101还包括以电压源102的第一输出端103为参考的缓冲器供电电路106。缓冲器供电电路106包括第一输出端107,其提供以电压源102的共模电压信号vcm为参考(例如,以图1中的信号共用电压com为参考)的第一(例如,正)供应电压信号v+,其中v+相对于vcm为正)。此外,缓冲器供电电路106包括提供第二供应电压信号v

‑

(例如,相对于vcm为负)的第二输出端108。系统100还包括控制器109,其向电压源102的控制输入端105提供控制信号。

20.此外,系统100包括接触器110。在一个示例中,接触器110是用于测试安装的集成电路dut以进行最终测试的插座。在另一个示例中,接触器110是晶圆探针,用于测试用于晶圆探针测试的已处理半导体晶圆dut的被探测的管芯区域。在一个示例中,测试电路101是或包括具有所描述的电路系统和一个或多个连接器的一个或多个印刷电路板,该连接器被布置或以其他方式适于连接到接触器110的配合连接器以提供图1中所示的电互连。

21.接触器110包括多个探针对。在一个示例中的探针对提供开尔文触点以允许通过第一导电探针(例如,称为力触点)单独施加电压信号,以及通过第二导电探针(例如,称为感测触点)感测所探测的导电特征部的电压或电流。单独的探针对包括被布置为耦合到dut的相应导电特征部的第一导电探针和第二导电探针。当接触器110与dut接合时,第一导电探针和第二导电探针均与dut的相关联的导电特征部机械接合并直接电耦合到该导电特征部。图1中的一个示例探针对111/121包括导电探针111和导电探针121。探针对112/122(在此称为第一探针对)包括导电探针112和导电探针122,探针对113/123(在此称为第二探针对)包括导电探针113和导电探针123。在所图示示例中,探针对111/121与未连接到dut的任何电路的安装的dut的导电特征部介接(interface),并且可以称为第三探针对111/121,尽管位于接触器110上以接合被接合的封装电子器件的第一引脚。第四探针对114/124包括导电探针114和导电探针124。类似地,第五探针对115/125包括导电探针115和导电探针125,第六探针对116/126包括导电探针116和导电探针126,第七探针对117/127包括导电探针

117和导电探针127,并且第八探针对118/128包括导电探针118和导电探针128。在图1的示例中,接触器110包括八个探针对111/121、112/122、113/123、114/124、115/125、116/126、117/127和118/128以与dut的八个导电特征部(例如8引脚ic dut)介接。在另一个实施方式中,接触器110具有少于八个探针对。在又一个实施方式中,接触器110具有多于八个探针对。

22.测试电路101还包括缓冲器,用于将dut的输入端与电压源102介接以进行dut的共模测试。第一缓冲器130包括第一输入端131(例如,非反相输入端)、第二输入端132(例如,反相输入端)、输出端133、耦合到缓冲器供电电路106的第一输出端107的第一(例如,正)供应节点,以及耦合到缓冲器供电电路106的第二输出端108的第二供应节点。第一输入端131耦合到电压源102的第一输出端103。第一缓冲器130的输出端133被布置为耦合到接触器110的第一探针对112/122的第一导电探针112,并且第二输入端132被布置为耦合到第一探针对112/122的第二导电探针122。在操作中,缓冲器输出端133向连接的dut的正(例如,非反相)输入端提供偏置电流ibp。在一个示例中,第一缓冲器130的输出端133直接耦合到第一探针对112/122的导电探针112并且缓冲器130的第二输入端132直接耦合到第一探针对112/122的导电探针122。

23.还参考图2,在另一个示例中,一个或多个开关耦合在第一缓冲器130和第一探针对112/122之间,在第一缓冲器130的输出电路支路和第一缓冲器130的第二输入电路支路中的任一者或两者中。如果包括,则一个或多个开关有助于使用缓冲器来测试单个ic插入或晶圆探针中的多个电路部件与dut触地(touchdown)互连。一个或多个开关具有控制输入端134并且在一个示例中根据来自控制器109的开关控制信号sc来操作。图1中的示例测试电路101包括耦合在第一缓冲器130的输出端133和第一探针对112/122的导电探针112之间的第一开关136,以及耦合在第一缓冲器130的第二输入端132和第一探针对112/122的导电探针122之间的第二开关138。开关136和138各自具有用于根据开关控制信号sc进行开关操作的控制输入端134。

24.测试电路101还包括第二缓冲器140以将dut的第二输入端与电压源102的第一输出端103介接以进行共模测试。在一个示例中,相应的第一缓冲器130和第二缓冲器140是运算放大器(op

‑

amp)。在一个示例中,缓冲器130和140是具有低偏移和低偏置电流规格的低噪声op

‑

amp,例如来自德克萨斯仪器股份有限公司的opa 2210运算放大器电路。在另一个示例中,缓冲器130和140是其他形式的缓冲放大器电路。缓冲器供电电路106的第一输出端107耦合到第一缓冲器130和第二缓冲器140的第一供应节点,并且第二输出端108耦合到第一缓冲器130和第二缓冲器140的第二供应节点,如图1中所示。

25.第二缓冲器140包括耦合到电压源102的第一输出端103的第一输入端141。如图1中所示,相应的缓冲器130和140的输入端131和141星形连接到电压源102的第一输出端103。从第一输出端103到输入端131和141的单独连接,以及从第一输出端103到缓冲器供电电路106的连接是彼此分开的,并且优选地具有相等的长度和阻抗。第二缓冲器140还包括耦合到接触器110的第二探针对113/123的导电探针113的输出端143,以及耦合到第二探针对113/123的导电探针123的第二输入端142。在操作中,第二缓冲器输出端143向连接的dut的负(例如,反相)输入端提供偏置电流ibn。第二缓冲器140还包括耦合到缓冲器供电电路106的第一输出端107的第一(例如,正)供应节点,以及耦合到缓冲器供电电路的第二输出

端108的第二(例如,负)供应节点。在一个示例中,第二缓冲器140的输出端143直接耦合到第二探针对113/123的导电探针113并且第二缓冲器140的第二输入端122直接耦合到第二探针对113/123的导电探针123。

26.在另一个示例中,一个或多个开关耦合在第二缓冲器140和第二探针对113/123之间。一个或多个开关具有控制输入端134并且根据开关控制信号sc进行操作。图1的示例包括根据开关控制信号sc操作的第三开关146和第四开关148。第三开关146耦合在第二缓冲器140的输出端143和第二探针对113/123的导电探针113之间。第四开关148耦合在第二缓冲器140的第二输入端142和第二探针对113/123的导电探针123之间。在操作中,开关136、138、146和148允许缓冲器130和140根据来自控制器109的开关控制信号sc选择性地连接到相应的探针对112/122和113/123或从它们断开。

27.图2示出了系统100的另一个实施例,其中省略了图1的开关138和148。在该示例中,单个开关136耦合在第一缓冲器130的输出端133和第一探针对112/122的导电探针112之间,并且第一缓冲器130的第二输入端132直接耦合到第一探针对112/122的导电探针122。而且,单个开关146耦合在第二缓冲器140的输出端143和第二探针对113/123的导电探针113之间,并且第二缓冲器140的第二输入端142直接耦合到第二探针对113/123的导电探针123。在另一个实施方式中,在每个缓冲器电路中的第二输入端上提供单个开关(例如,包括图1中的开关138和148)并且缓冲器输出端133和143直接耦合到相应的导电探针112和113(例如,省略了图1的开关136和146)。在又一实施方式中,省略了所有开关136、138、146和148,缓冲器输出端133和143直接耦合到相应的导电探针112和113,并且反相输入端132和142直接耦合到相应的导电探针122和123。

28.在图1和图2中的示例测试电路101包括被配置为为连接的dut的电路系统(例如,被测试的放大器)供电的第二供电电路150。第二供电电路150以参考节点104为参考。第二供电电路150包括提供正dut供应电压信号vcc(例如,相对于参考节点104的电压gnd的正dc电压)的第一输出端151。第一输出端151耦合到探针对115/125的导电探针115和125。第二供电电路150的第二输出端152提供相对于参考节点104的电压gnd的负dc供应电压信号vee。第二输出端152耦合到探针对114/124的导电探针114和124。在其他实施方式中,dut 160由正电源和地(例如,5v和0v)供电而没有任何负(低于地)电源。

29.图1和图2中的测试电路101还包括电压感测电路154,其具有耦合到最终探针对118/128的导电探针118和128的输入端。电压感测电路154包括向控制器109提供感测的电压信号vs的输出端,该信号表示施加到电压感测电路154的输入端的电压。在一个示例中,电压感测电路154包括模拟信号调节电路系统、缓冲放大器、电平移位器等,以向控制器109提供模拟感测电压信号vs。在另一个示例中,电压感测电路144包括模数转换电路系统,其向控制器109提供数字感测电压信号vs。

30.图1和图2示出了与dut 160接合的系统100。在所图示的示例中,dut 160包括导电特征部161、162、163、164、165、166、167和168。在该示例中的导电特征部161未连接到dut 160的电子电路。在所图示的示例中,导电特征部161是未连接到dut 160的任何电路的封装电子器件dut 160的第一引脚,并且可以被称为dut 160的第三导电特征部。导电特征部162耦合到示例dut 160的电子电路系统并且在此处被称为第一导电特征部。导电特征部163在此处被称为第二导电特征部。第四导电特征部164、第五导电特征部165、第六导电特征部

166、第七导电特征部167和第八导电特征部168耦合到示例dut 160的电子电路系统。探针对111/121、112/122、113/123、114/124、115/125、116/126、117/127和118/128的导电探针与dut 160的相应的导电特征部161、162、163、164、165、166、167和168接合。dut 160包括一个或多个电路,其输入端和输出端将经由测试电路101的电压源102和缓冲器130和140测试共模抑制比性能。在用于集成电路最终测试的一个示例中,dut 160是ic或其他封装的电子器件,并且导电探针111

‑

118和121

‑

128是引脚或触点,其被配置为接合集成电路dut 160(例如,下面的图5)的相应的导电引脚或引线特征部161、162、163、164、165、166、167、168。在用于处理的半导体晶圆dut的晶圆探针测试的另一个实施方式中,导电探针111

‑

118和121

‑

128是晶圆探测针,其被配置为接合半导体晶圆dut 160(例如,下面的图7)的相应的键合焊盘161、162、163、164、165、166、167、168。

31.图1和图2示出了接触器110接合8引脚仪表放大器ic(例如可从德克萨斯仪器股份有限公司获得的ina240)的示例。图1和图2中的示例dut 160包括耦合到电阻器网络的放大器170、耦合到第一导电特征部162的第一输入端171、耦合到第二导电特征部163的第二输入端172、耦合到第八导电特征部168的输出端173和耦合到dut 160的相应的第六导电特征部166和第七导电特征部167的参考连接(例如,ref2和ref1)。此外,放大器170具有分别耦合到dut 160的相应导电特征部165和164的正电源轨连接178和负电源轨连接179,以从第二供电电路150接收dut供应信号vcc和vee。图1和图2还示意性地示出了使接触器110的导电探针111

‑

118和121

‑

128接合并电耦合到dut 160的导电特征部161、162、163、164、165、166、167、168的处理器(handler)装置180。

32.此示例dut 160用于高侧或低侧电流感测中的电流感测,例如用于电源转换系统应用。dut示例160在操作期间具有低输入阻抗和相应的高输入偏置电流。此外,由于dut输入电路系统的电阻网络结构,偏置电流随着施加到输入端的共模电压的增加而增加。结果,在没有缓冲器130和140的情况下通过将共模电压源102直接连接到dut输入特征部162和163来测量cmrr导致共模抑制性能的不准确测量。

33.在所图示的测试系统100中,施加的共模电压信号vcm由测试电路缓冲器130和140缓冲,并且缓冲器130和140由以共模电压vcm为参考的缓冲器供应信号v+和v

‑

供电。在该示例中,第二供电电路150的第一输出端151被布置为通过测试电路101和其接口通过接触器110耦合到连接到dut 160的第一供应节点178的导电特征部165。第二输出端152被布置为耦合到连接到dut 160的第二供应节点179的导电特征部164。此外,第一缓冲器输出端133耦合到第一探针对112/122的第一导电探针112,并且探针对112/122被布置为耦合到连接到dut 160的第一输入节点171的第二导电特征部162。此外,第二缓冲器140的输出端143耦合到第二探针对113/123的第一导电探针113,其被布置为耦合到连接到dut 160的第二输入端节点172的第二导电特征部163。

34.还参考图3,在系统100中的缓冲器130和140促进了dut 160的共模抑制性能的准确cmrr测试和测量,甚至用于具有低输入阻抗和高输入偏置电流的放大器dut电路,甚至用于改变dut 160与接触器110的互连的接触电阻。图3示出了图1的测试系统的电气模型的示意图,其具有相关联的开关电阻rsfp、rssp、rsfn和rssn,以及接触电阻rcfp、rcsp、rcfn和rcsn。电阻命名法rxyz包括r代表电阻,x代表s=开关、c=接触,y代表f=力、s=感测,z代表p=正输入、n=负输入。在图示的配置中,包括的相应开关136和138的正输入开关电阻

rsfp和rssp和与dut 160的导电特征部(例如,引脚)162接合的第一探针对112/122的相应导电探针112和122的接触电阻rcfp和rcsp串联。此外,包括的相应开关146和148的负输入开关电阻rsfn和rssn和与dut 160的导电特征部(例如,引脚)163接合的第二探针对113/123的相应导电探针113和123的接触电阻rcfn和rcsn串联。

35.测试系统100为接触器110提供开尔文触点对、两个开关和用于dut输入端连接171和172中的每一个的缓冲器,以自动测试集成电路或其他封装电子器件的共模抑制比,或包含电子电路的晶圆管芯区域的共模抑制比。在一个示例中的共模抑制比测试包括测量施加到dut输入端171和172的两个不同共模电压下的偏移电压。通过向缓冲器130和140施加共模电压信号vcm并经由电压感测电路154在输出引脚168处进行测量来进行偏移电压测量。缓冲器130和140容纳在测试电路101中可能相等或可能不相等的寄生开关电阻rsfp和rsfn,以及寄生接触器(插座)引脚电阻rcfp、rcsp、rcfn和rcsn,它们可以对于每次插入或触地而变化。这有利于与在每次插入或触地之后未清洁(clean)的接触器110一起使用,以在晶圆探针和/或最终测试时进行准确的cmrr测试,甚至用于具有高输入偏置电流的dut电路。

36.在每个缓冲器电路中具有一个开关的测试系统100(例如,图2)中,即使在dut偏移电压vos=0的情况下,所施加的偏移出现为(ibp*rcfp)

‑

(ibn*(rsfn+rcfn))。测量受到rsfn的系统性损害,并且随机受到rcfn和rcfp的损害。为了帮助减少这种误差,使用了第二开关(例如,如图1和图3中所示),以便输入端171和172看到近似对称的阻抗。即使dut偏移电压vos=0,实际偏移电压出现为(ibp*(rsfp+rcfp))

‑

(ibn*(rsfn+rcfn))。增加的开关电阻rsfp有助于消除由电阻rsfn引起的系统误差,通常会降低系统误差(ibp

‑

ibn)*(rsfp

‑

rsfn),但由于寄生接触电阻通常会随着每次插入或触地而改变,随机误差仍然存在。因此,尽管测量现在对rsfn和rsfp的失配敏感,而不是对rsfn本身敏感(通常会降低整体误差),但由于接触电阻的变化,没有缓冲器130和140的cmrr测试仍然经历不准确性。

37.测试电路101通过以下操作进一步改善测量准确性:将缓冲器130和140星形连接到电压源102的输出端103处的共模电压vcm,并且将缓冲器输出端133和143耦合到相应的导电探针(例如,力触点)112和113,而缓冲器反相输入端(例如,反馈端子)132和142耦合到相应的导电探针(例如,感测触点)122和123。在该配置中,dut电路的输入电路偏置电流ibp和ibn由相应的缓冲器130和140提供。

38.缓冲器电路的负反馈回路感测相应导电探针(例如,感测触点)处的电压,并且缓冲器130和140适当地调整其相应输出端133和143处的电压以缓冲共模电压信号vcm。因为很少电流(例如,微微安)流入缓冲器130和140的高阻抗输入端131、132、141和142,寄生开关电阻rsfp和rsfn以及接触电阻rcfp、rcsp、rcfn和rcsn贡献可忽略的误差。相应缓冲放大器130和140上的小ibp和ibn意味着感测线上的电阻(rssp、rcsp、rssn和rcsn)贡献可忽略的误差。力线上的电阻具有经过它们的dut 160的ib,因此它们仍然具有它们两端的电压降,尽管这些电压降由缓冲器130和140补偿。如果仪表放大器dut偏置电流在共模电压信号vcm的两个不同幅度的施加之间改变,则缓冲器130和140提供相应的电流ibp和ibn,而对输出电压测量准确度几乎没有影响或没有影响。在这点上,dut 160的两个输入端171和172之间的任何差分偏移都不会随着施加的共模电压信号vcm的变化而变化,并且dut输出vs的测量变化是dut 160的cmrr的结果。

39.在该示例中将缓冲器130和140耦合到仪表放大器dut 160的输入端171和172防止偏置电流ibp和ibn在共模抑制比测试中引起误差。当共模电压信号vcm在测试期间改变时,如果缓冲器130和140不存在,则dut 160传导更多偏置电流,这将导致开关和接触电阻引起的误差。在所描述的示例中,缓冲器130和140通过由相应探针对112/122和113/123提供的开尔文触点供应任何需要的偏置电流ibp和/或ibn。此外,利用以共模电压信号vcm为参考的来自浮动缓冲器供电电路106的功率为缓冲器130和140供电防止缓冲器130和140在测试期间使用的两个共模电压幅度下改变它们的偏移,并且通过两点cmrr测量抵消了任何缓冲器偏移。此外,在所图示的示例中,缓冲器130和140以及缓冲器供电电路106与vcm电压源输出端103的星形连接有助于确保电压源输出端103与缓冲器130和140之间的任何寄生电阻不会产生由于偏置电流ibp和ibn变化而引起的误差,并在不同的施加的共模电压幅度下保持任何偏置误差一致。

40.在测试电路中没有缓冲器130和140的不同方法是代之以使用开尔文接触引脚对dut输入端171和172处的输入电压进行精确测量,并在cmrr计算中考虑测量的电压。然而,这种测量将需要达到单微伏准确度,并且将需要测试时间和/或额外的测试器资源。例如,串行测量通常会增加35到50毫秒的测试时间,并且仍然存在一些测量不确定性。使用具有缓冲器130和140的示例测试电路101去掉了这些测量并减少了测试时间。在一个示例中,测试系统100包括具有指定最大测试时间的eagle test systems ets88高性能测试设备,并且使用缓冲器130和140可以减少15%或更多的测试时间,同时提高cmrr测量的准确性和精确性。

41.图4示出了用于测试集成电路电子器件dut 160的系统100的最终测试实施方式的示例实施方式。在图4中的系统实施方式包括接触器110以与如上所描述的ic dut 160介接。该系统实施方式包括带有介接板402的测试柜400,该介接板402通过线缆404连接到负载板406。负载板406安装在接触器介接板408上,并且接触器110连接到接触器介接板408。处理器180包括控制接触器110与dut 160的电气介接的支撑臂182。在该示例中,图1

‑

图3的测试电路101在测试柜400、介接板402、负载板406和/或接触器介接板408中的一个或多个中实施。在一个实施方式中,测试柜和介接板402包括eagle test systems ets

‑

88高性能设置。

42.在该示例中,在图1

‑

图3中的测试器电压源102包括在测试柜400或介接板402中,并通过从测试柜400到介接板402的连接提供编程的共模电压信号vcm。介接板402将来自测试柜400的共模电压信号vcm传递到介接板402的线缆连接器而不电气改变信号vcm,并且线缆404将共模电压信号vcm传递到负载板406。在一个示例中,负载板406包括缓冲器供电电路106,例如,使用一个或多个dc到dc转换器来实施,用于正和负浮动电源,其提供分别高于和低于共模电压信号vcm的电压信号v+和v

‑

(例如,v+=vcm+15v和v

‑

=vcm

‑

15v)。共模电压信号vcm到电压源102(例如,图1

‑

图3)的输出端103的信号和功率连接在到相应dc/dc转换器参考和开尔文缓冲器非反相输入端131和141的星形布局连接中是分开的。接触器介接板408是可变的,以允许不同的接触器110用于不同的dut ic占用面积(footprint),以使用相同的负载板406进行测试。在一个示例中,缓冲器130和140在负载板406上实施,并且开关136、138、146和148(如果包括的话)在接触器介接板408上实施。在一个实施方式中,接触器110是具有探针对的集成电路插座,以将测试电路101的力和感测互连从接触器介接板408

介接到安装的ic dut 160的引脚或引线161

‑

168。处理器180和相关联的支撑臂182在测试期间将dut 160保持或以其他方式支撑在接触器110上,并且在测试之间将dut 160移向和移离接触器110。

43.图5示出了用于测试集成电路电子器件dut 160的系统100的示例最终测试实施方式的另一视图。系统100包括如上所述的控制器109、测试电路101、接触器110、处理器180和支撑臂182。在该示例中,支撑臂182通过通过真空管或喷嘴500施加的真空压力来接合并支撑ic dut 160以接合dut 160的ic封装的顶部表面。该示例中的处理器180包括定位器装置502和真空泵504。真空泵504通过喷嘴500施加真空压力以选择性地接合或释放dut 160,并且定位器装置502控制臂182、喷嘴500和接合的dut 160的定位以用于自动器件电气测试。当与接触器110接合时,dut 160的引线161

‑

168被接触器110的导电探针111

‑

118和121

‑

128(开尔文触点)接触。在制造过程中的器件封装之后,处理器180促进在自动化过程中接合、移动和测试dut 160。在一个示例中,处理器180的定位器装置502以重复的顺序操作以从托盘或载体结构(未示出)拾取dut 160,将dut 160传送到具有接触器110的测试夹具,将dut 160与接触器110接合以用于自动器件电气测试,包括共模抑制比测试,并将测试的dut 160返回到载体结构。定位器装置502可以包括线性或旋转伺服器、定位器致动器和机械支撑结构以将支撑臂182移动到三维空间中的任何位置和取向。控制器109控制测试电路101和定位器装置502的操作。

44.图6示出了可以在图1

‑

图5的系统100中实施的示例电子器件测试方法600。在一个示例中,测试系统100的控制器109为一系列器件测试循环中的每一个实施方法600。方法600包括在602处将接触器探针对接合到dut 160的相应导电特征部。在一个示例中,图5中的控制器109致使定位器装置502使用来自真空泵504的真空压力将dut 160与喷嘴500接合,并且沿着图5中的

‑

z方向向下平移接合的dut 160使得接触器探针对111/121、112/122、113/123、114/124、115/125、116/126、117/127和118/128接合到dut 160的相应的导电特征部161、162、163、164、165、166、167和168。在图4和图5的ic最终测试示例中,在一个示例中,在602处的处理包括将接触器110的引脚或触点接合到集成电路dut 160的相应导电引脚或引线特征部161、162、163、164、165、166、167或168。在半导体晶圆探针测试实施方式(例如,下面的图7)中,在602处的处理包括将接触器110的晶圆探测针对111/121、112/122、113/123、114/124、115/125、116/126、117/127和118/128接合到半导体晶圆dut 160的相应键合焊盘161、162、163、164、165、166、167、168。

45.方法600在604处继续,其中闭合缓冲器130和140与探针对之间的测试电路开关(例如,上述包括的任何开关136、138、146和/或148)以将缓冲器输出端133和143耦合到并且将反相输入端132和142耦合到接触器110的相应的第一探针对112/122和第二探针对113/123。在测试电路101不包括任何开关136、138、146或148的情况下,省略图6中的步骤604。方法600在606处继续,其中利用以共模电压信号vcm为参考的供应电压v+和v

‑

为第一缓冲器130和第二缓冲器140供电。在一个示例中,这包括启用上述图1

‑

图3的缓冲器供电电路106。在另一个实施方式中,缓冲器130和140在测试任何器件之前被供电,然后缓冲器将在测试之后断电以减少测试时间。在这点上,缓冲器130和140可以在dut测试之间加电,只要vcm接地,因此新的dut没有在高电压上接合(例如,触地)。在该实施方式中,仅vcm在dut 160之间移动并且缓冲器电源可以在所有dut被测试的持续时间内保持供电。

46.在608处,共模电压信号vcm以第一幅度被施加到非同相缓冲器输入端131和141,并且在610处,测量dut 160的第一输出电压信号vs,同时以第一幅度施加共模电压信号vcm。方法600包括以不同施加的共模电压信号幅度的多次测量,并且控制器109在612处判断共模抑制比测试是否完成。如果需要另一次测量(在612处为否),则控制器在614处将共模电压信号vcm调整到不同的第二幅度,并且在608处将调整后的共模电压信号vcm施加到非反相缓冲器输入端131和141。方法600在610处继续,其中测量dut输出电压信号vs,同时以第二幅度施加共模电压信号vcm。一旦获得所需数量的两个或更多个测量(在612处为是),在616处控制器109基于测量的输出电压信号vs和所施加共模电压信号vcm的两个或更多个相应幅度(例如,作为两个电压测量值的差除以第一共模电压信号幅度和第二共模电压信号幅度的差)来计算dut 160的共模抑制比cmrr。在618处,执行接合的dut 160的任何期望的进一步电气测试。一旦完成所有测试,控制器109在620处使用定位器装置502和真空泵504将被测试的dut 160存放在产品载体(未示出)中,并且在622处接合另一个dut 160以进行测试。然后对每个要测试的连续dut 160重复所图示的过程600。

47.图7示出了图1

‑

图3的系统100的晶圆探针测试系统实施方式,用于测试经处理的半导体晶圆dut 160的管芯区域的电子器件。在一个示例中,晶圆dut 160在管芯分离或切单之前包括多个器件管芯区域,并且每个器件管芯区域具有要在系统中测试的一个或多个电路,例如上述图1

‑

图3中所示的仪表放大器电路。在该示例中,探针对(例如,图1

‑

图3中的111/121、112/122、113/123、114/124、115/125、116/126、117/127和118/128)的导电探针是晶圆探测针,其被配置为接合半导体晶圆dut 160的相应键合焊盘导电特征部161、162、163、164、165、166、167和168。该示例中的晶圆dut 160具有多个管芯区域700,每个管芯区域包括导电特征部161、162、163和164。晶圆dut 160的图示部分示出了管芯区域700中的三个的部分,其中接触器110被定位成接合管芯区域700中的单个和相关联的导电特征部161

‑

164。在一个示例中的操作中,控制器109连续地定位支撑臂182以控制接触器110在半导体晶圆dut 160的相应管芯位置处的电介接以根据上述方法600依次执行相应管芯位置的电路的共模抑制比测试(以及可能的其他电气测试)。

48.以上示例仅仅是本公开的各个方面的几种可能的实施方式的说明,其中本领域的其他技术人员在阅读和理解本说明书和附图后将想到等效的改变和/或修改。在权利要求的范围内,在所描述的示例中的修改是可能的,并且其他实施方式也是可能的。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1