一种应用于自动测试机SOC芯片并行测试切换方法与流程

一种应用于自动测试机soc芯片并行测试切换方法

技术领域

1.本发明涉及半导体测试技术领域,具体地说是一种应用于自动测试机soc芯片并行测试切换方法。

背景技术:

2.系统级芯片(system

‑

on

‑

chip)是指在同一颗芯片内部集成了多个不同功能的内核,每个内核都有自己的设计参数和检验指标,内核之间通过内部总线实现逻辑和数据交互。例如:机顶盒处理器就是一类典型的soc芯片,其内部包含了强大的微处理器内核、以太网内核、音频信号编解码内核、视频信号编解码内核、内部存储器内核、外扩存储器控制内核、电源管理内核等。

3.不同功能内核运转的时钟速度不尽相同,例如:微处理器的外部串行数据通讯端口运行在25mhz(时钟周期为40.0ns),而其以太网端口却是基于24mhz运行(时钟周期为41.667ns)。音频编解码需要数字测试通道和音频模拟信号源加采集器的配合,而视频编解码需要数字测试通道和高频模拟信号发生器加采集器的配合。

4.这类复杂芯片的测试,要求自动测试机首先具有多种测试资源,包括可编程电源(dps)、直流参数测量单元(pmu)、高速数字测试通道、至少两个高稳定度低抖动的可编程时钟源、高解析度音频模拟信号发生器(hr

‑

awg)、高解析度音频模拟信号采集器(hr

‑

dtz)、高速模拟信号发生器(hs

‑

awg)、高速模拟信号采集器(hs

‑

dtz)等。

5.部分此类复杂soc芯片的架构设计上,考虑到测试成本和测试便利性,会允许内核可以被配置为独立工作与测试模式。这就给多内核的并行测试提供了可行性。

6.传统的自动测试机针对这一类复杂soc芯片的测试,一般都是将需要测试的不同内核的功能排序后,由自动测试机一个一个测试项的串行执行。主要原因在于,配置为独立工作测试模式的内核,由于功能的不同,会需要该内核端口对应的测试机资源工作于不同频率(或不同周期长度)的状态。举例来说,数据接口和mcu端口需要工作与25mhz(t1=40ns周期),利用这个端口去配置以太网内核进入测试模式。同时,以太网端口却需要24mhz(t2=41.667ns周期)。t1和t2无法找到1以外的最小公约数,这就对要求自动测试机的两组数字测试通道分别工作与不同的时钟域。很多自动测试机无法实现这样的功能,就只能串行测试。

7.当几个内核的工作频率无法基于同一个系统时钟分频而来的时候,就必须要分段来串行测试,每一段测试让测试机配置成某一特定测试频率,在下一段测试前需要切换系统时钟。不能并行测试,会延长测试时间,增加测试成本。串行测试,也导致无法测试两个内核之间数据通讯,必须要增加额外的测试项目去验证内核间通讯。

技术实现要素:

8.本发明为克服现有技术的不足,提供一种应用于自动测试机soc芯片并行测试切换方法,通过时钟域切换电路切换到模拟时钟域,这样就可以让两个端口在不同频率下同

时启动逻辑测试。

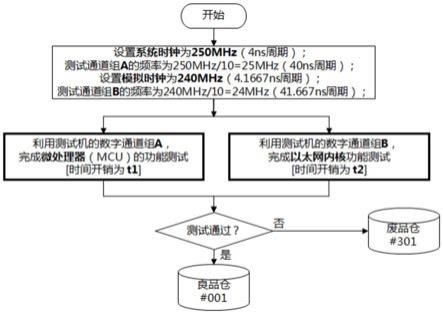

9.为实现上述目的,设计一种应用于自动测试机soc芯片并行测试切换方法,包括测试载具板、数字测试通道、时钟域切换电路,其特征在于:具体流程如下:s1:在测试载具板上的数据接口及mcu端连接一组数字测试通道a,在测试载具板上的以太网接口端连接一组数字测试通道b,数字测试通道b上连接时钟域切换电路;s2:设置系统时钟周期为250mhz,则数字测试通道组a的频率为250 mhz/10=25 mhz;设置模拟时钟周期为240 mhz,则数字测试通道组b的频率为240mhz/10=24 mhz;s3:测试开始时,利用数字测试通道组a对被测soc芯片完成微处理器mcu的功能测试;利用数字测试通道组b对被测soc芯片完成以太网内核的功能测试;s4:两项测试完成后,判断测试是否通过,是则被测soc芯片认定合格;否则被测soc芯片认定不合格。

10.所述的时钟域切换电路可以连接到音频内核端的数字测试通道上。

11.所述的时钟域切换电路可以连接到视频内核端的数字测试通道上。

12.所述的时钟域切换电路可以连接到数据接口及mcu端的数字测试通道上。

13.所述的音频内核端、视频内核端、数据接口及mcu端设置在测试载具板上。

14.所述的时钟域切换电路通过时钟切换芯片lmk01020实现的时钟域切换。

15.本发明同现有技术相比,提供一种应用于自动测试机soc芯片并行测试切换方法,通过时钟域切换电路切换到模拟时钟域,这样就可以让两个端口在不同频率下同时启动逻辑测试。

16.自动测试机提供的最多1152个数字测试通道,其中每一组(32通道一组)都可以在两个时钟域间随意切换,这就大大扩展了数字测试通道资源在频率组合上的可能性。

附图说明

17.图1为现有测试载具板结构示意图。

18.图2为本发明流程示意图。

19.图3为时钟域切换电路图。

20.图4为本发明测试流程图。

21.图5为本发明实施例测试载具板结构示意图。

具体实施方式

22.下面根据附图对本发明做进一步的说明。

23.如图1至图4所示,一种应用于自动测试机soc芯片并行测试切换方法,具体流程如下:s1:在测试载具板上的数据接口及mcu端连接一组数字测试通道a,在测试载具板上的以太网接口端连接一组数字测试通道b,数字测试通道b上连接时钟域切换电路;s2:设置系统时钟周期为250mhz,则数字测试通道组a的频率为250 mhz/10=25 mhz;设置模拟时钟周期为240 mhz,则数字测试通道组b的频率为240mhz/10=24 mhz;s3:测试开始时,利用数字测试通道组a对被测soc芯片完成微处理器mcu的功能测试;利用数字测试通道组b对被测soc芯片完成以太网内核的功能测试;

s4:两项测试完成后,判断测试是否通过,是则被测soc芯片认定合格;否则被测soc芯片认定不合格。

24.时钟域切换电路可以连接到音频内核端的数字测试通道上。

25.时钟域切换电路可以连接到视频内核端的数字测试通道上。

26.时钟域切换电路可以连接到数据接口及mcu端的数字测试通道上。

27.音频内核端、视频内核端、数据接口及mcu端设置在测试载具板上。

28.时钟域切换电路通过时钟切换芯片lmk01020实现的时钟域切换。

29.本发明在自动测试机的数字测试通道上连接时钟域切换电路,根据测试需要,可以通过时钟域切换电路切换到模拟时钟域,这样就可以让两个端口在不同频率下同时启动逻辑测试。自动测试机提供的最多1152个数字测试通道,其中每一组(32通道一组)都可以在两个时钟域间随意切换,这就大大扩展了数字测试通道资源在频率组合上的可能性。利用2选1的时钟切换芯片lmk01020实现的时钟域切换电路图。

30.实施例:如图5所示,音频内核的模拟信号测试(信噪比,谐波失真比,增益,等等)需要的时钟频率,与视频内核模拟信号测试所需不同。传统测试机也是串行测试这两部分。

31.在本发明自动测试机上,可以将高速模拟信号发生器和高速模拟信号采集器通过时钟域切换电路都配置到系统时钟域,与数字测试通道共享。因为视频内核通常都有16位宽的高速数模转换器(dac,digital

‑

to

‑

analog converter)和高速模数转换器(adc,analog

‑

to

‑

digital converter)构成,其工作的并行数据总线按照100mhz以上的刷新率工作,并且数据刷新率与dac,adc的工作频率是同步的。这样,系统时钟域里的数字测试资源和高速模拟测试资源就可以完成视频内核的测试。

32.音频内核与数字接口的通讯是异步串行总线模式,可以将它对应的数字测试通道保留在系统时钟域。音频内核通常有自己内置的固定频率发生器(pll),以配合其内部的数字滤波器和数字信号处理器的工作。它的频率与测试机无法严格同步,必然会导致输入输出模拟信号的频谱泄露,给后期的软件处理和计算引入误差。这时候,将音频模拟信号发生器和音频模拟信号采集器配置到另外一个时钟域,即模拟时钟域。可以不受数字测试通道工作频率的限制,任意调整模拟时钟域的频率,优化送入芯片的模拟信号,达到最低的频谱泄露,降低后期软件运算的误差。

33.利用两个时钟域的合理分配,就能够并行测试音频内核、视频内核。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1