1.本发明涉及集成电路技术领域,尤其涉及一种集成电路的测试结构。

背景技术:

2.静电放电(electrostatic discharges,简称esd)对电子器件的危害,尤其对集成电路(integrated circuit,简称ic)的危害,越来越引起人们的重视。在静电放电的情况下,会有较大的电压施加于集成电路,集成电路中触发闩锁效应(latch-up),导致突然而猛烈的电压骤回(snapback)现象。这种电压骤回现象通常会影响集成电路的稳定性甚至损伤集成电路。

3.为保证集成电路的可靠性,需要测试集成电路发生闩锁效应时的电学参数,以进行集成电路的设计。

技术实现要素:

4.鉴于上述问题,本发明实施例提供一种集成电路的测试结构,用于测试集成电路发生闩锁效应时的电学参数。

5.为了实现上述目的,本发明实施例提供如下技术方案:

6.第一方面,本发明实施例提供一种集成电路的测试结构,其包括:第一p型重掺杂区、第二p型重掺杂区和n型重掺杂区;其中,所述第一p型重掺杂区、所述第二p型重掺杂区和所述n型重掺杂区均位于n阱内,且所述n阱位于p型衬底上;所述第一p型重掺杂区与所述第二p型重掺杂区之间具有第一距离,所述第二p型重掺杂区与所述n型重掺杂区之间具有第二距离,通过调整所述第一距离和/或所述第二距离,获得所述集成电路的电学参数。

7.如上所述的集成电路的测试结构,所述第二p型重掺杂区位于所述第一p型重掺杂区和所述n型重掺杂区之间;所述第一p型重掺杂区,所述n阱和所述第二p型重掺杂区形成寄生pnp型晶体管。

8.如上所述的集成电路的测试结构,所述n阱具有寄生电阻,所述寄生电阻的第一端连接所述n型重掺杂区,所述寄生电阻的第二端连接所述寄生pnp型晶体管的基级。

9.第二方面,本发明实施例提供一种集成电路的测试结构,其包括:第一p型重掺杂区、第二p型重掺杂区和n型重掺杂区;其中,所述第一p型重掺杂区位于p型衬底上,所述第二p型重掺杂区和所述n型重掺杂区均位于n阱内,所述n阱位于所述p型衬底上;所述第一p型重掺杂区与所述第二p型重掺杂区之间具有第一距离,所述第二p型重掺杂区与所述n型重掺杂区之间具有第二距离,通过调整所述第一距离和/或所述第二距离,获得所述集成电路的电学参数。

10.如上所述的集成电路的测试结构,所述第二p型重掺杂区位于所述第一p型重掺杂区和所述n型重掺杂区之间;所述第一p型重掺杂区,所述n阱和所述第二p型重掺杂区形成寄生pnp型晶体管。

11.如上所述的集成电路的测试结构,所述n阱具有寄生电阻,所述寄生电阻的第一端

连接所述n型重掺杂区,所述寄生电阻的第二端连接所述寄生pnp型晶体管的基级。

12.第三方面,本发明实施例提供一种集成电路的测试结构,其包括:第一p型重掺杂区、第二p型重掺杂区和n型重掺杂区;其中,所述第一p型重掺杂区、所述第二p型重掺杂区和所述n型重掺杂区均位于深n阱内,且所述深n阱位于p型衬底上;所述第一p型重掺杂区位于第一p阱内,且所述第一p阱位于所述深n阱内;和/或,所述第二p型重掺杂区位于第二p阱内,且所述第二p阱位于在所述深n阱内;所述第一p型重掺杂区与所述第二p型重掺杂区之间具有第一距离,所述第二p型重掺杂区与所述n型重掺杂区之间具有第二距离,通过调整所述第一距离和/或所述第二距离,获得所述集成电路的电学参数。

13.如上所述的集成电路的测试结构,所述第二p型重掺杂区位于深n阱内,所述第一p型重掺杂区位于所述第一p阱内;所述第二p型重掺杂区位于所述第一p型重掺杂区和所述n型重掺杂区之间;所述第一p阱,所述深n阱和所述第二p型重掺杂区形成寄生pnp型晶体管。

14.如上所述的集成电路的测试结构,所述深n阱具有寄生电阻,所述寄生电阻的第一端连接所述n型重掺杂区,所述寄生电阻的第二端连接所述寄生pnp型晶体管的基级。

15.如上所述的集成电路的测试结构,所述第一p型重掺杂区位于所述深n阱内,所述第二p型重掺杂区位于所述第二p阱内;所述第二p型重掺杂区位于所述第一p型重掺杂区和所述n型重掺杂区之间;所述第一p型重掺杂区,所述深n阱和所述第二p阱形成寄生pnp型晶体管。

16.如上所述的集成电路的测试结构,所述深n阱具有寄生电阻,所述寄生电阻的第一端连接所述n型重掺杂区,所述寄生电阻的第二端连接所述寄生pnp型晶体管的基级。

17.如上所述的集成电路的测试结构,所述第一p型重掺杂区位于所述第一p阱内,所述第二p型重掺区位于所述第二p阱内;所述第二p型重掺杂区位于所述第一p型重掺杂区和所述n型重掺杂区之间;所述第一p阱,所述深n阱和所述第二p阱形成寄生pnp晶体管。

18.如上所述的集成电路的测试结构,所述深n阱具有寄生电阻,所述寄生电阻的第一端连接所述n型重掺杂区,所述寄生电阻的第二端连接所述寄生pnp型晶体管的基级。

19.第四方面,本发明实施例提供一种集成电路的测试结构,其包括:第一p型重掺杂区、第二p型重掺杂区和n型重掺杂区;其中,所述第一p型重掺杂区位于p型衬底上,所述第二p型重掺杂区位于p阱内,且所述p阱位于深n阱内,所述n型重掺杂区位于所述深n阱内,且所述深n阱位于所述p型衬底上;所述第一p型重掺杂区与所述第二p型重掺杂区之间具有第一距离,所述第二p型重掺杂区与所述n型重掺杂区之间具有第二距离,通过调整所述第一距离和/或所述第二距离,获得所述集成电路的电学参数。

20.如上所述的集成电路的测试结构,所述第二p型重掺杂区位于所述第一p型重掺杂区和所述n型重掺杂区之间;所述第一p型重掺杂区,所述深n阱和所述p阱形成寄生pnp晶体管。

21.如上所述的集成电路的测试结构,所述深n阱具有寄生电阻,所述寄生电阻的第一端连接所述n型重掺杂区,所述寄生电阻的第二端连接所述寄生pnp晶体管的基级。

22.第五方面,本发明实施例提供一种集成电路的测试结构,其包括:第一p型重掺杂区、第二p型重掺杂区和n型重掺杂区;其中,所述第一p型重掺杂区位于p型衬底上,所述第二p型重掺杂区和所述n型重掺杂区均位于深n阱内,且所述深n阱位于所述p型衬底上;所述第一p型重掺杂区与所述第二p型重掺杂区之间具有第一距离,所述第二p型重掺杂区与所

述n型重掺杂区之间具有第二距离,通过调整所述第一距离和/或所述第二距离,获得所述集成电路的电学参数。

23.如上所述的集成电路的测试结构,所述第二p型重掺杂区位于所述第一p型重掺杂区和所述n型重掺杂区之间;所述第一p型重掺杂区,所述深n阱和所述第二p型重掺杂区形成寄生pnp晶体管。

24.如上所述的集成电路的测试结构,所述深n阱具有寄生电阻,所述寄生电阻的第一端连接所述n型重掺杂区,所述寄生电阻的第二端连接所述寄生pnp晶体管的基级。

附图说明

25.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作一简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

26.图1为本发明实施例中的集成电路的测试结构的应用场景示意图;

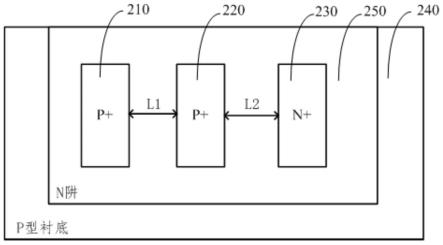

27.图2为本发明实施例中的第一种集成电路的测试结构的俯视图;

28.图3为本发明实施例中的第一种集成电路的测试结构的剖视图;

29.图4为本发明实施例中的第二种集成电路的测试结构的俯视图;

30.图5为本发明实施例中的第二种集成电路的测试结构的剖视图;

31.图6为本发明实施例中的第三种集成电路的测试结构的俯视图;

32.图7为本发明实施例中的第三种集成电路的测试结构的剖视图;

33.图8为本发明实施例中的第四种集成电路的测试结构的俯视图;

34.图9为本发明实施例中的第四种集成电路的测试结构的剖视图;

35.图10为本发明实施例中的第五种集成电路的测试结构的俯视图;

36.图11为本发明实施例中的第五种集成电路的测试结构的剖视图;

37.图12为本发明实施例中的第六种集成电路的测试结构的俯视图;

38.图13为本发明实施例中的第六种集成电路的测试结构的剖视图;

39.图14为本发明实施例中的第七种集成电路的测试结构的俯视图;

40.图15为本发明实施例中的第七种集成电路的测试结构的剖视图。

41.附图标记说明:

42.100-晶圆;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

110-裸片;

43.120-划片道;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

210-第一p型重掺杂区;

44.220-第二p型重掺杂区;

ꢀꢀꢀꢀꢀꢀꢀꢀ

230-n型重掺杂区;

45.240-p型衬底;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

250-n阱;

46.260-深n阱;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

270-第一p阱;

47.280-第二p阱;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

290-浅槽隔离结构;

48.300-p阱。

具体实施方式

49.为了提高集成电路的可靠性,在开发阶段,需要根据集成电路发生闩锁效应时的

电学参数来进行集成电路的设计。本发明实施例提供一种集成电路的测试结构,该测试结构包括第一p型重掺杂区、第二p型重掺杂区和n型重掺杂区,第一p型重掺杂区与第二p型重掺杂区之间具有第一距离,第二p型重掺杂区与n型重掺杂区之间具有第二距离。在不同的测试结构中,第一距离和第二距离不同,通过调整每种测试结构中的第一距离和/或第二距离,获得该测试结构所对应的集成电路的电学参数,从而为集成电路的设计提供依据,提高集成电路的可靠性。

50.为了使本发明实施例的上述目的、特征和优点能够更加明显易懂,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例仅仅是本发明的一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动的前提下所获得的所有其它实施例,均属于本发明保护的范围。

51.图1为本发明实施例提供的集成电路的测试结构的应用场景示意图。如图1所示,该测试结构应用场景涉及晶圆100,晶圆100切割后形成多个裸片120和划片道110。集成电路设置在裸片120内,集成电路的测试结构设置在划片道内110或者裸片120内。集成电路与集成电路的测试结构的等效电路相同,通过集成电路的测试结构来测试集成电路发生闩锁效应时的电学参数。

52.电学参数包括发生闩锁效应的触发电压(trigger voltage)、维持电压(holding voltage)、触发电流(trigger current)和维持电流(holding current)等。其中,触发电压为发生闩锁效应的电压,维持电压为维持闩锁效应的电压,触发电流为触发闩锁效应时的电流,维持电流为维持闩锁效应的电流。触发电压通常大于维持电压,随着触发电压或者维持电压的增加,闩锁效应发生的可能性降低,即越不易发生闩锁效应。

53.上述电学参数与集成电路的具体结构有一定关系,通过集成电路的测试结构测得集成电路的电学参数,并根据测试结果设计裸片110中的集成电路中,从而避免裸片110中的集成电路在工作过程中发生闩锁效应,从而提高集成电路的可靠性。具体的,可以通过传输线脉冲发生器(transmission line pulse,tlp)对该集成电路的测试结构进行测试,根据测试结果可以设计相对应的集成电路的设计规则,从而保证集成电路的可靠性。

54.下面对本发明实施例提供的集成电路的测试结构进行详细说明,图2至图15共提供七种集成电路的测试结构。在下述实施例中,重掺杂区是指掺入的杂质量多,即掺杂浓度高,p型重掺杂区简称p+,n型重掺杂区简称n+。p型衬底是指p型半导体(空穴型半导体)衬底;n阱(n well)的深度小于深n阱(deep n well),n阱的深度通常为0.3~0.5μm,深n阱的深度通常为0.5μm~1μm。

55.实施例一

56.参照图2和图3,图2为本发明实施例中的第一种集成电路的测试结构的俯视图;图3为本发明实施例中的第一种集成电路的测试结构的剖视图。

57.如图2和图3所示,集成电路的测试结构包括第一p型重掺杂区210、第二p型重掺杂区220和n型重掺杂区230。第一p型重掺杂区210、第二p型重掺杂区220和n型重掺杂区230之间可以设置有浅槽隔离结构(shallow trench isolation,简称sti),浅槽隔离结构290中填充绝缘材料,以将各掺杂区隔离,其中,浅槽隔离结构290的深度可以为0.3μm。浅槽隔离结构290的深度是指图3所示的竖直方向。

58.第一p型重掺杂区210、第二p型重掺杂区220和n型重掺杂区230均位于n阱250内,且n阱250位于p型衬底240上。如图2和图3所示,第二p型重掺杂区220位于第一p型重掺杂区210和n型重掺杂区230之间。

59.如图2所示,第一p型重掺杂区210与第二p型重掺杂区220之间具有第一距离l1,第二p型重掺杂区220与n型重掺杂区230之间具有第二距离l2。集成电路的测试结构通过调整第一距离l1和第二距离l2中的至少一个,获得集成电路的电学参数。

60.第一p型重掺杂区210,n阱250和第二p型重掺杂区220形成寄生pnp型晶体管。n阱250具有寄生电阻r1,如图3所示,寄生电阻r1的第一端连接n型重掺杂区230,寄生电阻r1的第二端连接寄生pnp型晶体管的基级。

61.在对本发明实施例中的集成电路的测试结构进行测试前,需将该测试结构进行电连接。如图3所示,第一p型重掺杂区210连接接地端vss,第二p型重掺杂区220和n型重掺杂区230连接电源端vdd。

62.测试时,将施加于电源端vdd的电压从0v开始逐渐增加,例如从0v开始逐渐增加至5v,监测电源端vdd和接地端vss之间的电流。当电源端vdd和接地端vss之间的电流突然变大时,判定此时发生闩锁效应。

63.通过调整第一距离l1和第二距离l2中的至少一个,得到多组第一距离l1、第二距离l2与闩锁效应的触发电压、维持电压、触发电流、维持电流之间的对应关系,即获得不同的第一距离l1和第二距离l2与集成电路的电学参数之间的对应关系。根据获得的对应关系对集成电路进行设计,从而避免集成电路在工作过程中发生闩锁效应,提高芯片的可靠性。

64.在上述集成电路的测试结构中,寄生pnp型晶体管的基级为n阱250,基级到集电极的增益可达数十倍,在图3所示的寄生pnp型晶体管和寄生电阻r1所形成的等效电路中,寄生pnp型晶体管存在截止状态和导通状态。当无外界干扰未引起触发时,寄生pnp型晶体管处于截止状态,集电极为c-b的反向漏电流,电流增益非常小,闩锁效应不会产生。当寄生pnp型晶体管受到外界干扰,其集电极电流或电压突然增加到预设值时,寄生pnp型晶体管导通,此时,寄生pnp型晶体管会在电源端vdd和接地端vss形成低抗通路,只需要一个非常小的电流就可以持续驱动寄生pnp型晶体管的放大状态,即形成闩锁。

65.本发明实施例提供一种集成电路的测试结构,其包括第一p型重掺杂区210、第二p型重掺杂区220和n型重掺杂区230;其中,第一p型重掺杂区210、第二p型重掺杂区220和n型重掺杂区230均位于n阱250内,且n阱250位于p型衬底240上;第一p型重掺杂区210与第二p型重掺杂区220之间具有第一距离l1,第二p型重掺杂区220与n型重掺杂区230之间具有第二距离l2,通过调整第一距离l1和/或第二距离l2,获得集成电路的电学参数。根据第一距离l1和/或第二距离l2与电学参数之间的关系,对集成电路中的进行设计,以避免集成电路发生闩锁效应,提高集成电路的可靠性。

66.实施例二

67.参照图4和图5,图4为本发明实施例中的第二种集成电路的测试结构的俯视图;图5为本发明实施例中的第二种集成电路的测试结构的剖视图。

68.如图4和图5所示,集成电路的测试结构包括第一p型重掺杂区210、第二p型重掺杂区220和n型重掺杂区230。第一p型重掺杂区210、第二p型重掺杂区220和n型重掺杂区230之间还设有浅槽隔离结构290,浅槽隔离结构290中填充绝缘材料,以将各掺杂区隔离,其中,

浅槽隔离结构290的深度可以为0.3μm。

69.第一p型重掺杂区210位于p型衬底240上,第二p型重掺杂区220和n型重掺杂区230均位于n阱250内,n阱250位于p型衬底240上。如图4和图5所示,第二p型重掺杂区220位于第一p型重掺杂区210和n型重掺杂区230之间。

70.如图4所示,第一p型重掺杂区210与第二p型重掺杂区220之间具有第一距离l1,第二p型重掺杂区220与n型重掺杂区230之间具有第二距离l2。集成电路的测试结构通过调整第一距离l1和/或第二距离l2,获得集成电路的电学参数。

71.第一p型重掺杂区210,n阱250和第二p型重掺杂区220形成寄生pnp型晶体管。n阱250具有寄生电阻r1,如图4所示,寄生电阻r1的第一端连接n型重掺杂区230,寄生电阻r1的第二端连接寄生pnp型晶体管的基级。

72.在对本发明实施例中的集成电路的测试结构进行测试前,需将该测试结构进行电连接。如图5所示,第一p型重掺杂区210连接接地端vss,第二p型重掺杂区220和n型重掺杂区230连接电源端vdd。

73.测试时,将施加于电源端vdd的电压从0v开始逐渐增加,例如从0v开始逐渐增加至5v,监测电源端vdd和接地端vss之间的电流。当电源端vdd和接地端vss之间的电流突然变大时,判定此时发生闩锁效应。

74.通过调整第一距离l1和第二距离l2中的至少一个,得到多组第一距离l1、第二距离l2与闩锁效应的触发电压、维持电压、触发电流、维持电流之间的对应关系,即获得不同的第一距离l1和第二距离l2与集成电路的电学参数之间的对应关系。根据获得的对应关系对集成电路进行设计,从而避免集成电路在工作过程中发生闩锁效应,提高芯片的可靠性。

75.在上述集成电路的测试结构中,寄生pnp型晶体管的基级为n阱250,基级到集电极的增益可达数十倍,在图5所示的寄生pnp型晶体管和寄生电阻r1形成的等效电路中,寄生pnp型晶体管存在截止状态和导通状态。当无外界干扰未引起触发时,寄生pnp型晶体管处于截止状态,集电极为c-b的反向漏电流,电流增益非常小,闩锁效应不会产生。当寄生pnp型晶体管受到外界干扰,其集电极电流或电压突然增加到预设值时,寄生pnp型晶体管导通,此时,寄生pnp型晶体管会在电源端vdd和接地端vss形成低抗通路,只需要一个非常小的电流就可以持续驱动寄生pnp型晶体管的放大状态,即形成闩锁。

76.本发明实施例提供一种集成电路的测试结构,其包括第一p型重掺杂区210、第二p型重掺杂区220和n型重掺杂区230;其中,第一p型重掺杂区210位于p型衬底240上,第二p型重掺杂区220和n型重掺杂区230均位于n阱250内,n阱250位于p型衬底240上;第一p型重掺杂区210与第二p型重掺杂区220之间具有第一距离,第二p型重掺杂区220与n型重掺杂区230之间具有第二距离,通过调整第一距离和/或第二距离,获得集成电路的电学参数。根据第一距离和/或第二距离与电学参数之间的关系,设置集成电路中的距离,以避免集成电路发生闩锁效应,提高集成电路的可靠性。

77.实施例三

78.参照图6至图11,图6为本发明实施例中的第三种集成电路的测试结构的俯视图;图7为本发明实施例中的第三种集成电路的测试结构的剖视图;图8为本发明实施例中的第四种集成电路的测试结构的俯视图;图9为本发明实施例中的第四种集成电路的测试结构的剖视图;图10为本发明实施例中的第五种集成电路的测试结构的俯视图;图11为本发明

实施例中的第五种集成电路的测试结构的剖视图。

79.集成电路的测试结构包括第一p型重掺杂区210、第二p型重掺杂区220和n型重掺杂区230。第一p型重掺杂区210、第二p型重掺杂区220和n型重掺杂区230之间还设有浅槽隔离结构290,浅槽隔离结构290中填充绝缘材料,以将各掺杂区隔离,其中,浅槽隔离结构290的深度可以为0.3μm。

80.第一p型重掺杂区210、第二p型重掺杂区220和n型重掺杂区230均位于深n阱260内,且深n阱260位于p型衬底240上,第一p型重掺杂区210位于第一p阱270内,且第一p阱270位于深n阱260内;和/或,第二p型重掺杂区220位于第二p阱280内,且第二p阱280位于在深n阱260内。

81.如图6至图11所示,第二p型重掺杂区220可以位于第一p型重掺杂区210和n型重掺杂区230之间,第一p型重掺杂区210与第二p型重掺杂区220之间具有第一距离l1,第二p型重掺杂区220与n型重掺杂区230之间具有第二距离l2。集成电路的测试结构通过调整第一距离l1和/或第二距离l2,获得集成电路的电学参数。

82.在第一种可能的示例中,如图6和图7所示,第二p型重掺杂区220位于深n阱260内,第一p型重掺杂区210位于第一p阱270内。即n型重掺杂区230和第二p型重掺杂区220均位于深n阱260内,且深n阱260位于p型衬底240上,第一p型重掺杂区210位于第一p阱270内,且第一p阱270位于在深n阱260内。

83.如图7所示,第一p阱270,深n阱260和第二p型重掺杂区220形成寄生pnp型晶体管,深n阱260具有寄生电阻r1,寄生电阻r1的第一端连接n型重掺杂区230,寄生电阻r1的第二端连接寄生pnp型晶体管的基级。

84.在第二种可能的示例中,如图8和图9所示,第一p型重掺杂区210位于深n阱260内,第二p型重掺杂区220位于第二p阱280内。即n型重掺杂区230和第一p型重掺杂区210均位于深n阱260内,且深n阱260位于p型衬底240上,第二p型重掺杂区220位于第二p阱280内,且第二p阱280位于在深n阱260内。

85.如图9所示,第一p型重掺杂区210,深n阱260和第二p阱280形成寄生pnp型晶体管。深n阱260具有寄生电阻r1,寄生电阻r1的第一端连接n型重掺杂区230,寄生电阻r1的第二端连接寄生pnp型晶体管的基级

86.在第三种可能的示例中,如图10和图11所示,第一p型重掺杂区210位于第一p阱270内,第二p型重掺区位于第二p阱280内。即n型重掺杂区230位于深n阱260内,且深n阱260位于p型衬底240上,第一p型重掺杂区210位于第一p阱270内,第二p型重掺杂区位于第二p阱280内,第一p阱270和第二p阱280位于深n阱260内。

87.如图11所示,第一p阱270,深n阱260和第二p阱280形成寄生pnp晶体管。深n阱260具有寄生电阻r1,寄生电阻r1的第一端连接n型重掺杂区230,寄生电阻r1的第二端连接寄生pnp型晶体管的基级。

88.在对上述三种示例中的集成电路的测试结构进行测试前,需将该测试结构进行电连接。具体的,如图7、图9和图11所示,第一p型重掺杂区210连接接地端vss,第二p型重掺杂区220和n型重掺杂区230连接电源端vdd。

89.测试时,将施加于电源端vdd的电压从0v开始逐渐增加,例如从0v开始逐渐增加至5v,监测电源端vdd和接地端vss之间的电流。当电源端vdd和接地端vss之间的电流突然变

大时,判定此时发生闩锁效应。

90.通过调整第一距离l1和第二距离l2中的至少一个,得到多组第一距离l1、第二距离l2与闩锁效应的触发电压、维持电压、触发电流、维持电流之间的对应关系,即获得不同的第一距离l1和第二距离l2与集成电路的电学参数之间的对应关系。根据获得的对应关系对集成电路进行设计,从而避免集成电路在工作过程中发生闩锁效应,提高芯片的可靠性。

91.在上述集成电路的测试结构中,寄生pnp型晶体管的基级为深n阱260,基级到集电极的增益可达数十倍,图7、图9和图11所示的寄生pnp型晶体管和寄生电阻r1形成的等效电路中,寄生pnp型晶体管存在截止状态和导通状态。当无外界干扰未引起触发时,寄生pnp型晶体管处于截止状态,集电极为c-b的反向漏电流,电流增益非常小,闩锁效应不会产生。当寄生pnp型晶体管受到外界干扰,其集电极电流或电压突然增加到预设值时,寄生pnp型晶体管导通,此时,寄生pnp型晶体管会在电源端vdd和接地端vss形成低抗通路,只需要一个非常小的电流就可以持续驱动寄生pnp型晶体管的放大状态,即形成闩锁。

92.本发明实施例提供一种集成电路的测试结构,其包括第一p型重掺杂区210、第二p型重掺杂区220和n型重掺杂区230均位于深n阱260内,且深n阱260位于p型衬底240上,第一p型重掺杂区210位于第一p阱270内,且第一p阱270位于深n阱260内;和/或,第二p型重掺杂区220位于第二p阱280内,且第二p阱280位于在深n阱260内。第一p型重掺杂区210与第二p型重掺杂区220之间具有第一距离l1,第二p型重掺杂区220与n型重掺杂区230之间具有第二距离l2,通过调整第一距离l1和/或第二距离l2,获得集成电路的电学参数。根据第一距离l1和/或第二距离l2与电学参数之间的关系,设置集成电路中的距离,以避免集成电路发生闩锁效应,提高集成电路的可靠性。

93.实施例四

94.参照图12和图13,图12为本发明实施例中的第六种集成电路的测试结构的俯视图;图13为本发明实施例中的第六种集成电路的测试结构的剖视图。

95.如图12和图13所示,集成电路的测试结构包括第一p型重掺杂区210、第二p型重掺杂区220和n型重掺杂区230。第一p型重掺杂区210、第二p型重掺杂区220和n型重掺杂区230之间还设有浅槽隔离结构290,浅槽隔离结构290中填充绝缘材料,以将各掺杂区隔离,其中,浅槽隔离结构290的深度可以为0.3μm。

96.第一p型重掺杂区210位于p型衬底240上,第二p型重掺杂区220位于p阱300内,且p阱300位于深n阱260内,n型重掺杂区230位于深n阱260内,且深n阱260位于p型衬底240上。如图12和图13所示,第二p型重掺杂区220位于第一p型重掺杂区210和n型重掺杂区230之间。

97.如图12所示,第一p型重掺杂区210与第二p型重掺杂区220之间具有第一距离l1,第二p型重掺杂区220与n型重掺杂区230之间具有第二距离l2。集成电路的测试结构通过调整第一距离l1和/或第二距离l2,获得集成电路的电学参数。

98.第一p型重掺杂区210,深n阱260和p阱300形成寄生pnp型晶体管。深n阱260具有寄生电阻r1,寄生电阻r1的第一端连接n型重掺杂区230,寄生电阻r1的第二端连接寄生pnp型晶体管的基级。

99.在对本发明实施例中的集成电路的测试结构进行测试前,需将该测试结构进行电连接。如图13所示,第一p型重掺杂区210连接接地端vss,第二p型重掺杂区220和n型重掺杂

区230连接电源端vdd。

100.测试时,将施加于电源端vdd的电压从0v开始逐渐增加,例如从0v开始逐渐增加至5v,监测电源端vdd和接地端vss之间的电流。当电源端vdd和接地端vss之间的电流突然变大时,判定此时发生闩锁效应。

101.通过调整第一距离l1和第二距离l2中的至少一个,得到多组第一距离l1、第二距离l2与闩锁效应的触发电压、维持电压、触发电流、维持电流之间的对应关系,即获得不同的第一距离l1和第二距离l2与集成电路的电学参数之间的对应关系。根据获得的对应关系对集成电路进行设计,从而避免集成电路在工作过程中发生闩锁效应,提高芯片的可靠性。

102.在上述集成电路的测试结构中,寄生pnp型晶体管的基级为深n阱260,基级到集电极的增益可达数十倍,图13所示的寄生pnp型晶体管和寄生电阻r1形成的等效电路中,寄生pnp型晶体管存在截止状态和导通状态。当无外界干扰未引起触发时,寄生pnp型晶体管处于截止状态,集电极为c-b的反向漏电流,电流增益非常小,闩锁效应不会产生。当寄生pnp型晶体管受到外界干扰,其集电极电流或电压突然增加到预设值时,寄生pnp型晶体管导通,此时,寄生pnp型晶体管会在电源端vdd和接地端vss形成低抗通路,只需要一个非常小的电流就可以持续驱动寄生pnp型晶体管的放大状态,即形成闩锁。

103.本发明实施例提供一种集成电路的测试结构,其包括第一p型重掺杂区210、第二p型重掺杂区220和n型重掺杂区230;其中,第一p型重掺杂区210位于p型衬底240上,第二p型重掺杂区220位于p阱300内,且p阱300位于深n阱260内,n型重掺杂区230位于深n阱260内,且深n阱260位于p型衬底240上;第一p型重掺杂区210与第二p型重掺杂区220之间具有第一距离l1,第二p型重掺杂区220与n型重掺杂区230之间具有第二距离l2,通过调整第一距离l1和/或第二距离l2,获得集成电路的电学参数。根据第一距离l1和/或第二距离l2与电学参数之间的关系,设置集成电路中的距离,以避免集成电路发生闩锁效应,提高集成电路的可靠性。

104.实施例五

105.参照图14和图15,图14为本发明实施例中的第七种集成电路的测试结构的俯视图;图15为本发明实施例中的第七种集成电路的测试结构的剖视图。

106.如图14和图15所示,该测试结构包括第一p型重掺杂区210、第二p型重掺杂区220和n型重掺杂区230。第一p型重掺杂区210、第二p型重掺杂区220和n型重掺杂区230之间还可以设置有浅槽隔离结构290,浅槽隔离结构290中填充绝缘材料,以将各掺杂区隔离,其中,浅槽隔离结构290的深度可以为0.3μm。

107.第一p型重掺杂区210位于p型衬底240上,n型重掺杂区230和第二p型重掺杂区220均位于深n阱260内,且深n阱260位于p型衬底240上。示例性的,第二p型重掺杂区220位于第一p型重掺杂区210和n型重掺杂区230之间。

108.如图14所示,第一p型重掺杂区210与第二p型重掺杂区220之间具有第一距离l1,第二p型重掺杂区220与n型重掺杂区230之间具有第二距离l2。集成电路的测试结构通过调整第一距离l1和/或第二距离l2,获得集成电路的电学参数。

109.第一p型重掺杂区210,深n阱260和第二p型重掺杂区220形成寄生pnp晶体管。n阱250具有寄生电阻r1,如图15所示,寄生电阻r1的第一端连接n型重掺杂区230,寄生电阻r1的第二端连接寄生pnp型晶体管的基级。

110.在对本发明实施例中的集成电路的测试结构进行测试前,需将该测试结构进行电连接。如图15所示,第一p型重掺杂区210连接接地端vss,第二p型重掺杂区220和n型重掺杂区230连接电源端vdd。

111.测试时,将施加于电源端vdd的电压从0v开始逐渐增加,例如从0v开始逐渐增加至5v,监测电源端vdd和接地端vss之间的电流。当电源端vdd和接地端vss之间的电流突然变大时,判定此时发生闩锁效应。

112.通过调整第一距离l1和第二距离l2中的至少一个,得到多组第一距离l1、第二距离l2与闩锁效应的触发电压、维持电压、触发电流、维持电流之间的对应关系,即获得不同的第一距离l1和第二距离l2与集成电路的电学参数之间的对应关系。根据获得的对应关系对集成电路进行设计,从而避免集成电路在工作过程中发生闩锁效应,提高芯片的可靠性。

113.在上述集成电路的测试结构中,寄生pnp型晶体管的基级为深n阱260,基级到集电极的增益可达数十倍,图15所示的寄生pnp型晶体管和寄生电阻r1形成的等效电路中,寄生pnp型晶体管存在截止状态和导通状态。当无外界干扰未引起触发时,寄生pnp型晶体管处于截止状态,集电极为c-b的反向漏电流,电流增益非常小,闩锁效应不会产生。当寄生pnp型晶体管受到外界干扰,其集电极电流或电压突然增加到预设值时,寄生pnp型晶体管导通,此时,寄生pnp型晶体管会在电源端vdd和接地端vss形成低抗通路,只需要一个非常小的电流就可以持续驱动寄生pnp型晶体管的放大状态,即形成闩锁。

114.本发明实施例提供一种集成电路的测试结构,其包括第一p型重掺杂区210、第二p型重掺杂区220和n型重掺杂区230;其中,第一p型重掺杂区210位于p型衬底240上,n型重掺杂区230和第二p型重掺杂区220均位于深n阱260内,且深n阱260位于p型衬底240上;第一p型重掺杂区210与第二p型重掺杂区220之间具有第一距离l1,第二p型重掺杂区220与n型重掺杂区230之间具有第二距离l2,通过调整第一距离l1和/或第二距离l2,获得集成电路的电学参数,根据第一距离l1和/或第二距离l2与电学参数之间的关系,设置集成电路中的距离,以避免集成电路发生闩锁效应,提高集成电路的可靠性。

115.本发明实施例提供一种集成电路的测试结构,其包括,根据第一距离和/或第二距离与电学参数之间的关系,设置集成电路中的距离,以避免集成电路发生闩锁效应,提高集成电路的可靠性。

116.本说明书中各实施例或实施方式采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似部分相互参见即可。

117.在本说明书的描述中,参考术“一个实施方式”、“一些实施方式”、“示意性实施方式”、“示例”、“具体示例”、或“一些示例”等的描述意指结合实施方式或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施方式或示例中。在本说明书中,对上述术语的示意性表述不一定指的是相同的实施方式或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施方式或示例中以合适的方式结合。

118.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

- 该技术已申请专利。仅供学习研究,如用于商业用途,请联系技术所有人。

- 技术研发人员:许杞安

- 技术所有人:长鑫存储技术有限公司

- 我是此专利的发明人

- 该领域下的技术专家

- 如您需求助技术专家,请点此查看客服电话进行咨询。

- 1、邢老师:1.机械设计及理论 2.生物医学材料及器械 3.声发射检测技术。

- 2、王老师:1.数字信号处理 2.传感器技术及应用 3.机电一体化产品开发 4.机械工程测试技术 5.逆向工程技术研究

- 3、王老师:1.机器人 2.嵌入式控制系统开发

- 4、张老师:1.机械设计的应力分析、强度校核的计算机仿真 2.生物反应器研制 3.生物力学

- 5、赵老师:检测与控制技术、机器人技术、机电一体化技术

- 如您是高校老师,可以点此联系我们加入专家库。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1

精彩留言,会给你点赞!

专利分类正在加载中....