一种基于FPGA的电路板有源通路测试方法与流程

一种基于fpga的电路板有源通路测试方法

技术领域

1.本发明属于数字芯片测试领域。通过一种测试方法,实现对fpga开发电路板上的有源通路的连通性测试并找出故障点。

背景技术:

2.fpga即现场可编程门阵列,它是在pal、gal、cpld等可编程器件的基础上进一步发展的产物。fpga是作为专用集成电路(asic)领域中的一种半定制电路而出现的,既解决了定制电路的不足,有克服了原有可编程器件门电路数有限的缺点。采用fpga设计电路,用户不需要投片生产,就能得到合用的芯片,fpga是asic电路中设计周期最短、开发费用最低、风险最小的器件之一。有源数字多路选择器是能够从多个数字信号中选择某个信号并将其连接到一个输出线路中,使用该器件能够实现将一个fpga芯片的某组接口信号连接到多个不同芯片的接口上,fpga通过数字多路选择器的控制信号动态选择需要连接的芯片,在fpga开发阶段能够节约fpga的接口资源。

3.在开发测试阶段,fpga功能引脚通过有源数字多路选择器选通某一功能芯片的接口信号线,该连接在电路板上的功能是否正确,即在板级测试中,该组信号线由fpga端引脚通过有源通路连接到该功能信号对应的应用之间的通路是否无故障,一般需要做相应的接口连通性测试,而常用的使用万用表对电路板连通性进行测试只能在断电的情况下测试,而有源数字多路选择器需要上电才能工作,因此该方法不适用有源数字多路选择器的连通行性测试。为此,通常通过fpga灌入接口逻辑功能,通过fpga的该功能接口发送测试数据,观察选通的芯片是否有正确的响应来判断。由于接口数据是由多根信号组合的,一旦该通路测试结果异常,一般情况下无法直接判断是哪根信号线的通路出现了问题。另外如果想确定故障位置,需要根据测试数据配合使用逻辑分析仪或信号分析设备来分析故障位置,对于一组多根信号的通路,逻辑分析仪或信号分析设备的采样线缆对多根信号同时采样(采样点通常是焊锡焊点或者裸线位置)的连接操作的稳定性也很难保证,可能需要多频次操作。

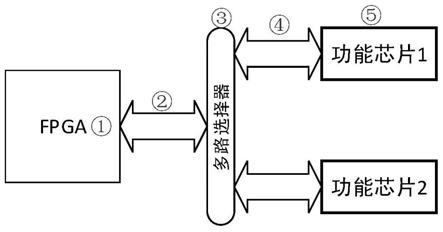

4.信号线通路的故障点如图1所示,包括:

①

fpga内部逻辑至管脚故障;

②

fpga管脚至多路选择器管脚间的布线故障;

③

多路选择器故障;

④

多路选择器管脚至功能芯片管脚间布线故障;

⑤

功能芯片故障。

技术实现要素:

5.本发明解决的技术问题是:克服现有技术的不足,提供一种基于fpga的电路板有源通路测试方法,减少fpga测试逻辑的设计复杂度,增加采样点采样的人工操作的稳定性,测试结果判据直观,能够大大缩短找出故障点位置的测试时间,提高fpga开发板测试效率。

6.本发明的技术方案是:一种基于fpga的电路板有源通路测试方法,用于在电路板有源通路出现故障时检测故障点的位置;当电路板有源通路发生故障时,电路板有源通路的故障点包括:

①

fpga内部逻辑至管脚故障;

②

fpga管脚至多路选择器管脚间的布线故障;

③

多路选择器故障;

④

多路选择器管脚至功能芯片管脚间布线故障;

⑤

功能芯片故障;步骤如下:

7.1)在fpga内部产生n路时钟发生器,得到时钟1、时钟2、

……

、时钟n,共n路不同频率的时钟,对应的时钟频率分别是频率1、频率2、

……

、频率n,上述n路不同频率的时钟作为n路有源通路的测试激励源;

8.2)将通过时钟发生器得到的n路不同频率时钟通过fpga的管脚绑定工具连接至fpga的各个接口上,分别对应电路板通路信号sig1、sig2、

……

、sign;

9.3)给电路板加电,将示波器探头放至fpga输出的时钟管脚a处采集频率;

10.4)若a处频率不等于频率1,则sig1存在故障点

①

fpga内部逻辑至管脚故障,排除故障后再返回步骤3);若a处频率等于频率1,将示波器探头放至多路选择器输入管脚b处采集频率;

11.5)若b处频率不等于频率1,则sig1存在故障点

②

fpga管脚至多路选择器管脚间的布线故障,排除故障后再返回步骤3);

12.6)若b处频率等于频率1,多路选择器选择端口0输出时,执行步骤7)。多路选择器选择端口1输出时,执行步骤9);

13.7)将示波器探头放至多路选择器输出管脚c1处采集频率,若c1处频率不等于频率1,则sig1存在故障点

③

多路选择器故障,排除故障后再返回步骤3);

14.8)若c1处频率等于频率1,将示波器探头放至功能芯片输入管脚d1处采集频率,若d1处频率不等于频率1,则sig1存在故障点

④

多路选择器管脚至功能芯片管脚间布线故障,排除故障后再返回步骤3);若d1处频率等于频率1,则存在故障点

⑤

功能芯片故障,排除故障后再返回步骤3);

15.9)将示波器探头放至多路选择器输出管脚c2处采集频率,若c2处频率不等于频率1,则sig1存在故障点

③

多路选择器故障,排除故障后再返回步骤3);

16.10)若c2处频率等于频率1,将示波器探头放至功能芯片输入管脚d2处采集频率,若d2处频率不等于频率1,则sig1存在故障点

④

多路选择器管脚至功能芯片管脚间布线故障,排除故障后再返回步骤3);若d2处频率等于频率1,则存在故障点

⑤

功能芯片故障,排除故障后再返回步骤3);

17.11)重复步骤3)~10),完成所有信号通路测试。

18.本发明与现有技术相比的优点在于:

19.1、本发明的测试激励容易实现。现有技术使用逻辑分析仪分析电路信号,需要的测试激励需要符合相关的协议,测试激励实现较复杂。本发明的测试激励采用时钟信号作为激励,通过对电路板上fpga使用的晶振时钟进行分频即可得到不同频率时钟,简单易行;

20.2、本发明对于测试人员人工操作稳定性强。现有技术使用逻辑分析仪分析电路信号,单次需要同时采样十几甚至几十根信号,人工操作稳定性较差(采样点通常是焊锡焊点或者裸线位置)。本发明单次只需要操作一根信号,人工操作稳定性高;

21.3、本发明的测试结果观测直观。现有技术使用逻辑分析仪分析电路信号,测试结果通过对多根信号的波形组合或者采样的数据协议包进行二次分析才能得到测试结果。本发明只需通过示波器观察采样点的时钟与对应的测试激励时钟是否一致即可;

22.4、本发明具有较强的适应性和通用性,现有技术对于不同的协议接口连通性测试

需要针对具体的协议开发对应的测试激励。而本发明的测试激励采用时钟信号作为激励,对于不同的协议接口均适用。

附图说明

23.图1为fpga至功能芯片选择通路故障点。

24.图2为改进前的有源通路测试方法框图。

25.图3为改进后的有源通路测试方法框图。

26.图4为时钟发生器架构图。

具体实施方式

27.图2为改进前的测试方法。

28.改进前的方法:

29.1)在fpga内部实现功能芯片的测试功能逻辑;

30.2)将功能逻辑通过fpga的管脚绑定工具连接至fpga的接口a上;

31.3)给电路板加电,在采样点a处将所有信号sig1、sig2、

……

、sign连接至逻辑分析仪上,通过fpga功能逻辑发出测试数据,逻辑分析仪分析a处协议是否异常。若a处异常,则存在故障点

①

fpga内部逻辑至管脚故障,排除故障后再重复步骤3)~7);

32.4)若a处正常,在采样点b处将所有信号sig1、sig2、

……

、sign连接至逻辑分析仪上,通过fpga功能逻辑发出测试数据,逻辑分析仪分析b处协议是否异常,若b处异常,则存在故障点

②

fpga管脚至多路选择器管脚间的布线故障,排除故障后再重复步骤3)~7);

33.5)若b处正常,在采样点c处将所有信号sig1、sig2、

……

、sign连接至逻辑分析仪上,通过fpga功能逻辑发出测试数据,逻辑分析仪分析c处协议是否异常。若c处异常,则存在故障点

③

多路选择器故障,排除故障后再重复步骤3)~7);

34.6)若c处正常,在采样点d处将所有信号sig1、sig2、

……

、sign连接至逻辑分析仪上,通过fpga功能逻辑发出测试数据,逻辑分析仪分析d处协议是否异常。若d处异常,则存在故障点

④

多路选择器管脚至功能芯片管脚间布线故障;若d处a正常,则存在故障点

⑤

功能芯片故障,排除故障后再重复步骤3)~7);

35.7)对通过以上步骤找出的故障点再使用多组不同测试数据,组合分析出是该故障点位置的哪个信号出现故障。

36.图3为改进后的测试方法,时钟发生器的实现框图见图4。

37.改进后的方法:

38.1)在fpga内部产生n路时钟发生器,得到时钟1、时钟2、

……

、时钟n共n路不同频率的时钟,对应的时钟频率分别是频率1、频率2、

……

、频率n,这n路不同频率的时钟作为n路有源通路的测试激励源;

39.2)将通过时钟发生器得到的n路不同频率时钟通过fpga的管脚绑定工具连接至fpga的各个接口上,分别对应电路板通路信号sig1、sig2、

……

、sign;

40.3)给电路板加电,将示波器探头放至fpga输出的时钟管脚a处采集频率;

41.4)若a处频率不等于频率1,则sig1存在故障点

①

fpga内部逻辑至管脚故障,排除故障后再重复步骤3)~11);若a处频率等于频率1,将示波器探头放至多路选择器输入管脚

b处采集频率;

42.5)若b处频率不等于频率1,则sig1存在故障点

②

fpga管脚至多路选择器管脚间的布线故障,排除故障后再重复步骤3)~11);

43.6)若b处频率等于频率1,多路选择器选择端口0输出时,执行步骤7)~8)。多路选择器选择端口1输出时,执行步骤9)~10);

44.7)将示波器探头放至多路选择器输出管脚c1处采集频率,若c1处频率不等于频率1,则sig1存在故障点

③

多路选择器故障,排除故障后再重复步骤3)~11);

45.8)若c1处频率等于频率1,将示波器探头放至功能芯片输入管脚d1处采集频率,若d1处频率不等于频率1,则sig1存在故障点

④

多路选择器管脚至功能芯片管脚间布线故障,排除故障后再重复步骤3)~11);若d1处频率等于频率1,则存在故障点

⑤

功能芯片故障,排除故障后再重复步骤3)~11);

46.9)将示波器探头放至多路选择器输出管脚c2处采集频率,若c2处频率不等于频率1,则sig1存在故障点

③

多路选择器故障,排除故障后再重复步骤3)~11);

47.10)若c2处频率等于频率1,将示波器探头放至功能芯片输入管脚d2处采集频率,若d2处频率不等于频率1,则sig1存在故障点

④

多路选择器管脚至功能芯片管脚间布线故障,排除故障后再重复步骤3)~11);若d2处频率等于频率1,则存在故障点

⑤

功能芯片故障,排除故障后再重复步骤3)~11);

48.11)重复步骤3)~10),完成所有信号通路测试。

49.时钟发生器说明:根据待测试信号数量n设计实现n个时钟分频,每个时钟分频器产生不同频率的时钟,例如频率1为1mhz、频率2为2mhz

……

频率n为nmhz,实际实现时频率不受限于此。

50.本发明虽然已以较佳实施例公开如上,但其并不是用来限定本发明,任何本领域技术人员在不脱离本发明的精神和范围内,都可以利用上述揭示的技术内容对本发明技术方案做出可能的变动和修改,因此,凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化及修饰,均属于本发明技术方案的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1