一种AIN压电薄膜水听器芯片单元、芯片以及水听器的制作方法

一种ain压电薄膜水听器芯片单元、芯片以及水听器

技术领域

1.本发明涉及一种ain压电薄膜水听器芯片单元、芯片以及水听器。

背景技术:

2.对于海洋信号的探测以及实现水下远距离的传播,声波是现阶段已知的唯一的能量形式。利用新材料、新原理、mems微纳制备工艺,实现低频化、低功耗、高集成度的新的水声探测器件的研发,实现对海洋中各种信号的高灵敏度的侦听,对于海洋的探测以及军事的运用有重要的意义。mems压电薄膜水听器探测的原理是首先利用aln压电薄膜的压电效应,将接收到声压信号转化为电信号,然后通过水听器的前置运算放大电路采集输出。

3.现有的压电薄膜式水听器芯片采用三明治结构,即由上、下电极以及位于上、下电极之间的压电薄膜组成,其工作原理如下:当压电薄膜受到沿一定方向的作用力而产生形变时,其内部会产生极化现象,同时会在它的两个相对表面出现正负相反的电荷,上、下电极与压电薄膜贴合,分别用以收集压电薄膜产生的正、负电荷,并输出到前置运算放大电路。

4.现阶段的压电薄膜芯片输出电荷较小,仅仅为pc级别,且针对aln材料,其压电晶相为001,当采用aln作为压电薄膜时,在受到垂直于三明治结构的方向作用力时,其正电荷主要聚集在薄膜的中心70%面积范围内,周围边缘聚集极性相反的负电荷,其中性面是一个贯穿薄膜上下的环形切面。由此可知,基于aln压电薄膜的水听器芯片,在采用三明治结构时,上电极需要进行光刻刻蚀,需要将其位置集中在压电薄膜的中间面积的70%之内,但是下电极刻蚀一般较为困难,若将下电极集中在压电薄膜的边缘位置,则需要首先进行下电极的刻蚀,之后再进行aln的压电薄膜的制备,这无疑大大提升了工艺制备的难度。

5.目前,现阶段采用的是刻蚀上电极,下电极不进行刻蚀的方法,直接通过湿法刻蚀将aln压电层直接刻蚀穿,显露出下电极,从而与外部运算放大电路连接。此种方法存在的不足之处是,所谓的下电极其实是电荷中和之后的电极,即电位为0,因此会导致上下电极之间的电位差较低,用于运算放大电路的输出不够,从而导致水听器芯片的灵敏度不高,且造成下电极材料的浪费。由此可见,现有技术中的ain压电薄膜水听器芯片需要进行改进。

技术实现要素:

6.本发明的目的之一在于提出一种ain压电薄膜水听器芯片单元,以实现对ain压电层产生的正负电荷的有效采集。本发明为了实现上述目的,采用如下技术方案:

7.一种ain压电薄膜水听器芯片单元,包括由下向上依次设置的soi基片、ain压电层以及电极层;其中,电极层与ain压电层的外缘轮廓的形状和大小均相同;

8.电极层包括正电极和负电极;其中,正电极设置于电极层的中心区域,且呈圆形;负电极设置于电极层的外侧边缘区域,且呈环形。

9.优选地,正电极所占面积为电极层面积的70%,负电极所占面积为电极层面积的20%。

10.优选地,正电极和负电极均为mo电极。

11.优选地,电极层位于正电极与负电极之间的环形区域设有二氧化硅。

12.优选地,负电极上设有供正电极引线的缺口。

13.优选地,soi基片底部设有空腔。

14.优选地,soi基片包括由下向上依次设置的下层硅、二氧化硅以及上层硅;

15.其中,空腔由下向上穿过下层硅。

16.本发明的目的之二在于提出一种ain压电薄膜水听器芯片,其采用上面述及的ain压电薄膜水听器芯片单元,以提高ain压电薄膜水听器芯片的灵敏度。

17.本发明为了实现上述目的,采用如下技术方案:

18.一种ain压电薄膜水听器芯片,包括水听器芯片单元、正电极输出端以及负电极输出端;水听器芯片单元有多个且采用阵列式排布;

19.水听器芯片单元采用上面述及的ain压电薄膜水听器芯片单元;

20.各个水听器芯片单元的正电极相连,且连接到正电极输出端上;

21.各个水听器芯片单元的负电极相连,且连接到负电极输出端上。

22.本发明的目的之三在于提出一种水听器,该水听器包括水听器芯片以及运算放大电路;水听器芯片的正电极输出端和负电极输出端分别连接到运算放大电路上;

23.其中,水听器芯片采用上面述及的ain压电薄膜水听器芯片。

24.由于本发明中的水听器采用上述ain压电薄膜水听器芯片,灵敏度会明显提高。

25.本发明具有如下优点:

26.如上所述,本发明提供了一种ain压电薄膜水听器芯片单元,该ain压电薄膜水听器芯片单元通过改进正负电极的排布方式,利于提高水听器芯片单元的正负电荷采集效率,进而增加了正负电极之间的电势差(对比度),从而提高了ain压电薄膜水听器芯片的灵敏度。

附图说明

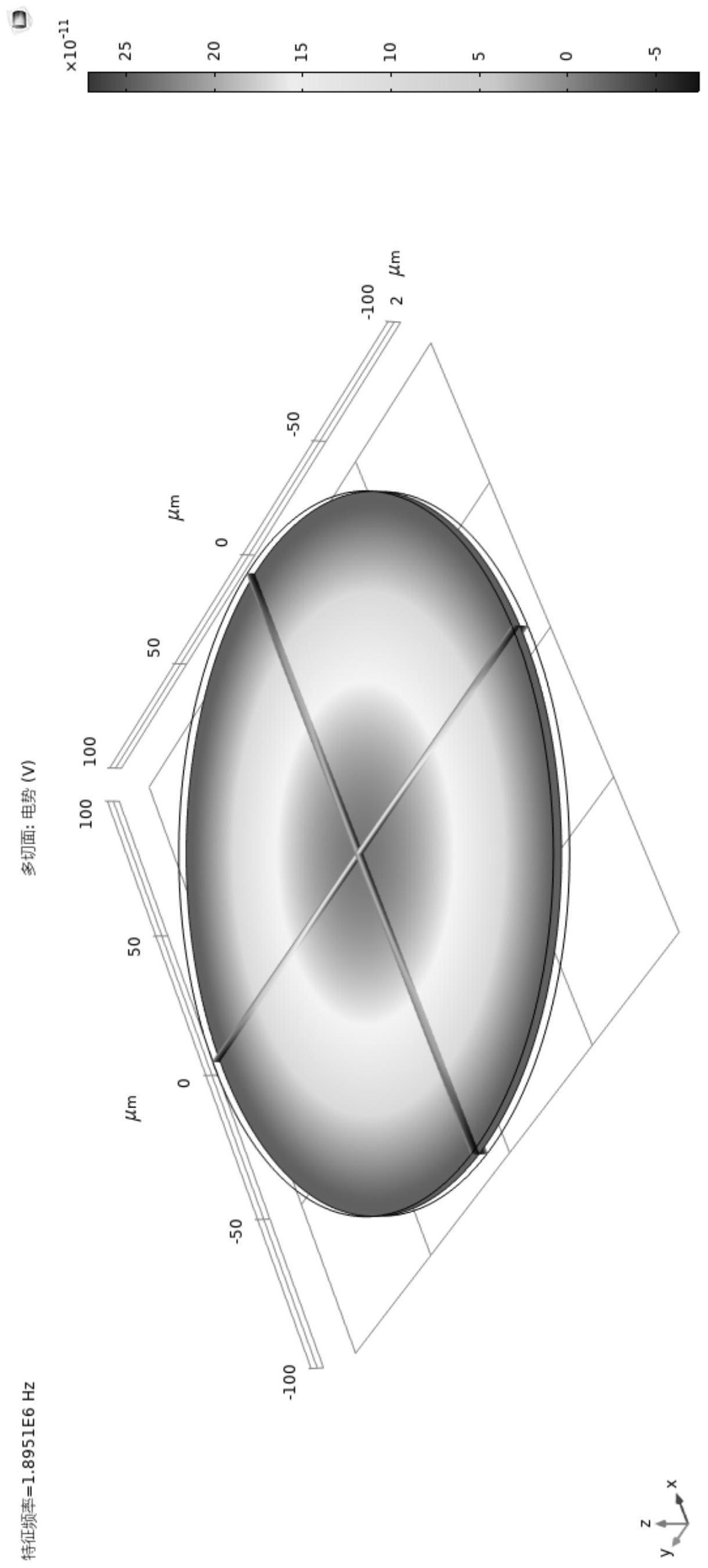

27.图1为aln压电薄膜电荷分布情况示意图。

28.图2为本实施例1中ain压电薄膜水听器芯片单元的结构示意图;

29.图3为本实施例1中ain压电薄膜水听器芯片单元的俯视图;

30.图4为本实施例1中ain压电薄膜水听器芯片单元的仰视图;

31.图5为本实施例1中ain压电薄膜水听器芯片单元的剖视图;

32.图6为本实施例1中ain压电薄膜水听器芯片单元的结构示意图;

33.图7为本实施例2中ain压电薄膜水听器芯片的结构示意图;

34.图8为本实施例2中ain压电薄膜水听器芯片的局部结构示意图。

35.其中,1-soi基片,2-ain压电层,3-电极层,4-正电极,5-负电极,6-二氧化硅,7-空腔,8-缺口,9-水听器芯片单元,10-正电极输出端;

36.11-负电极输出端,12-下层硅,13-二氧化硅,14-上层硅。

具体实施方式

37.名词解释

38.压电效应是指电介质受到沿一定方向的外力作用而产生形变时,其内部就会产生极化现象,同时在它的两个相对表面出现正负相反的电荷;当外力去掉时,又恢复到不带电的状态,这种现象称为压电材料的正压电效应,利用压电效应制备的传感器称为压电传感器。

39.如图1示出了aln压电薄膜电荷分布情况,由图1能够看出,ain压电薄膜在受到外界压力激励时,ain压电薄膜的电荷分布情况如下:

40.ain压电薄膜产生的正电荷主要集中在中心位置,边缘环状位置为负电荷。

41.针对aln压电薄膜的这一压电特性,本实施例设计出了新的ain压电薄膜水听器芯片单元结构,通过该水听器芯片单元,能够实现对aln压电薄膜有效的电荷采集。

42.下面结合附图以及具体实施方式对本发明作进一步详细说明:

43.实施例1

44.本实施例1述及了一种ain压电薄膜水听器芯片单元。

45.如图2所示,ain压电薄膜水听器芯片单元包括soi基片1、ain压电层2以及电极层3;其中,soi基片1、ain压电层2以及电极层3由下向上依次设置。

46.ain压电层2是在soi基片1上通过磁控溅射生成的。

47.ain压电层2为声压感测单元,在受到外界声压信号激励时发生形变,ain压电层2发生形变时,基于其压电效应产生电荷信号,完成声压的感测。

48.其中,电极层3与ain压电层2的外缘轮廓均为圆形,且外缘轮廓的大小均相同。

49.如图3所示,电极层3包括正电极4以及负电极5。

50.其中,正电极4和负电极5为同心设置,正电极4设置于电极层3的中心区域,且呈圆形;负电极5设置于电极层3的外侧边缘区域,且呈环形。

51.正电极4所占面积为电极层3面积的70%,负电极5所占面积为电极层3面积的20%。

52.其中,设置于电极层3中心区域的正电极4,用于收集ain压电薄膜产生的正电荷,设置于电极层3外侧边缘区域的负电极5收集ain压电薄膜产生的负电荷。

53.本实施例1中正电极4和负电极5优选采用mo电极,其成型过程如下:

54.首先在ain压电层2上磁控溅射生长一层电极层3,然后对电极层3进行光刻刻蚀图形化,进而得到上述正电极4以及负电极5。

55.在电极层3上位于正电极4与负电极5之间的环形区域设有二氧化硅6,如图3所示。

56.二氧化硅6的作用在于保护ain压电层2。

57.soi基片1能够为双层ain压电薄膜水听器芯片单元的制备提供支撑,soi基片1的尺寸和厚度能够调节水听器芯片单元的谐振频率,实现对水听器频率响应范围的选择。

58.如图4和图5所示,在soi基片1的底部设有空腔7。空腔7的作用在于,当ain压电薄膜受到声压激励时,增加ain压电薄膜的形变量。

59.如图1所示,soi基片1包括由下向上依次设置的下层硅12、二氧化硅13以及上层硅14。其中,空腔7是在soi基片1底部进行深硅刻蚀所形成的。

60.本实施例1中空腔7由下向上穿过下层硅12。

61.二氧化硅13的作用在于,当通过ibe刻蚀进行深硅刻蚀时,刻蚀技术在遇到二氧化硅13时,刻蚀速度会明显降低,进而起到保护的作用,以保证刻蚀精度。

62.本实施例1通过改进电极层3上正负电极的排布方式,使得正负电极的排布方式与ain压电层2产生的电荷分布高度吻合,其中,通过正电极4能够有效采集ain压电层2产生的正电荷,通过负电极5则能够有效采集ain压电层2产生的负电荷。

63.由于本实施例1中正电极4和负电极5均能实现电荷的有效采集(负电极5的电位不再是0),因而,增加了正负电极之间的电势差,大大提高了压电电荷的采集效率。

64.此外,本实施例1中的水听器芯片单元与现有的三明治结构相比,还具有如下优势:

65.1.水听器芯片单元的制备成本和制备难度明显降低;

66.2.水听器芯片单元的厚度降低,进一步降低了ain压电薄膜水听器芯片单元的内应力,避免因ain压电薄膜的内应力导致的剥离现象,提高了耐用性。

67.实施例2

68.本实施例2述及了一种ain压电薄膜水听器芯片单元,该ain压电薄膜水听器芯片单元除以下技术特征与上述实施例1不同之外,其余技术特征均可参照上述实施例1。

69.如图6所示,本实施例2中的负电极5上设有供正电极引线的缺口8,通过设置该缺口8,方便ain压电薄膜水听器芯片单元在阵列化时,各个芯片单元中正电极4的连接。

70.实施例3

71.本实施例3述及了一种ain压电薄膜水听器芯片,该水听器芯片采用上述实施例1或2中的ain压电薄膜水听器芯片单元,以提高ain压电薄膜水听器芯片的灵敏度。

72.如图7和图8所示,一种ain压电薄膜水听器芯片,包括水听器芯片单元9、正电极输出端10以及负电极输出端11,水听器芯片单元9有多个。

73.其中,水听器芯片单元9采用上面实施例1或2述及的ain压电薄膜水听器芯片单元。

74.各个水听器芯片单元9采用阵列式排布。

75.其中,各个水听器芯片单元9的正电极4相连,且连接到正电极输出端10上;各个水听器芯片单元9的负电极5相连,且连接到负电极输出端11上。

76.本实施例3通过采用上述ain压电薄膜水听器芯片单元,利于提高压电电荷的采集效率,进而增加了正负电极的电势差(对比度),从而提高了水听器芯片的灵敏度。

77.在正常的压电测试情况下,本实施例3中ain压电薄膜水听器芯片,相比于采用三明治结构的ain压电薄膜水听器芯片而言,可实现芯片灵敏度两倍的提升,灵敏度明显提高。

78.实施例4

79.本实施例4述及了一种水听器,该水听器包括水听器芯片以及运算放大电路。其中,水听器芯片的正电极输出端10和负电极输出端11分别连接到运算放大电路上。

80.其中,水听器芯片采用上面实施例3中的ain压电薄膜水听器芯片。

81.本实施例4中的水听器采用上述ain压电薄膜水听器芯片,灵敏度明显提高。

82.此外,由于本实施例中的ain压电薄膜水听器芯片厚度相比于三明治结构的水听器芯片厚度降低,因而水听器的整体厚度降低,水听器芯片内应力降低,耐用性明显增强。

83.当然,以上说明仅仅为本发明的较佳实施例,本发明并不限于列举上述实施例,应当说明的是,任何熟悉本领域的技术人员在本说明书的教导下,所做出的所有等同替代、明

显变形形式,均落在本说明书的实质范围之内,理应受到本发明的保护。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1