用于DSP芯片电路可靠性的自动上下电测试系统及方法与流程

用于dsp芯片电路可靠性的自动上下电测试系统及方法

技术领域

1.本发明涉及测试技术领域,特别涉及一种用于dsp芯片电路可靠性的自动上下电测试系统及方法。

背景技术:

2.目前,在芯片上电后需要ate测试系统对电子电路进行测试,ate测试系统价格昂贵,且无法再高低温下进行测试,使用继电器进行上下电,存在继电器寿命问题,对芯片上电后的功能未进行测试,无法知道芯片在多次上下电后是否存在异常情况,且无法适应dsp芯片这种需要多路电源,对于不同的电源域有严格上下电顺序的芯片。

技术实现要素:

3.本发明提供了一种用于dsp芯片电路可靠性的自动上下电测试系统及方法,其目的是为了解决传统的上下测试方法采用ate测试系统,价格昂贵,无法在高低温下进行上下电测试,采用继电器进行上下电测试,存在继电器寿命问题,对dsp芯片上电后的功能未进行测试,无法知道芯片在多次上下电后是否存在异常情况,无法适应对于不同的电源域电压有严格上下电顺序的dsp芯片的问题。

4.为了达到上述目的,本发明的实施例提供了一种用于dsp芯片电路可靠性的自动上下电测试系统,包括:

5.pc;

6.可编程电源,所述可编程电源的第一端通过rs232接口与pc电连接;

7.htol底板,所述htol底板的gpio端与所述可编程电源的第二端电连接,所述htol底板的gpio端用于输出反馈信号,所述htol底板的第一端与所述可编程电源的第三端电连接;

8.htol顶板,所述htol顶板设置有多个,每个所述htol顶板均安装在所述htol底板上,每个所述htol顶板上均设置有dsp芯片,每个所述dsp芯片的io30端均与所述htol底板的gpio端电连接。

9.本发明的实施例还提供了用于dsp芯片电路可靠性的自动上下电测试方法,包括:

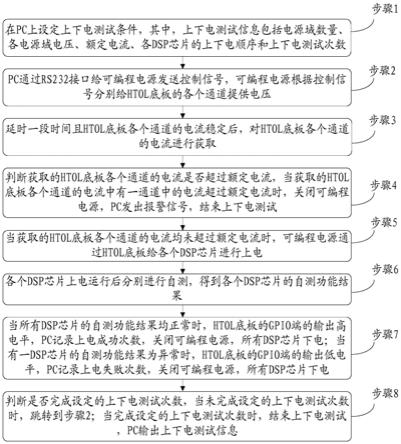

10.步骤1,在pc上设定上下电测试条件,其中,上下电测试信息包括电源域数量、各电源域电压、额定电流、各dsp芯片的上下电顺序和上下电测试次数;

11.步骤2,pc通过rs232接口给可编程电源发送控制信号,可编程电源根据控制信号分别给htol底板的各个通道提供电压;

12.步骤3,延时一段时间且htol底板各个通道的电流稳定后,对htol底板各个通道的电流进行获取;

13.步骤4,判断获取的htol底板各个通道的电流是否超过额定电流,当获取的htol底板各个通道的电流中有一通道中的电流超过额定电流时,关闭可编程电源,pc发出报警信号,结束上下电测试;

14.步骤5,当获取的htol底板各个通道的电流均未超过额定电流时,可编程电源通过htol底板给各个dsp芯片进行上电;

15.步骤6,各个dsp芯片上电运行后分别进行自测,得到各个dsp芯片的自测功能结果;

16.步骤7,当所有dsp芯片的自测功能结果均正常时,htol底板的gpio端的输出高电平,pc记录上电成功次数,关闭可编程电源,所有dsp芯片下电;当有一dsp芯片的自测功能结果为异常时,htol底板的gpio端的输出低电平,pc记录上电失败次数,关闭可编程电源,所有dsp芯片下电;

17.步骤8,判断是否完成设定的上下电测试次数,当未完成设定的上下电测试次数时,跳转到步骤2;当完成设定的上下电测试次数时,结束上下电测试,pc输出上下电测试信息。

18.其中,所述步骤2具体包括:

19.在pc上设定上下电测试条件后,延时一段时间执行以下步骤:

20.步骤21,可编程电源通过rs232接口接收pc发送的控制信号,可编程电源按各个dsp芯片的上下电顺序分别对htol底板的各个通道输入相对应的电源域电压。

21.其中,所述步骤6具体包括:

22.每个dsp芯片进行自测的步骤如下:

23.步骤61,dsp芯片上电后,dsp芯片运行预先加载在flash中的自测程序,自测程序控制dsp芯片的io30端输出低电平后进行dsp芯片自测,当dsp芯片自测成功后,dsp芯片的io30端输出高电平,表示dsp芯片上电后自测功能正常;当dsp芯片自测失败或dsp芯片的自测程序跑飞后,dsp芯片的io30端一直输出低电平,表示dsp芯片上电后自测功能异常。

24.其中,所述步骤7具体包括:

25.pc将上电成功次数或上电失败次数保存至log文本。

26.本发明的上述方案有如下的有益效果:

27.本发明的上述实施例所述的用于dsp芯片电路可靠性的自动上下电测试系统及方法,可以在常温、低温和高温下进行上下电测试,通过对dsp芯片上电后的自测功能进行测试,检测dsp芯片在多次上下电后是否存在异常情况,通过采用pc和可编程电源适应了对于不同的电源域电压有严格上下电顺序的dsp芯片,通用性强,节约了成本。

附图说明

28.图1为本发明的流程图;

29.图2为本发明的结构示意图。

30.【附图标记说明】

[0031]1‑

pc;2

‑

可编程电源;3

‑

htol底板;4

‑

htol顶板。

具体实施方式

[0032]

为使本发明要解决的技术问题、技术方案和优点更加清楚,下面将结合附图及具体实施例进行详细描述。

[0033]

本发明针对现有的上下测试方法采用ate测试系统,价格昂贵,无法在高低温下进

行上下电测试,采用继电器进行上下电测试,存在继电器寿命问题,对dsp芯片上电后的功能未进行测试,无法知道芯片在多次上下电后是否存在异常情况,无法适应对于不同的电源域电压有严格上下电顺序的dsp芯片的问题,提供了一种用于dsp芯片电路可靠性的自动上下电测试系统及方法。

[0034]

如图1至图2所示,本发明的实施例提供了一种用于dsp芯片电路可靠性的自动上下电测试系统,包括:pc1;可编程电源2,所述可编程电源2的第一端通过rs232接口与pc1电连接;htol底板3,所述htol底板3的gpio端与所述可编程电源2的第二端电连接,所述htol底板3的gpio端用于输出反馈信号,所述htol底板3的第一端与所述可编程电源2的第三端电连接;htol顶板4,所述htol顶板4设置有多个,每个所述htol顶板4均安装在所述htol底板3上,每个所述htol顶板4上均设置有dsp芯片,每个所述dsp芯片的io30端均与所述htol底板3的gpio端电连接。

[0035]

本发明的上述实施例所述的用于dsp芯片电路可靠性的自动上下电测试系统及方法,所述pc1通过rs232接口进行数据交互控制所述可编程电源2,包括各路电源的电压、各路电源的上电顺序、上电时间、上电次数、下电时间、下电次数和记录dsp芯片上电成功或上电失败次数;所述可编程电源2通过rs232接口接收来自所述pc1的控制信号,所述可编程电源2的多路电压输出通道分别与所述htol底板3相连,所述可编程电源2对不同的电压输出通道按设定的上下电顺序给所述dsp芯片上下电,同时使用一路通道接收来自所述htol底板3的反馈信号(高低电平),所述可编程电源2采用三通道可编程电源it6332a,将所述可编程电源2的第一通道和第二通道用于给dsp芯片提供3.3v电源域和1.8v电源域,将所述可编程电源2的第三通道连接到所述htol底板3的gpio端(反馈信号总线端),通过所述htol顶板4实现最小系统,并将大部分所述htol顶板4的管脚信号线引出至所述htol底板3,所述htol底板3用于提供所述htol顶板4的连接座,并对控制信号按测试要求做相应的处理,完成dsp芯片自测所需要的电路功能,同时将每一个dsp芯片的io30端作为反馈信号引出到所述htol底板3的gpio端,作为总反馈信号,dsp芯片采用adp32f035qp80s。

[0036]

本发明的上述实施例所述的用于dsp芯片电路可靠性的自动上下电测试系统及方法,反馈信号用于反馈上电后dsp芯片的自测功能是否正常,通过将所有dsp芯片的io30端与所述htol底板的gpio端连接在一起,所有dsp芯片上电正常并自测功能正常后拉高所述htol底板的gpio端输出的总反馈信号,反馈信号只有高低电平的区别。

[0037]

本发明的实施例提供了一种用于dsp芯片电路可靠性的自动上下电测试方法,包括:步骤1,在pc1上设定上下电测试条件,其中,上下电测试信息包括电源域数量、各电源域电压、额定电流、各dsp芯片的上下电顺序和上下电测试次数;步骤2,pc1通过rs232接口给可编程电源2发送控制信号,可编程电源2根据控制信号分别给htol底板3的各个通道提供电压;步骤3,延时一段时间且htol底板3各个通道的电流稳定后,对htol底板3各个通道的电流进行获取;步骤4,判断获取的htol底板3各个通道的电流是否超过额定电流,当获取的htol底板3各个通道的电流中有一通道中的电流超过额定电流时,关闭可编程电源2,pc1发出报警信号,结束上下电测试;步骤5,当获取的htol底板3各个通道的电流均未超过额定电流时,可编程电源2通过htol底板3给各个dsp芯片进行上电;步骤6,各个dsp芯片上电运行后分别进行自测,得到各个dsp芯片的自测功能结果;步骤7,当所有dsp芯片的自测功能结果均正常时,htol底板3的gpio端的输出高电平,pc1记录上电成功次数,关闭可编程电源2,

所有dsp芯片下电;当有一dsp芯片的自测功能结果为异常时,htol底板3的gpio端的输出低电平,pc1记录上电失败次数,关闭可编程电源2,所有dsp芯片下电;步骤8,判断是否完成设定的上下电测试次数,当未完成设定的上下电测试次数时,跳转到步骤2;当完成设定的上下电测试次数时,结束上下电测试,pc1输出上下电测试信息。

[0038]

本发明的上述实施例所述的用于dsp芯片电路可靠性的自动上下电测试系统及方法,使用所述可编程电源2给所述dsp芯片进行上电,而非特定电源芯片,存在很多优势:1)通道多,且每路通道都可单独设定精确电压(0.001v),对于需要多路不同电压电源的芯片,通过所述pc1可快速方便修改各通道电压,无需加入和更换硬件上的电源芯片;2)对每路通道设定电流保护,避免大电流损坏芯片。

[0039]

其中,所述步骤2具体包括:在pc1上设定上下电测试条件后,延时一段时间执行以下步骤:步骤21,可编程电源2通过rs232接口接收pc1发送的控制信号,可编程电源2按各个dsp芯片的上下电顺序分别对htol底板3的各个通道输入相对应的电源域电压。

[0040]

其中,所述步骤6具体包括:每个dsp芯片进行自测的步骤如下:步骤61,dsp芯片上电后,dsp芯片运行预先加载在flash中的自测程序,自测程序控制dsp芯片的io30端输出低电平后进行dsp芯片自测,当dsp芯片自测成功后,dsp芯片的io30端输出高电平,表示dsp芯片上电后自测功能正常;当dsp芯片自测失败或dsp芯片的自测程序跑飞后,dsp芯片的io30端一直输出低电平,表示dsp芯片上电后自测功能异常。

[0041]

其中,所述步骤7具体包括:pc1将上电成功次数或上电失败次数保存至log文本。

[0042]

本发明的上述实施例所述的用于dsp芯片电路可靠性的自动上下电测试系统及方法,dsp芯片在所述htol底板3上运行芯片自测程序,所有dsp芯片的io30端连接在一起作为所有dsp芯片给可编程电源2的总反馈信号,dsp芯片在上电之后将io30端置低,进行cpu、flash和外设等模块的自测,自测完成并且所有功能正常后将io30端置高,未完成或功能失效的io30端置低,在所有dsp芯片自测完成并且所有功能正常后,所述htol底板3的gpio端置高,所述htol底板3的gpio端输出总反馈信号给所述可编程电源2,表示所有dsp芯片上电后功能正常,pc1记录上电成功次数;一段时间内所述htol底板3的gpio端未置高说明存在dsp芯片上电后出现异常,pc1记录上电失败次数,重新上电继续完成上下电测试。

[0043]

本发明的上述实施例所述的用于dsp芯片电路可靠性的自动上下电测试系统及方法,不需要ate测试系统,可以在上下电测试中对dsp芯片进行功能自测,可以适应多种电源域,节约成本,对比大型的自动上下电装置,所述用于dsp芯片电路可靠性的自动上下电测试系统及方法只需要pc1、可编程电源2、所述htol底板3和所述htol顶板4,测试过程可监控,通过所述pc1可以对上下电次数、上电成功次数和上电失败次数等进行监测,通用性强,对于不同电源域、不同上电顺序的dsp芯片,只需修改在所述pc1设定的上下电信息。

[0044]

本发明的上述实施例所述的用于dsp芯片电路可靠性的自动上下电测试系统及方法,主要用于可靠性的上下电实验,既包括对芯片的有时序要求的上电控制,同时还有对芯片上电后的自测,自测后芯片功能失效与否的记录,之后对芯片进行下电操作,同时对以上这一操作在高温、低温和常温进行上万次循环测试并记录,以检验以dsp芯片为核心的整机系统在常温、低温和高温上电后下启动程序是否存在异常情况。

[0045]

以上所述是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明所述原理的前提下,还可以作出若干改进和润饰,这些改进和润饰也

应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1