一种芯片功能测试系统和方法与流程

1.本发明涉及集成电路测试技术领域,特别涉及一种芯片功能测试系统和方法。

背景技术:

2.近年来,随着集成电路设计的高速迅猛发展,系统结构由多个分立器件组成发展到由集成器件组成的阶段,又随着系统结构逐渐向追求小薄轻和低功耗的阶段发展,由此引起了芯片设计从集成器件向系统级封装sip(system in package)芯片迈进。芯片越来越小,功能越来越多,性能越来越强,如何验证功能在封装后是否正常,也成了行业亟需解决的问题。

3.sip芯片的功能参数主要涉及flash数据存取、ddr数据存取、uart通信、i2c通信、arm核间通信、axi通信、adc采集、mio输入输出、emio输入输出、浮点运算等。目前测试sip芯片主要还是使用自动测试设备ate测试平台针对于电路级测试,而sip芯片不再是传统的、单一的集成电路芯片,而是封装了zynq芯片、ddr、flash等集成电路芯片组成的一个微系统,对于sip芯片的功能测试就显得尤为重要。

技术实现要素:

4.本发明的提供一种芯片功能测试系统,以解决现有技术中ate对于sip芯片测试不充分的问题。

5.本发明提供的一种芯片功能测试系统,技术方案如下:一种芯片功能测试系统,包括上位机、激励测试载板和待测芯片载板,所述待测芯片载板与所述激励测试载板连接,所述上位机与所述激励测试载板连接;所述上位机能够发送测试指令,并接收所述激励测试载板反馈的测试结果;所述激励测试载板能够根据所述测试指令确定是否启动相应的测试功能项,并将所述测试指令发送至所述待测芯片载板,以及能够将所述待测芯片载板的测试结果发送至所述上位机;所述待测芯片载板能够安装待测芯片,所述待测芯片能够根据所述激励测试载板是否启动相应的测试功能项执行不同的测试流程,并得到测试结果。

6.进一步地,所述激励测试载板能够根据所述测试指令确定是否启动相应的测试功能项,包括:所述激励测试载板能够解析所述测试指令,并得到包括待测功能项的解析结果,根据所述解析结果的待测功能项与自身预设的测试功能项进行匹配,若匹配一致,则确定启动与所述待测功能项对应的测试功能项;若匹配不一致,则不启动自身的测试功能项。

7.进一步地,所述待测芯片能够根据所述激励测试载板是否启动相应的测试功能项执行不同的测试流程,并得到测试结果,包括:当所述激励测试载板启动测试功能项时,所述待测芯片能够根据所述测试指令启动与所述测试功能项对应的第一测试流程,并与所述激励测试载板配合执行第一测试流程

得到测试结果;当所述激励测试载板未启动测试功能项时,所述待测芯片能够根据所述测试指令启动与所述测试指令对应的第二测试流程,并执行第二测试流程得到测试结果。

8.进一步地,所述激励测试载板包括控制单元、第一时钟电路、第一复位电路和第一通讯接口,所述第一时钟电路、第一复位电路和第一通讯接口均与所述控制单元连接;所述控制单元能够与所述上位机、所述待测芯片载板进行数据交互,并能够启动相应的测试功能项;所述第一时钟电路能够为所述控制单元提供时钟信号;所述第一复位电路能够复位所述控制单元;所述第一通讯接口能够与所述上位机、所述待测芯片载板和外部仿真器连接。

9.进一步地,所述控制单元包括fpga芯片。

10.进一步地,所述第一通讯接口包括rs232接口、高速连接器和jtag接口,所述rs232接口、高速连接器和jtag接口均与所述控制单元连接;所述rs接口用于与所述上位机连接;所述高速连接器用于与所述待测芯片载板连接;所述jtag接口用于与外部仿真器连接。

11.进一步地,所述待测芯片载板包括芯片插槽、第二时钟电路、第二复位电路和第二通讯接口,所述第二时钟电路、第二复位电路和第二通讯接口均与所述芯片插槽连接;所述芯片插槽能够安装待测芯片;所述第二时钟电路能够为所述待测芯片提供时钟信号;所述第二复位电路能够复位所述待测芯片;所述第二通讯接口能够与所述激励测试载板和外部仿真器连接。

12.进一步地,还包括互联底板,所述互联底板用于连接激励测试载板与待测芯片载板,并为所述待测芯片载板和所述激励测试载板供电。

13.进一步地,所述互联底板包括两个高速连接器与供电电路;两个所述高速连接器分别连接所述待测芯片载板和所述激励测试载板;所述供电电路用于所述待测芯片载板和所述激励测试载板供电。

14.本发明还提供了一种芯片功能测试方法,应用于上述任意一项所述的芯片功能测试系统,其特征在于,包括:接收上位机发送的测试指令;能够根据所述测试指令确定是否启动相应的测试功能项;将所述测试指令发送至待测芯片载板;接收所述待测芯片载板的测试结果,并将所述测试结果发送至所述上位机。

15.本发明的有益效果:本发明的激励测试载板用于接收上位机发送的测试功能或测试性能的测试指令并进行解析,并将测试数据发送给待测芯片载板,且如果是对mio或emio的测试项,则进行相应测试功能项的启动;激励测试载板亦用于接收待测芯片载板发送的测试结果,并将测试结果发送给上位机。本发明通过使用激励测试载板进行芯片的mio或emio等功能项的测试可裁减及可扩增性强;采用互联底板架构设计,可自由组合测试方法及步骤,灵活性强;通过增加了上位机功能,可以灵活的通过上位机软件自动的完成测试项

的配置、发送、接收测试数据,并将测试结果显示更新,测试结果的实时、直接显示方式可以让测试人员快捷得到测试结论,并可保存测试报告用来对产品具体追踪、分析。

附图说明

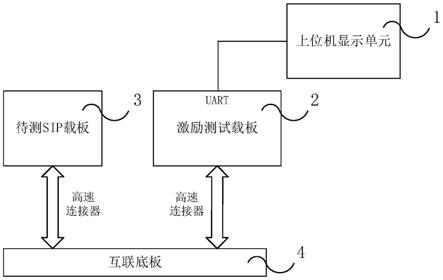

16.图1是本发明提供的芯片功能测试系统的结构示意图。

17.图2为激励测试载板结构示意图。

18.图3为待测芯片载板结构示意图。

19.图4为激励测试载板程序接收功能设计示意图。

20.图5为激励测试载板程序发送功能设计示意图。

21.图6为待测芯片载板程序设计示意图。

22.图7为互联底板结构示意图。

具体实施方式

23.为了使本领域技术人员更好地理解本发明方案,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,所描述的实施例仅仅是本发明一部分的实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都应当属于本发明保护的范围。

24.在本发明的实施例中,图1是根据本发明的实施例结构所提供的结构示意框图。如图1所示,本发明的实施例包括上位机1、激励测试载板2和待测芯片载板3,所述待测芯片载板3与所述激励测试载板2连接,所述上位机1与所述激励测试载板2连接。

25.所述上位机1能够发送测试指令,并接收所述激励测试载板2反馈的测试结果。

26.其中,上位机1运行测试软件,下发测试功能或测试性能的测试指令;同时接收测试完成后的测试结果数据,并实时显示、保存、更新。测试结果数据包括但不限于flash数据存取、ddr数据存取、uart通信、i2c通信、arm核间通信、axi通信、adc采集、mio输入输出、emio输入输出、浮点运算等测试结果,通过上位实时更新并显示便于让测试人员快捷得到测试结论,同时可以保存测试报告用来对产品具体追踪、分析。

27.所述激励测试载板2能够根据所述测试指令确定是否启动相应的测试功能项,并将所述测试指令发送至所述待测芯片载板3,以及能够将所述待测芯片载板3的测试结果发送至所述上位机1。

28.激励测试载板2能够解析所述测试指令,并得到包括待测功能项的解析结果,根据所述解析结果的待测功能项与自身预设的测试功能项进行匹配,若匹配一致,则确定启动与所述待测功能项对应的测试功能项;若匹配不一致,则不启动自身的测试功能项。

29.其中,所述激励测试载板2接收上位机1发送的的测试指令并进行解析,并将测试指令转发给待测芯片载板3。如果该测试指令是对mio或emio的测试项,则进行相应测试功能项的启动。后续激励测试载板2可通过拓展实现更多功能的测试。激励测试载板接收到待测芯片载板3发送的测试结果后转发到上位机,上位机将测试结果进行显示、更新及保存。

30.所述待测芯片载板3能够安装待测芯片,所述待测芯片能够根据所述激励测试载板2是否启动相应的测试功能项执行不同的测试流程,并得到测试结果。

31.其中,当所述激励测试载板2启动测试功能项时,所述待测芯片能够根据所述测试

指令启动与所述测试功能项对应的第一测试流程,并与所述激励测试载板2配合执行第一测试流程得到测试结果;当所述激励测试载板2未启动测试功能项时,所述待测芯片能够根据所述测试指令启动与所述测试指令对应的第二测试流程,并执行第二测试流程得到测试结果。

32.所述待测芯片载板安装有待测芯片,待测芯片接收激励测试载板发送的测试指令后进行解析,并进行相应测试的测试流程,待测芯片亦负责将测试结果经组合后发送给激励测试载板。

33.本发明通过使用激励测试载板进行芯片的mio或emio等功能项的测试可裁减及可扩增性强;采用互联底板架构设计,可自由组合测试方法及步骤,灵活性强。同时,本发明增加了上位机功能,可以灵活的通过上位机软件自动的完成测试项的配置、发送、接收测试数据,并将测试结果显示更新,测试结果的实时、直接显示方式可以让测试人员快捷得到测试结论,并可保存测试报告用来对产品具体追踪、分析。

34.在本发明的一个实施例中,图2是根据激励测试载板的结构提供的结构示意图。如图2所示,所述激励测试载板2包括控制单元21、第一时钟电路22、第一复位电路23和第一通讯接口,所述第一时钟电路22、第一复位电路23和第一通讯接口均与所述控制单元21连接。

35.所述控制单元21能够与所述上位机、所述待测芯片载板进行数据交互,并能够执行相应的测试功能项。所述控制单元21包括fpga芯片。fpga芯片为激励测试载板的核心控制单元,与所述上位机、待测sip载板通信,且可执行部分测试功能项,具体的程序设计过程请参阅图4、图5。

36.所述第一时钟电路22能够为所述控制单元21提供时钟信号。所述第一复位电路23能够复位所述控制单元21。所述第一通讯接口能够与所述上位机1、所述待测芯片载板3和外部仿真器连接。其中,所述第一通讯接口包括rs232接口、高速连接器和jtag接口,所述rs232接口、高速连接器和jtag接口均与所述控制单元21连接。所述rs232接口用于与所述上位机连接。所述高速连接器用于与所述待测芯片载板3连接。所述jtag接口用于与外部仿真器连接。jtag接口可以连接外部仿真器,供调试、仿真及固化fpga程序使用。

37.激励测试载板2还包括过流过压保护电路、供电电路、状态指示电路等外围电路;其中,所述过流过压保护电路连接所述外部供电电源,同时与所述激励测试载板2的供电电路,当电流或电压值超过设定范围时,通过切断电路实现对电路元件和线路的保护。所述供电电路为所述激励测试载板2供电。所述状态指示电路指示激励测试载板的工作运行状态。

38.在本发明的一个实施例中,图3是根据待测芯片载板的结构提供的结构示意图。如图3所示,所述待测芯片载板3包括芯片插槽31、第二时钟电路32、第二复位电路33和第二通讯接口,所述第二时钟电路32、第二复位电路33和第二通讯接口均与所述芯片插槽31连接。

39.所述芯片插槽31能够安装待测芯片,与激励测试载板2通信,待测芯片可执行部分测试功能项,包括但不限于flash数据存取、ddr数据存取、uart通信、i2c通信、arm核间通信、axi通信、adc采集、mio输入输出、emio输入输出、浮点运算等,具体的程序设计过程请参阅图6。所述第二时钟电路32能够为所述待测芯片提供时钟信号,所述第二复位电路33能够复位所述待测芯片。

40.所述第二通讯接口能够与所述激励测试载板2和外部仿真器连接。其中,所述第二通讯接口包括高速连接器和jtag接口,所述高速连接器和jtag接口均与所述芯片插槽31连

接。所述高速连接器用于与所述激励测试载板2连接。所述jtag接口用于与外部仿真器连接。jtag接口可以连接外部仿真器,供调试、仿真及固化芯片程序使用。

41.待测芯片载板还包括过流过压保护电路、供电电路等外围电路,其中,所述过流过压保护电路连接外部电源与待测芯片载板的供电电路,当电流或电压值超过设定范围时,通过切断电路实现对电路元件和线路的保护。

42.在本发明的一个实施例中,本系统还包括互联底板4,所述互联底板4分别与所述待测芯片载板3和所述激励测试载板2连接。所述互联底板4用于连接激励测试载板2与待测芯片载板3,实现接激励测试载板2与待测芯片载板3之间的信号传输与信息交换,同时为所述待测芯片载板3和所述激励测试载板2供电。图4是根据互联底板的结构提供的结构示意图。如图4所示,所述互联底板4包括两个高速连接器与供电电路。两个所述高速连接器分别连接所述待测芯片载板3和所述激励测试载板2。所述供电电路用于为所述待测芯片载板3和所述激励测试载板2供电,所述互联底板的供电电路分别与所述待测芯片载板3的供电电路和所述激励测试载板2的供电电路连接。

43.需要注意的是,本发明中提及的时钟电路、复位电路、过流过压保护电路、供电电路的结构均为本领域技术人员所熟知,故不再赘述。

44.本发明中还提供了一种供上述任一芯片功能测试系统使用的芯片功能测试方法,流程图如图4与图5所示,包括:接收上位机1发送的测试指令;用户能够根据实际需求,使用上位机1发送测试指令。同时上位机1也是数据终端,能够保存、显示测试激励载板转发的测试结果。

45.能够根据所述测试指令确定是否启动相应的测试功能项;测试激励载板2能够分析测试指令,执行测试激励载板所能执行的测试功能,具体为mio或emio功能测试,后续可进行拓展。

46.将所述测试指令发送至待测芯片载板3;接收所述待测芯片载板3的测试结果,并将所述测试结果发送至所述上位机1。

47.本发明提供测试方法配合测试系统使用,能够对sip芯片进行功能的测试,解决了现有技术只能对sip芯片进行电路级别测试的问题。

48.最后所应说明的是,以上具体实施方式仅用以说明本发明的技术方案而非限制,尽管参照实例对本发明进行了详细说明,本领域的普通技术人员应当理解,可以对本发明的技术方案进行修改或者等同替换,而不脱离本发明技术方案的精神和范围,其均应涵盖在本发明的权利要求范围当中。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1