检测电路及检测方法与流程

1.本发明涉及一种检测电路及方法。详细而言,本发明涉及一种检测电路及检测方法,检测电路及检测方法用以检测存储器芯片。

背景技术:

2.于现有技术中,聚焦离子束(focused ion beam,fib)电路修补技术已使用于存储器芯片,以理解复数个字线或复数个位线的漏电流。聚焦离子束(focused ion beam,fib)电路修补技术经常采用聚焦离子束来修改电路芯片或存储器芯片的逻辑电路或电路连接关系。

3.由于聚焦离子束(focused ion beam,fib)电路修补技术的聚焦离子束,从存储器芯片的边缘至中心的复数个字线或复数个位线经常被烧毁以进行电性分析。然而,使用聚焦离子束会导致电路芯片或存储器芯片损坏。因此,技术人员无法知道漏电流是由电路芯片或存储器芯片的何处产生。

4.因此,上述技术尚存诸多缺陷,而有待本领域技术人员研发出其余适合的检测方法。

技术实现要素:

5.本发明的一面向涉及一种检测方法。检测方法用以检测存储器芯片。检测方法包含以下步骤:耦接检测电路至存储器芯片的第一区域及第二区域,其中第二区域与第一区域不互相重叠;从检测电路输入第一检测信号至存储器芯片的第一区域;烧毁检测电路的记忆格;以及从检测电路输入第二检测信号至存储器芯片的第二区域。

6.在一些实施例中,从检测电路输入第一检测信号至存储器芯片的第一区域的步骤包含:判断存储器芯片的第一区域是否正常;从检测电路输入第二检测信号至存储器芯片的第二区域的步骤包含:判断存储器芯片的第二区域是否正常。

7.在一些实施例中,检测方法还包含:导通检测电路的开关以作为电阻,借以根据控制信号传送第二检测信号至存储器芯片的第二区域。

8.在一些实施例中,检测方法还包含:于制造过程中从存储器芯片移除检测电路。

9.在一些实施例中,存储器芯片还包含复数个字线及复数个位线。从检测电路输入第一检测信号至存储器芯片的第一区域的步骤包含:分别输入复数个检测信号至复数个字线或复数个位线。

10.在一些实施例中,从检测电路输入第一检测信号至存储器芯片的第一区域的步骤包含:同时输入复数个检测信号至复数个字线及复数个位线。

11.本发明的另一面向涉及一种检测电路。检测电路用以检测存储器芯片。检测电路包含:输入板以及记忆格。输入板,耦接于存储器芯片的第一区域。输入板用以输入第一检测信号至存储器芯片的第一区域。记忆格耦接于输入板及存储器芯片的第二区域。第二区域与第一区域不互相重叠。记忆格被烧毁,以使得输入板输入第二检测信号至存储器芯片

的第二区域。

12.在一些实施例中,检测电路还包含开关。开关被导通以作为电阻,借以根据控制信号传送第二检测信号至存储器芯片的第二区域。

13.在一些实施例中,存储器芯片包含二维数组存储器及三维存储器。存储器芯片包含复数个字线及复数个位线。复数个字线垂直于复数个位线。复数个字线及复数个位线于存储器芯片形成网格矩阵。网格矩阵包含第一部分及第二部分。第二部分环绕第一部分。第二部分与第一部分不互相重叠。检测电路包含第一检测电路及第二检测电路。第一检测电路耦接于复数个字线。第二检测电路耦接于复数个位线。

14.在一些实施例中,检测电路还包含复数个检测板。复数个检测板用以回传第一检测信号及第二检测信号的复数个检测结果至输入板。

附图说明

15.参照后续段落中的实施方式以及下列附图,当可更佳地理解本发明的内容:

16.图1为根据本发明一些实施例绘示的存储器芯片及检测电路的电路方块示意图;

17.图2为根据本发明一些实施例绘示的检测方法的步骤流程示意图;

18.图3为根据本发明一些实施例绘示的存储器芯片及检测电路的电路状态示意图;

19.图4为根据本发明一些实施例绘示的存储器芯片及检测电路的电路状态示意图;

20.图5为根据本发明一些实施例绘示的存储器芯片及检测电路的电路方块示意图;

21.图6为根据本发明一些实施例绘示的存储器芯片及检测电路的电路方块示意图;以及

22.图7为根据本发明一些实施例绘示的存储器芯片及两个检测电路的电路方块示意图。

具体实施方式

23.以下将以附图及详细叙述清楚说明本发明的精神,任何本领域技术人员在了解本发明的实施例后,当可由本发明所教示的技术,加以改变及修饰,其并不脱离本发明的精神与范围。

24.本文的用语只为描述特定实施例,而无意为本发明的限制。单数形式如“一”、“这”、“此”、“本”以及“该”,如本文所用,同样也包含复数形式。

25.关于本文中所使用的“包含”、“包括”、“具有”、“含有”等等,均为开放性的用语,即意指包含但不限于。

26.关于本文中所使用的用词(terms),除有特别注明外,通常具有每个用词使用在此领域中、在本发明的内容中与特殊内容中的平常意义。某些用以描述本发明的用词将于下或在此说明书的别处讨论,以提供本领域技术人员在有关本发明的描述上额外的引导。

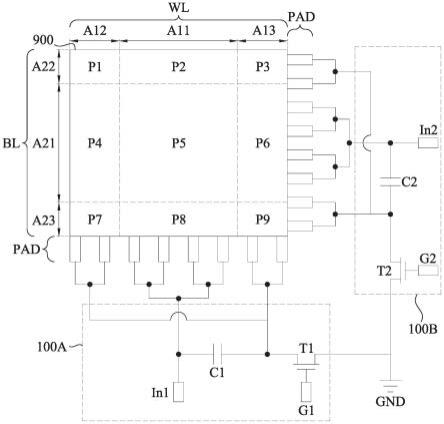

27.图1为根据本发明一些实施例绘示的存储器芯片900及检测电路100的电路方块示意图。在一些实施例中,请参阅图1,存储器芯片900包含复数个字线wl(附图中所有纵向的线均代表字线)以及复数个位线bl(附图中所有横向的线均代表位线)。在一些实施例中,复数个字线垂直于复数个位线。在一些实施例中,存储器芯片900包含二维(two-dimensional,2d)数组存储器及三维(three-dimensional,3d)存储器。在一些实施例中,存

储器芯片9001包含动态随机存取存储器(dynamic random access memory,dram)。

28.在一些实施例中,检测电路100包含输入板in1、记忆格c1及开关t1。输入板in1耦接于存储器芯片900。请从附图中每一元件的上端及右端起算为第一端,记忆格c1包含第一端及第二端。记忆格c1的第一端耦接于存储器芯片900。记忆格c1的第二端耦接于输入板in1。

29.在一些实施例中,开关t1包含第一端、第二端及控制端。开关t1的第一端耦接于接地端gnd。开关t1的第二端耦接于记忆格c1以及存储器芯片900。开关t1的控制端耦接于闸极控制板g1。开关t1响应闸极控制板g1所输入的控制信号,以进行导通或关闭。开关t1包含p型金属氧化物半导体场效应晶体管(metal-oxide-semiconductor field-effect transistor,mosfet)或n型金属氧化物半导体场效应晶体管(metal-oxide-semiconductor field-effect transistor,mosfet)。

30.在一些实施例中,复数个检测板pad位于检测电路100及存储器芯片900之间。复数个检测板pad用以传输单向或双向的复数个检测信号。在一些实施例中,复数个检测板pad耦接于检测电路100以及存储器芯片900。复数个检测板pad用以回传复数个检测信号的复数个检测结果输入板in1。

31.在一些实施例中,为使本发明图1的用以检测电路100易于理解,检测电路100用以检测存储器芯片900。请一并参阅图2至图4,图2为根据本发明一些实施例绘示的检测方法200的步骤流程示意图。图3及图4为根据本发明一些实施例绘示的存储器芯片900及检测电路100的电路状态示意图。须说明的是,图3及图4的实施例为检测电路100用以独自检测存储器芯片900的复数个字线wl。图3所示的存储器芯片900对应至图1的存储器芯片900。检测方法200用以检测存储器芯片。检测方法200包含以下步骤:

32.于步骤210中,耦接检测电路至存储器芯片的第一区域及第二区域。

33.在一些实施例中,请参阅图2及图3,检测电路100的输入板in1耦接于存储器芯片900的第一区域a11及第二区域(例如:区域a12及区域a13)。第二区域(例如:区域a12及区域a13)与第一区域a11不互相重叠。详细而言,第一区域a11为复数个字线的中央区域。区域a12及区域a13位于第一区域a11的两侧。须说明的是,每一区域a11、区域a12及区域a13的尺寸及长度不以附图实施例为限。

34.于步骤220中,从检测电路输入第一检测信号至存储器芯片的第一区域。

35.在一些实施例中,输入板in1用以从检测电路100沿如图3所示的路径r1输入第一检测信号至存储器芯片900的第一区域a11。复数个检测板pad用以回传第一检测信号的第一检测结果至输入板in1。输入板in1用以根据传第一检测信号的第一检测结果判断存储器芯片900的第一区域a11是否正常。于此同时,开关t1响应闸极控制板g1的控制信号,以进行关闭。

36.于步骤230中,烧毁检测电路的记忆格。

37.在一些实施例中,请参阅图2及图4,记忆格c1被烧毁以形成短路,短路路径如图4所示沿路径r2。于此同时,开关t1响应闸极控制板g1的控制,以导通,借以作为电阻使得自输入板in1的信号可以被传送至存储器芯片900的第二区域(例如:区域a12及区域a13)。须说明的是,附图中的闪电符号代表记忆格c1被烧毁以及无法被复原或被修复。

38.于步骤240中,从检测电路输入第二检测信号至存储器芯片的第二区域。

39.在一些实施例中,请参阅图2及图4,输入板in1用以从检测电路100沿如图4所示的路径r2输入第二检测信号至存储器芯片900的第二区域(例如:区域a12及区域a13)。复数个检测板pad回传第二检测信号的第二检测结果至输入板in1。输入板in1用以根据第二检测信号的第二检测结果判断存储器芯片900的第二区域(例如:区域a12及区域a13)是否正常。

40.于步骤250中,从存储器芯片移除检测电路。

41.在一些实施例中,在存储器芯片900的制造过程中从存储器芯片移除检测电路100。详细而言,在存储器芯片900的制造过程的后段检测过程中移除检测电路100。

42.图5为根据本发明一些实施例绘示的存储器芯片900及检测电路100的电路方块示意图。在一些实施例中,相较于图3及图4,图5的实施例与图3及图4的实施例的差异点在于改变存储器芯片900及检测电路100的连接关系。详细而言,检测电路100沿路径r2’耦接至第一区域a11以及检测电路100沿路径r1’耦接至第二区域(例如:区域a12及区域a13)。

43.在一些实施例中,与上述步骤220的差异点在于检测电路100的输入板in1用以自检测电路100沿路径r1’输入第一检测信号至第二区域(例如:区域a12及区域a13)。在一些实施例中,与上述步骤220的另一差异点在于检测电路100的输入板in1用以自检测电路100沿路径r2’输入第二检测信号至第一区域a11。其余步骤均相同,已于上述步骤叙述,于此不作赘述。

44.图6为根据本发明一些实施例绘示的存储器芯片900及检测电路100的电路方块示意图。相较于图3及图4,图6的实施例为检测电路100用以独自检测存储器芯片900的复数个位线bl。如图6所示的存储器芯片900对应于图1所示的存储器芯片900。

45.在一些实施例中,请参阅图6,如图6所示的检测电路100的输入板in2沿路径r3耦接于存储器芯片900的复数个位线bl的区域a21。如图6所示的检测电路100的输入板in2沿路径r4耦接于存储器芯片900的复数个位线bl的区域a22及区域a23。详细而言,区域a21位于复数个位线bl的中央区域。区域a22及区域a23位于区域a21的两侧。须说明的是,每一区域a21、区域a22及区域a23的尺寸及长度不以附图实施例为限。

46.图7为根据本发明一些实施例绘示的存储器芯片900、检测电路100a及检测电路100b的电路方块示意图。图7的实施例与图3、图4、图5及图6的实施例的差异点在于检测电路的数量改变。检测电路包含第一检测电路100a及第二检测电路100b。第一检测电路100a及第二检测电路100b耦接于存储器芯片900。如图7所示的第一检测电路100a及第二检测电路100b与前述图1、图3及图6的检测电路均相同。

47.须说明的是,第一检测电路100a及第二检测电路100b同时检测存储器芯片900的复数个字线wl与复数个位线bl。详细而言,第一检测信号与第二检测信号同时输入至存储器芯片900。第一检测信号与第二检测信号互相不干扰。

48.在一些实施例中,如图7所示,复数个字线wl与复数个位线bl于存储器芯片形成一种网格矩阵(例如:如图7所示的方阵)。网格矩阵包含9个网格。9个网格的排列顺序从左至右及从上至下分别为第一网格p1、第二网格p2、第三网格p3、第四网格p4、第五网格p5、第六网格p6、第七网格p7、第八网格p8及第九网格p9。在一些实施例中,网格矩阵包含第一部分(例如:第五网格p5)及第二部分(例如:网格p1至p4以及网格p6至p9)。第二部分环绕第一部分。第一部分及第二部分互相不重叠。

49.在一些实施例中,复数个字线wl的区域a12与复数个位线bl的区域a22部分重叠以

形成第一网格p1。在一些实施例中,复数个字线wl的区域a11与复数个位线bl的区域a22部分重叠以形成第二网格p2。在一些实施例中,复数个字线wl的区域a13与复数个位线bl的区域a22部分重叠以形成第三网格p3。

50.在一些实施例中,复数个字线wl的区域a12与复数个位线bl的区域a21部分重叠以形成第四网格p4。在一些实施例中,复数个字线wl的区域a11与复数个位线bl的区域a21部分重叠以形成第五网格p5。在一些实施例中,复数个字线wl的区域a13与复数个位线bl的区域a21部分重叠以形成第六网格p6。

51.在一些实施例中,复数个字线wl的区域a12与复数个位线bl的区域a23部分重叠以形成第七网格p7。在一些实施例中,复数个字线wl的区域a11与复数个位线bl的区域a23部分重叠以形成第八网格p8。在一些实施例中,复数个字线wl的区域a13与复数个位线bl的区域a23部分重叠以形成第九网格p9。

52.在一些实施例中,存储器芯片900与第一检测电路100a之间的电路连接关系根据实际需求设计。存储器芯片900与第二检测电路100b之间的电路连接关系根据实际需求设计。

53.在一些实施例中,如图7所示,第一部分实际上为存储器芯片900的中央部分,第二部分实际上为存储器芯片900的周遭部分。须说明的是,每一中央部分及周遭部分的形状及尺寸不以附图实施例为限。

54.须说明的是,本发明的检测电路及检测方法主要用以检测存储器芯片900的中央部分及周遭部分,借以判断忆体芯片900的每一中央部分及周遭部分是否正常。再者,存储器芯片的复数个字线及复数个位线能被同时检测,借以节省检测存储器芯片的检测时间。

55.依据前述实施例,本发明提供一种检测电路及检测方法,借以节省检测存储器芯片的检测时间及成本,以及避免存储器芯片于检测中受到损坏。

56.虽然本发明以详细的实施例揭露如上,然而本发明并不排除其他可行的实施态样。因此,本发明的保护范围当视后附的权利要求书所界定者为准,而非受于前述实施例的限制。

57.对本领域技术人员而言,在不脱离本发明的精神和范围内,当可对本发明作各种的更动与润饰。基于前述实施例,所有对本发明所作的更动与润饰,亦涵盖于本发明的保护范围内。

58.【符号说明】

59.100,100a,100b:检测电路

60.t1,t2:开关

61.c1,c2:记忆格

62.g1,g2:闸极控制板

63.in1,in2:输入板

64.gnd:接地端

65.pad:检测板

66.900:存储器芯片

67.bl:位线

68.wl:字线

69.a11~a13,a21~a23:区域

70.p1~p9:网格

71.r1~r4,r1’~r2’:路径

72.200:方法

73.210~250:步骤。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1