轴角编码器测试电路的制作方法

1.本实用新型涉及轴角编码器测试设备领域,特别是涉及一种轴角编码器测试电路。

背景技术:

2.轴角编码器是将转轴的角位移或直线位移的模拟量转变成数字量输出的一种轴角(位)-数字转换器,在轴角编码器生产完成后,需要对其进行测试,以确定轴角编码器是否合格。

技术实现要素:

3.本实用新型的目的在于克服现有技术的一项或多项不足,提供一种轴角编码器测试电路。

4.本实用新型的目的是通过以下技术方案来实现的:轴角编码器测试电路,包括:

5.数码管模块,用于显示测试结果;

6.移位寄存器模块,与所述数码管模块电连接,用于驱动所述数码管进行显示;

7.电平模块,用于与轴角编码器电连接,用于接收所述轴角编码器输出的第一电平,并将所述第一电平转换为第二电平;

8.处理器模块,与所述移位寄存器模块和电平模块电连接,用于接收所述第二电平,并将所述第二电平发送至所述数码管进行显示;

9.电源模块,与所述处理器模块、移位寄存器模块和电平模块电连接。

10.优选的,所述轴角编码器测试电路还包括:

11.滤波放大模块,串联在电平模块和微处理器之间,用于对所述第二电平进行滤波和放大。

12.优选的,所述轴角编码器测试电路还包括:

13.线性稳压器,串接在所述电源模块和处理器模块之间。

14.优选的,所述电源模块包括:

15.电池;

16.保护电路,串接在所述电池和处理器模块之间,用于在过流或过压时断开电池与处理器模块、移位寄存器模块和电平模块之间的电连接。

17.优选的,所述电源模块还包括:

18.电量检测电路,与所述处理器模块和电池电连接,用于检测所述电池的剩余电量,并将检测结果发送给处理器模块;

19.报警器,与所述处理器模块连接;

20.所述处理器模块在所述电池的剩余电量低于阈值时控制所述报警器报警。

21.优选的,所述线性稳压器包括稳压芯片,所述稳压芯片的型号为asm1117

‑

3.3v。

22.优选的,所述处理器模块包括单片机,所述单片机的型号为stm32f103c。

23.优选的,所述移位寄存器模块包括多个移位寄存器,所述移位寄存器的型号为m74hc595m1r。

24.本实用新型的有益效果是:

25.(1)本实用新型能够检测轴角编码器输出的格雷码,并将格雷码转换为10进制数据显示至数码管,实现轴角编码器当前码值和跳码码值的检测;

26.(2)本实用新型利用电池供电,方便携带;

27.(3)本实用新型设有电量保护电路和电量检测电路,可以防止过充以及进行低电量报警。

附图说明

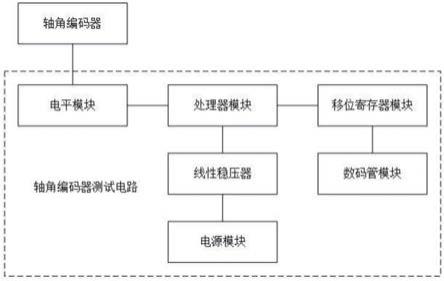

28.图1为轴角编码器测试电路的一种组成框图;

29.图2为处理器模块的一种电路图;

30.图3为线性稳压器的一种电路图;

31.图4为电平模块的一种电路图;

32.图5为移位寄存器模块的一种电路图;

33.图6为数码管模块的一种电路图;

34.图7为rs485模块的一种电路图;

35.图8为rs232模块的一种电路图。

具体实施方式

36.下面将结合实施例,对本实用新型的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本实用新型一部分实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域技术人员在没有付出创造性劳动的前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

37.参阅图1

‑

图8,本实施例提供了一种轴角编码器测试电路:

38.如图1所示,轴角编码器测试电路,包括处理器模块、数码管模块、移位寄存器模块、电平模块和电源模块。所述数码管模块用于显示测试结果;所述移位寄存器模块,与所述数码管模块电连接,用于驱动所述数码管进行显示;所述电平模块,用于与轴角编码器电连接,用于接收所述轴角编码器输出的第一电平,并将所述第一电平转换为第二电平;所述处理器模块,与所述移位寄存器模块和电平模块电连接,用于接收所述第二电平,并将所述第二电平发送至所述数码管进行显示;所述电源模块,与所述处理器模块、移位寄存器模块和电平模块电连接。

39.一般的,所述处理器模块包括单片机u1、晶振x1电路和复位电路,所述单片机u1分别与晶振x1电路和复位电路电连接。具体的,如图2所示,所述处理器模块包括单片机u1、晶振x1、第一电阻r1、第二电阻r2、第一电容c1、第二电容c2、第三电容c3、第四电容c4和第一开关s1,所述单片机u1的型号为stm32f103c,所述单片机u1的boot0端经第一电阻r1接地,所述单片机u1的vss_1端、vss_2端、vss_3端和vssa端接地,所述单片机u1的vdd_1端、vdd_2端、vdd_3端和vdda端与第一电容c1的第一端连接,所述单片机u1的vdda端接3.3v电压,所述第一电容c1的第二端接地,所述晶振x1的第一端经第二电容c2接地,所述晶振x1的第二

端经第三电容c3接地,所述晶振x1串接在单片机u1的osc_in端和osc_out端之间,所述第一开关s1的第一端接地,所述第一开关s1的第二端接单片机u1的nrst端,所述第一开关s1的第二端经第二电阻r2接3.3v电压,所述第四电容c4与第一开关s1并联。

40.在一些实施例中,所述轴角编码器测试电路还包括线性稳压器,所述线性稳压器串接在所述电源模块和处理器模块之间。线性稳压器通过对输出电压进行采样,然后反馈到调节电路去调节输出级调整管的阻抗,当输出电压偏低时,就调节输出级的阻抗变小从而减小调整管的压降,当输出电压偏高时,就调节输出级的阻抗变大从而增大调整管的压降,从而维持了输出电压的稳定。

41.具体的,如图3所示,所述线性稳压器包括稳压芯片u2、第三电阻r3、第五电容c5、第六电容c6和第七电容c7,所述稳压芯片u2的型号为asm1117

‑

3.3v,所述稳压芯片u2的输入端接电源模块的输出端,所述稳压芯片u2的输入端经第五电容c5接地,所述稳压芯片u2的输出端经第六电容c6接地,所述稳压芯片u2的输出端接第三电阻r3的第一端,所述第三电阻r3的第二端经第七电容c7接地,所述第三电阻r3的第二端接3.3v电压。

42.具体的,如图4所示,所述电平模块包括第四电阻r4、第五电阻r5、第六电阻r6、第七电阻r7、第八电阻r8和第九电阻r9,所述第五电阻r5、第六电阻r6、第七电阻r7、第八电阻r8和第九电阻r9均为排阻,所述第四电阻r4的第一端接3.3v电压,所述第四电阻r4的第二端分别与第五电阻r5、第六电阻r6、第七电阻r7、第八电阻r8和第九电阻r9的公共引脚连接,所述第五电阻r5的第一独立引脚接单片机u1的pb15端,所述第五电阻r5的第二独立引脚接单片机u1的pa11端,所述第五电阻r5的第三独立引脚接单片机u1的pa12端,所述第五电阻r5的第四独立引脚接单片机u1的pb8端,所述第六电阻r6的第一独立引脚接单片机u1的pb1端,所述第六电阻r6的第二独立引脚接单片机u1的pb2端,所述第六电阻r6的第三独立引脚接单片机u1的pb10端,所述第六电阻r6的第四独立引脚接单片机u1的pb11端,所述第七电阻r7的第一独立引脚接单片机u1的pa5端,所述第七电阻r7的第二独立引脚接单片机u1的pa6端,所述第七电阻r7的第三独立引脚接单片机u1的pa7端,所述第七电阻r7的第四独立引脚接单片机u1的pb0端,所述第八电阻r8的第一独立引脚接单片机u1的pc15端,所述第八电阻r8的第二独立引脚接单片机u1的pa0端,所述第八电阻r8的第三独立引脚接单片机u1的pa1端,所述第八电阻r8的第四独立引脚接单片机u1的pa4端,所述第九电阻r9的第一独立引脚接单片机u1的pb5端,所述第九电阻r9的第二独立引脚接单片机u1的pb6端,所述第九电阻r9的第三独立引脚接单片机u1的pb7端。

43.具体的,如图5所示,所述移位寄存器模块包括第一移位寄存器u3、第二移位寄存器u4、第三移位寄存器u5、第四移位寄存器u6、第五移位寄存器u7、第六移位寄存器u8、第七移位寄存器u9、第八移位寄存器u10、第十电阻r10、第十一电阻r11、第十二电阻r12、第十三电阻r13、第十四电阻r14、第十五电阻r15、第八电容c8和第九电容c9,第一移位寄存器u3、第二移位寄存器u4、第三移位寄存器u5、第四移位寄存器u6、第五移位寄存器u7、第六移位寄存器u8、第七移位寄存器u9和第八移位寄存器u10的型号为m74hc595m1r。所述第十电阻r10的第一端接单片机u1的pc13端,所述第十电阻r10的第二端经第八电容c8接地,所述第十电阻r10的第二端接5v电压,所述第十电阻r10的第二端分别与第一移位寄存器u3、第二移位寄存器u4、第三移位寄存器u5和第四移位寄存器u6的vcc端连接,所述第十电阻r10的第二端分别与第一移位寄存器u3、第二移位寄存器u4、第三移位寄存器u5和第四移位寄存

器u6的端连接。

44.所述第十一电阻r11的第一端与第十电阻r10的第二端连接,所述第十一电阻r11的第二端接单片机u1的pc14端,所述第十一电阻r11的第二端分别与第一移位寄存器u3、第二移位寄存器u4、第三移位寄存器u5和第四移位寄存器u6的srclk端连接。所述第十二电阻r12的第一端与第十电阻r10的第二端连接,所述第十二电阻r12的第二端接单片机u1的pb9端,所述第十二电阻r12的第二端接第一移位寄存器u3的ser端。

45.所述第一移位寄存器u3的端分别与第二移位寄存器u4、第三移位寄存器u5和第四移位寄存器u6的连接,所述第一移位寄存器u3的端与其gnd端连接,所述第一移位寄存器u3、第二移位寄存器u4、第三移位寄存器u5和第四移位寄存器u6的gnd端接地。所述第二移位寄存器u4的ser端接第一移位寄存器u3的qh'端连接,所述第三移位寄存器u5的ser端接第二移位寄存器u4的qh'端连接,所述第四移位寄存器u6的ser端接第三移位寄存器u5的qh'端连接。

46.所述第十三电阻r13的第一端接单片机u1的pc13端,所述第十三电阻r13的第二端经第九电容c9接地,所述第十三电阻r13的第二端接5v电压,所述第十三电阻r13的第二端分别与第五移位寄存器u7、第六移位寄存器u8、第七移位寄存器u9和第八移位寄存器u10的vcc端连接,所述第十三电阻r13的第二端分别与第五移位寄存器u7、第六移位寄存器u8、第七移位寄存器u9和第八移位寄存器u10的端连接。

47.所述第十四电阻r14的第一端与第十三电阻r13的第二端连接,所述第十四电阻r14的第二端接单片机u1的pc14端,所述第十四电阻r14的第二端分别与第五移位寄存器u7、第六移位寄存器u8、第七移位寄存器u9和第八移位寄存器u10的srclk端连接。所述第十五电阻r15的第一端与第十三电阻r13的第二端连接,所述第十五电阻r15的第二端接单片机u1的pb9端,所述第十五电阻r15的第二端接第五移位寄存器u7的ser端。

48.所述第五移位寄存器u7的端分别与第六移位寄存器u8、第七移位寄存器u9和第八移位寄存器u10的连接,所述第五移位寄存器u7的端与其gnd端连接,所述第五移位寄存器u7、第六移位寄存器u8、第七移位寄存器u9和第八移位寄存器u10的gnd端接地。所述第六移位寄存器u8的ser端接第五移位寄存器u7的qh'端连接,所述第七移位寄存器u9的ser端接第六移位寄存器u8的qh'端连接,所述第八移位寄存器u10的ser端接第七移位寄存器u9的qh'端连接。

49.具体的,如图6所示,所述数码管模块包括第一数码管u11、第二数码管u12和第十六电阻r16,所述第一数码管u11和第二数码管u12的型号为ca56数码管。

50.所述第一数码管u11的d1a端接第一移位寄存器u3的qa端,所述第一数码管u11的d1b端接第一移位寄存器u3的qb端,所述第一数码管u11的d1c端接第一移位寄存器u3的qc端,所述第一数码管u11的d1d端接第一移位寄存器u3的qd端,所述第一数码管u11的d1e端接第一移位寄存器u3的qe端,所述第一数码管u11的d1f端接第一移位寄存器u3的qf端,所述第一数码管u11的d1g端接第一移位寄存器u3的qg端,所述第一数码管u11的dp1端接第一移位寄存器u3的qh端;

51.所述第一数码管u11的d2a端接第二移位寄存器u4的qa端,所述第一数码管u11的d2b端接第二移位寄存器u4的qb端,所述第一数码管u11的d2c端接第二移位寄存器u4的qc

端,所述第一数码管u11的d2d端接第二移位寄存器u4的qd端,所述第一数码管u11的d2e端接第二移位寄存器u4的qe端,所述第一数码管u11的d2f端接第二移位寄存器u4的qf端,所述第一数码管u11的d2g端接第二移位寄存器u4的qg端,所述第一数码管u11的dp2端接第二移位寄存器u4的qh端;

52.所述第一数码管u11的d3a端接第三移位寄存器u5的qa端,所述第一数码管u11的d3b端接第三移位寄存器u5的qb端,所述第一数码管u11的d3c端接第三移位寄存器u5的qc端,所述第一数码管u11的d3d端接第三移位寄存器u5的qd端,所述第一数码管u11的d3e端接第三移位寄存器u5的qe端,所述第一数码管u11的d3f端接第三移位寄存器u5的qf端,所述第一数码管u11的d3g端接第三移位寄存器u5的qg端,所述第一数码管u11的dp3端接第三移位寄存器u5的qh端;

53.所述第一数码管u11的d4a端接第四移位寄存器u6的qa端,所述第一数码管u11的d4b端接第四移位寄存器u6的qb端,所述第一数码管u11的d4c端接第四移位寄存器u6的qc端,所述第一数码管u11的d4d端接第四移位寄存器u6的qd端,所述第一数码管u11的d4e端接第四移位寄存器u6的qe端,所述第一数码管u11的d4f端接第四移位寄存器u6的qf端,所述第一数码管u11的d4g端接第四移位寄存器u6的qg端,所述第一数码管u11的dp4端接第四移位寄存器u6的qh端。

54.所述第二数码管u12的d1a端接第五移位寄存器u7的qa端,所述第二数码管u12的d1b端接第五移位寄存器u7的qb端,所述第二数码管u12的d1c端接第五移位寄存器u7的qc端,所述第二数码管u12的d1d端接第五移位寄存器u7的qd端,所述第二数码管u12的d1e端接第五移位寄存器u7的qe端,所述第二数码管u12的d1f端接第五移位寄存器u7的qf端,所述第二数码管u12的d1g端接第五移位寄存器u7的qg端,所述第二数码管u12的dp1端接第五移位寄存器u7的qh端;

55.所述第二数码管u12的d2a端接第六移位寄存器u8的qa端,所述第二数码管u12的d2b端接第六移位寄存器u8的qb端,所述第二数码管u12的d2c端接第六移位寄存器u8的qc端,所述第二数码管u12的d2d端接第六移位寄存器u8的qd端,所述第二数码管u12的d2e端接第六移位寄存器u8的qe端,所述第二数码管u12的d2f端接第六移位寄存器u8的qf端,所述第二数码管u12的d2g端接第六移位寄存器u8的qg端,所述第二数码管u12的dp2端接第六移位寄存器u8的qh端;

56.所述第二数码管u12的d3a端接第七移位寄存器u9的qa端,所述第二数码管u12的d3b端接第七移位寄存器u9的qb端,所述第二数码管u12的d3c端接第七移位寄存器u9的qc端,所述第二数码管u12的d3d端接第七移位寄存器u9的qd端,所述第二数码管u12的d3e端接第七移位寄存器u9的qe端,所述第二数码管u12的d3f端接第七移位寄存器u9的qf端,所述第二数码管u12的d3g端接第七移位寄存器u9的qg端,所述第二数码管u12的dp3端接第七移位寄存器u9的qh端;

57.所述第二数码管u12的d4a端接第八移位寄存器u10的qa端,所述第二数码管u12的d4b端接第八移位寄存器u10的qb端,所述第二数码管u12的d4c端接第八移位寄存器u10的qc端,所述第二数码管u12的d4d端接第八移位寄存器u10的qd端,所述第二数码管u12的d4e端接第八移位寄存器u10的qe端,所述第二数码管u12的d4f端接第八移位寄存器u10的qf端,所述第二数码管u12的d4g端接第八移位寄存器u10的qg端,所述第二数码管u12的dp4端

接第八移位寄存器u10的qh端。

58.所述第一数码的dig1端、dig2端、dig3端和dig4端均与第十六电阻r16的第一端连接,所述第二数码的dig1端、dig2端、dig3端和dig4端均与第十六电阻r16的第一端连接,所述第十六电阻r16的第二端接5v电压,所述第十六电阻r16为滑动电阻。

59.在一些实施例中,所述轴角编码器测试电路还包括通讯模块,所述通信模块包括rs232模块和rs485模块中的一种或两种。

60.具体的,所述rs485收发器u13、rs232收发器u14、第十七电阻r17、第十电容c10、第十一电容c11、第十二电容c12、第十三电容c13、第十四电容c14、第十五电容c15、485接口p1和232接口p2,所述rs485收发器u13的型号为max485,所述rs232收发器u14的型号为max232。

61.如图7所示,所述rs485收发器u13的vcc端接地,所述rs485收发器u13的vcc端接5v电压,所述rs485收发器u13的a端经第十七电阻r17与其b端连接,所述rs485收发器u13的a端接485接口p1的第二端,所述rs485收发器u13的b端接485接口p1的第三端,所述rs485收发器u13的ro端接单片机u1的pa10端,所述rs485收发器u13的re端和de端接单片机u1的pa8端,所述rs485收发器u13的di端接单片机u1的pa9端,所述485接口p1的第四端接5v电压,所述485接口p1的第一端接地。

62.如图8所示,所述rs232收发器u14的vcc端经第十一电容c11接地,所述rs232收发器u14的vcc端接5v电压,所述rs232收发器u14的vdd端经第十二电容c12接地,所述rs232收发器u14的t1out端接232接口p2的第三端,所述rs232收发器u14的r1in端接232接口p2的第二端,所述232接口p2的第一端接地,所述232接口p2的第四端接5v电压,所述rs232收发器u14的vee端经第十三电容c13接地,所述rs232收发器u14的c1+端经第十四电容c14接其c1

‑

端,所述rs232收发器u14的c2+端经第十五电容c15接其c2

‑

端,所述rs232收发器u14的t1in端接单片机u1pa2端,所述rs232收发器u14的r1out端接单片机u1的pa3端,所述rs232收发器u14的gnd端接地。

63.在一些实施例中,所述轴角编码器测试电路还包括滤波放大模块,所述滤波放大模块串联在电平模块和微处理器之间,用于对所述第二电平进行滤波和放大,消除噪声信号的影响。

64.在一些实施例中,所述电源模块包括电池和保护电路,所述保护电路串接在所述电池和处理器模块之间,用于在过流或过压时断开电池与处理器模块、移位寄存器模块和电平模块之间的电连接,防止过压或过流时损坏相关元器件。

65.所述电源模块还包括电量检测电路和报警器,所述电量检测电路与所述处理器模块和电池电连接,用于检测所述电池的剩余电量,并将检测结果发送给处理器模块,所述报警器与所述处理器模块连接,所述处理器模块在所述电池的剩余电量低于阈值时控制所述报警器报警,提醒用户及时更换电池。

66.以上所述仅是本实用新型的优选实施方式,应当理解本实用新型并非局限于本文所披露的形式,不应看作是对其他实施例的排除,而可用于各种其他组合、修改和环境,并能够在本文所述构想范围内,通过上述教导或相关领域的技术或知识进行改动。而本领域人员所进行的改动和变化不脱离本实用新型的精神和范围,则都应在本实用新型所附权利要求的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1