一种用于雷达发射机的辐射功率优化电路的制作方法

1.本实用新型属于航空制导技术领域,尤其是涉及一种用于雷达发射机的辐射功率优化电路。

背景技术:

2.雷达发射机是雷达系统的一个重要组成部分,它产生满足要求的大功率射频发射信号,经馈线系统再由天线辐射出去,从而照射远处目标。雷达发射机主要由小型速调管、主控振荡器、功率优化装置及高压电源组成,具有效率高、体积小、增益高、辐射功率大、空间利用率高的优点,特别适用于弹载应用。但由于发射机工作频带窄、辐射功率不稳定,必须使用功率优化装置构成功率反馈回路,以保证小型速调管功率输出保持在最大状态。

3.目前,上述的雷达发射机,其功率优化装置采用分立元器件构成,优化程序采用门电路实现,电子元器件种类繁多、结构复杂,相对狭小的空间限制了元器件数量的使用,使得自动优化程序无法应用。在辐射信号优化过程中会产生两个问题:一、大量采用门电路,难以集成复杂的自动功率优化程序;二、集成度低,增加了功率优化装置的功耗和体积。

技术实现要素:

4.为解决上述问题,本实用新型的目的是提供一种用于雷达发射机的辐射功率优化电路,其能够保证雷达发射机的最大功率输出,还能够应用在遥控遥测、制导武器等装备的电子系统中以保证信号的最大功率输出。

5.为实现上述发明目的,本实用新型采用如下技术方案:

6.一种用于雷达发射机的辐射功率优化电路,其包括:

7.转换电路,与数字集成电路连接,用于将发射机辐射信号的耦合输出转换为指示电平输出,同时将指示电平转换为数字量,送入数字集成电路进行处理;

8.数字集成电路,与电调电路连接,数字集成电路采用复杂可编程逻辑器件cpld,用于根据发射机的工作时钟生成功率优化的控制节拍,以及根据功率指示电平的变化输出控制电调电路的数字量;

9.电调电路,用于根据数字集成电路的处理结果和数字量形成电调信号,控制发射机输入信号的功率。

10.进一步地,上述的转换电路,其由平均值电路、同相放大电路和模数转换电路组成,所述平均值电路包括双运算放大器u1的运算放大器u1a,信号输入端与电阻r1一端连接,电阻r1与串联的电阻r2、电容c1并联,电阻r3一端接在电阻r2与电容c1之间,另一端分别经电容c3、电阻r4与运算放大器u1a的反相输入端、同相输入端相连,且同相输入端通过电容c2与电阻r1另一端连接,运算放大器u1a的反相输入端与输出端相连,正、负电源端分别接正、负电源;运算放大器u1a的输出端与同相放大电路连接,同相放大电路和模数转换电路连接。

11.更进一步地,上述的同相放大电路包括双运算放大器u1的运算放大器u1b,运算放

大器u1b的同相输入端通过电阻r6与运算放大器u1a的输出端相连,反相输入端通过电阻r5接地,反相输入端通过并联的电阻r7、电容c4与输出端相连,输出端经电阻r8输出指示电平,正、负电源端分别接正、负电源。

12.更进一步地,上述的模数转换电路包括模数转换器u7,模数转换器u7的模拟量输入端与运算放大器u1b的输出端相连,时钟输入端通过总线与数字集成电路的复杂可编程逻辑器件u6的模数转换时钟控制接口连接,多个数字量输出端通过总线与复杂可编程逻辑器件u6的多个数字输入接口一一对应相连,控制信号端、模拟公共端、数字公共端均接地,正、负电源端分别接正、负电源。

13.进一步地,上述的电调电路由衰减器、低通滤波电路、电流驱动电路和稳压电路组成,衰减器包括数模转换器u2和双运算放大器u3的运算放大器u3a,数模转换器u2的多个数字量输入端通过总线与数字集成电路的复杂可编程逻辑器件u6的多个数字输出接口一一对应相连,第一输出端、第二输出端分别与双运算放大器u3的运算放大器u3a的反相输入端、同相输入端相连,且第一输出端、第二输出端之间反向并联二极管d2、二极管d3,电源端与运算放大器u3a的正电源端相连且接正电源,反馈电阻端rf与运算放大器u3a的输出端相连,基准电压端vref与稳压电路、电流驱动电路连接,写信号端wr与接地端相连并接地,负电源端接负电源, 运算放大器u3a的输出端与低通滤波电路连接。

14.更进一步地,上述的低通滤波电路包括双运算放大器u3的运算放大器u3b和双运算放大器u4的运算放大器u4a,运算放大器u3a的输出端与电阻r9一端相连,电阻r9另一端分别通过电阻r10、电容c5、电阻r11与运算放大器u3b的反相输入端、同相输入端、输出端相连,反相输入端与输出端之间接有电容c6;运算放大器u3b的输出端与电阻r12一端相连,电阻r12另一端分别通过电阻r13、电容c7、电阻r14与运算放大器u4a的反相输入端、同相输入端、输出端相连;运算放大器u4a的反相输入端与输出端之间接有电容c8,运算放大器u4a的正、负电源端分别接正、负电源。

15.更进一步地,上述的电流驱动电路包括双运算放大器u4的运算放大器u4b和双运算放大器u5的运算放大器u5a, 运算放大器u4a的输出端通过串联的电阻r15、电阻r16与运算放大器u4b的反相输入端相连,且运算放大器u4b的反相输入端与输出端之间接有电阻r19,电调电路中的衰减器的数模转换器u2的基准电压端vref通过电阻r17与运算放大器u4b的同相输入端相连,且此同相输入端通过电阻r18接地,运算放大器u4b的输出端与运算放大器u5a的同相输入端相连;运算放大器u5a的反相输入端与三极管q1的发射极相连,并通过电阻r24与数模转换器u2的基准电压端vref相连,输出端与三极管q1的基极相连,正、负电源端分别接正、负电源,三极管q1的集电极通过并联的电阻r20、电容c9接地。

16.再进一步地,上述的三极管q1为npn型三极管。

17.更进一步地,上述的稳压电路包括双运算放大器u5的运算放大器u5b、稳压二极管d1和三极管q2,运算放大器u5b的同相输入端、反相输入端分别通过稳压二极管d1、电阻r21接地,同相输入端与负电源端之间接有电阻r23,正电源端接正电源,输出端与三极管q2的基极相连,负电源端与三极管q2的集电极相连,反相输入端通过电阻r22与三极管q2的发射极相连,三极管q2的发射极与数模转换器u2的基准电压端vref相连。

18.再进一步地,上述的三极管q2为pnp型三极管。

19.由于采用如上所述的技术方案,本实用新型具有如下优越性:

20.该用于雷达发射机的辐射功率优化电路,其结构设计合理,集成度高,体积小,功耗低,制造成本低,利用转换电路将发射机辐射信号的耦合输出转换为指示电平输出,同时将指示电平转换为数字量,送入数字集成电路进行处理;数字集成电路根据发射机的工作时钟生成功率优化的控制节拍,集成发射机功率优化程序并生成控制电调电路的数字量;电调电路根据数字集成电路的处理结果和数字量形成电调衰减控制信号,控制发射机输入信号的功率,从而使发射机辐射信号功率保持在最大值,具有良好的推广应用价值。

附图说明

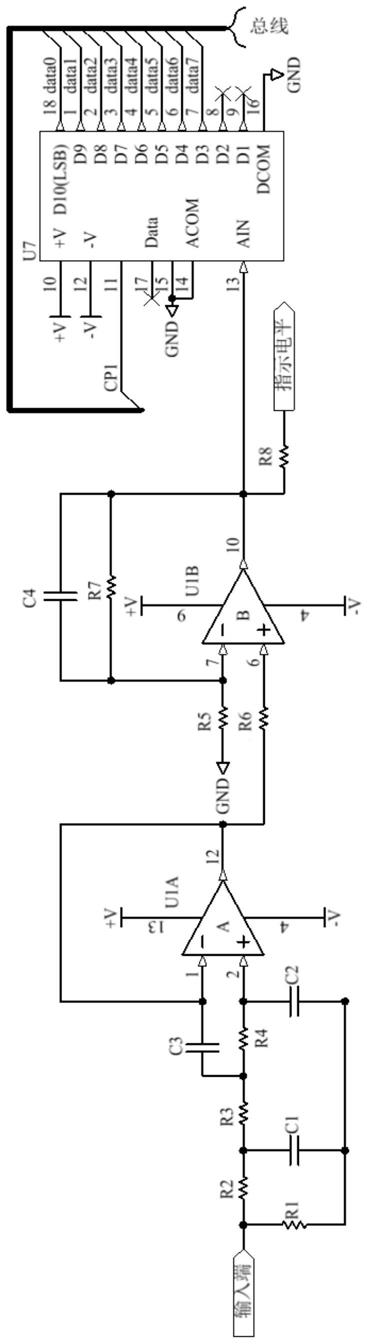

21.图1是本实用新型用于雷达发射机的辐射功率优化电路的转换电路的原理图;

22.图2是本实用新型用于雷达发射机的辐射功率优化电路的衰减器的原理图;

23.图3是本实用新型用于雷达发射机的辐射功率优化电路的低通滤波电路的原理图;

24.图4是本实用新型用于雷达发射机的辐射功率优化电路的电流驱动电路的原理图;

25.图5是本实用新型用于雷达发射机的辐射功率优化电路的稳压电路的原理图;

26.图6是本实用新型用于雷达发射机的辐射功率优化电路的数字集成电路的原理图。

具体实施方式

27.下面结合附图和实施例对本实用新型的技术方案作进一步详细说明。

28.如图1~6所示,该用于雷达发射机的辐射功率优化电路,其包括:

29.转换电路,与数字集成电路连接,用于将发射机辐射信号的耦合输出转换为指示电平输出,同时将指示电平转换为数字量,送入数字集成电路进行处理;

30.数字集成电路,与电调电路连接,数字集成电路采用复杂可编程逻辑器件cpld,用于根据发射机的工作时钟生成功率优化的控制节拍,以及根据功率指示电平的变化输出控制电调电路的数字量,该数字量经电调电路生产相应的模拟电平,以便控制发射机输入信号大小;

31.电调电路,用于根据数字集成电路的处理结果和数字量形成电调信号,控制发射机输入信号的功率;当发射机辐射功率达到最大时,数字集成电路控制电调信号跟踪辐射功率最大值。

32.上述的转换电路,其由平均值电路、同相放大电路和模数转换电路组成,辐射信号经过耦合后变为脉冲信号,经过平均值电路和同相放大电路转换为直流电平,转换系数与信号占空比、电路增益相关;将上述直流电平放大后输出功率指示电平,经过电阻隔离输出;通过调整比例电路的增益,配合输入脉冲信号的占空比,能够保证功率指示电平转换系数。同时,直流电平经过模/数转换后变为数字量,送入复杂可编程逻辑器件cpld进行信号处理。

33.上述的平均值电路包括双运算放大器u1的运算放大器u1a,信号输入端与电阻r1一端连接,进行阻抗匹配,电阻r1与串联的电阻r2、电容c1并联,电阻r3一端接在电阻r2与电容c1之间,另一端分别经电容c3、电阻r4与运算放大器u1a的反相输入端(引脚1)、同相输

入端(引脚2)相连,且同相输入端通过电容c2与电阻r1另一端连接,电阻r2与电容c1组成的低通滤波电路,电阻r4与电容c2组成低通滤波电路,运算放大器u1a的反相输入端(引脚1)与输出端(引脚12)相连构成负反馈,正电源端(引脚13)、负电源端(引脚4)分别接正电源、负电源;运算放大器u1a的输出端与同相放大电路连接,同相放大电路和模数转换电路连接。

34.上述的同相放大电路包括双运算放大器u1的运算放大器u1b,运算放大器u1b的同相输入端(引脚6)通过电阻r6与运算放大器u1a的输出端(引脚12)相连,反相输入端(引脚7)通过电阻r5接地,反相输入端通过并联的电阻r7、电容c4与输出端(引脚10)相连,输出端经电阻r8输出指示电平,正电源端(引脚9)、负电源端(引脚4)分别接正电源、负电源。同相放大电路增益由(1+r7/r5)决定,电容c4对比例电路的相频特性进行补偿,防止电路自激,保证整个电路的稳定性。通过调整比例电路的增益,配合输入脉冲信号的占空比,能够保证功率指示电平转换系数。

35.上述的模数转换电路包括模数转换器u7,模数转换器u7的模拟量输入端(引脚13)与运算放大器u1b的输出端(引脚10)相连,时钟输入端(引脚11)通过总线与数字集成电路的复杂可编程逻辑器件u6的模数转换时钟控制接口(引脚22)连接,多个数字量输出端(引脚18、引脚1~7)通过总线与复杂可编程逻辑器件u6的多个数字输入接口(引脚33~41)一一对应相连,控制信号端(引脚15)、模拟公共端(引脚14)、数字公共端(引脚16)均接地,正电源端(引脚10)、负电源端(引脚12)分别接正电源、负电源。模数转换器u7按照总线传输的时钟cp1将运算放大器u1b输出的模拟量转换为8位数字量data0~data7,从数字端口输出到总线。

36.上述的电调电路由衰减器、低通滤波电路、电流驱动电路和稳压电路组成,用于生成发射机输入功率调整的控制信号,稳压电路为衰减器提供数模转换的基准电压,衰减器采用8bit数模转换器及其外围电路构成的数字衰减器,根据总线数字量的大小对基准电压进行衰减,并经过运算放大器驱动进行输出,控制数字量以实现输出电压在一定范围内输出;低通滤波电路采用二阶无限增益低通滤波电路,保证信号幅频特性;电流驱动电路采用运算放大器和三极管组成电流驱动,满足发射机输入信号功率调整的驱动要求。

37.上述的衰减器包括数模转换器u2和双运算放大器u3的运算放大器u3a,数模转换器u2的多个数字量输入端(引脚11~4)通过总线与数字集成电路的复杂可编程逻辑器件u6的多个数字输出接口(引脚4~12)一一对应相连,第一输出端(引脚1)、第二输出端(引脚2)分别与双运算放大器u3的运算放大器u3a的反相输入端(引脚1)、同相输入端(引脚2)相连,且第一输出端、第二输出端之间反向并联二极管d2、二极管d3,电源端(引脚14)与运算放大器u3a的正电源端(引脚13)相连且接正电源,反馈电阻端rf(引脚16)与运算放大器u3a的输出端(引脚12)相连,基准电压端vref(引脚15)与稳压电路、电流驱动电路连接,写信号端wr(引脚13)与接地端(引脚3)相连并接地,负电源端(引脚4)接负电源, 运算放大器u3a的输出端(引脚12)与低通滤波电路连接。数模转换器u2将稳压电路输出的基准电压作为参考电平vref,并将自身反馈电阻rf作为运算放大器u3a的负反馈与输出端相连构成可编程衰减器,复杂可编程逻辑器件u6经总线传输的8位数字量d0~d7能够控制衰减器的衰减系数。

38.上述的低通滤波电路包括双运算放大器u3的运算放大器u3b和双运算放大器u4的运算放大器u4a,运算放大器u3a的输出端(引脚12)与电阻r9一端相连,电阻r9另一端分别

通过电阻r10、电容c5、电阻r11与运算放大器u3b的反相输入端(引脚7)、同相输入端(引脚6)、输出端(引脚10)相连,反相输入端与输出端之间接有电容c6;运算放大器u3b的输出端(引脚10)与电阻r12一端相连,电阻r12另一端分别通过电阻r13、电容c7、电阻r14与运算放大器u4a的反相输入端(引脚1)、同相输入端(引脚2)、输出端(引脚12)相连;运算放大器u4a的反相输入端与输出端之间接有电容c8,运算放大器u4a的正(引脚13、引脚9)接正电源,负电源端(引脚4)接负电源。使用运算放大器u3b和运算放大器u4a构成两级有源低通滤波器电路,第一级低通滤波器的截止频率fh1≈1.4khz、等效品质因数q1≈0.5、增益a1=1,为二阶巴特沃斯低通滤波器;第二级低通滤波器的截止频率fh2≈1.7khz、等效品质因数q2≈0.8、增益a2=1,为二阶巴特沃斯低通滤波器。

39.上述的电流驱动电路包括双运算放大器u4的运算放大器u4b和双运算放大器u5的运算放大器u5a, 运算放大器u4a的输出端(引脚12)通过串联的电阻r15、电阻r16与运算放大器u4b的反相输入端(引脚7)相连,且运算放大器u4b的反相输入端与输出端(引脚10)之间接有电阻r19,电调电路中的衰减器的数模转换器u2的基准电压端vref(引脚15)通过电阻r17与运算放大器u4b的同相输入端(引脚6)相连,且此同相输入端通过电阻r18接地,运算放大器u4b的输出端(引脚10)与运算放大器u5a的同相输入端(引脚2)相连;运算放大器u5a的反相输入端(引脚1)与三极管q1的发射极相连,并通过电阻r24与数模转换器u2的基准电压端vref(引脚15)相连,输出端(引脚12)与三极管q1的基极相连,正电源端(引脚13)接正电源,负电源端(引脚4)接负电源,三极管q1的集电极通过并联的电阻r20、电容c9接地;所述的三极管q1为npn型三极管。利用运算放大器u4b和运算放大器u5a跟随控制信号,并与稳压电路输出的基准电压vref确定电调信号电流大小,三极管q1用于电流扩展,以满足负载要求。

40.上述的稳压电路包括双运算放大器u5的运算放大器u5b、稳压二极管d1和三极管q2,运算放大器u5b的同相输入端(引脚6)、反相输入端(引脚7)分别通过稳压二极管d1、电阻r21接地,同相输入端与负电源端(引脚4)之间接有电阻r23,正电源端(引脚9)接正电源,输出端(引脚10)与三极管q2的基极相连,负电源端(引脚4)与三极管q2的集电极相连,反相输入端(引脚7)通过电阻r22与三极管q2的发射极相连,三极管q2的发射极与数模转换器u2的基准电压端vref(引脚15)相连;所述的三极管q2为pnp型三极管。稳压二极管d1与运算放大器u5b构成带反馈环节的可调有源稳压电路,通过调节电阻r22改变稳压电路输出基准电压vref。

41.上述的数字集成电路,其复杂可编程逻辑器件u6由bank a单元、bank b单元和bank d单元组成,bank a单元的8位数字io接口作为数字输出口由高到低输出数字控制量d7~d0,bank b单元的1位数字io接口作为模数转换时钟控制cp1,bank d单元的8位数字io接口作为数字输入口由高到低输入功率电平的数字量data7~data0。

42.本实用新型用于雷达发射机的辐射功率优化电路,其双运算放大器u1、双运算放大器u3、双运算放大器u4、双运算放大器u5的型号均为td747,模数转换器u7的型号为ad571、或ad838,数模转换器u2的型号为ad7524、或adm660;复杂可编程逻辑器件u6采用altera公司的epm7160sli84芯片,plcc封装,84个引脚且引脚逻辑延时不超过5ns,计数器工作频率高达178.6mhz,+5v供电。复杂可编程逻辑器件cpld内集成时序控制和功率优化程序。

43.以上所述仅为本实用新型的较佳实施例,而非对本实用新型的限制,在不脱离本实用新型的精神和范围的情况下,凡依本实用新型申请专利范围所作的均等变化与修饰,皆应属本实用新型的专利保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1