一种用于三相电流电压采样的MCU与CPLD间高速并行通信装置的制作方法

一种用于三相电流电压采样的mcu与cpld间高速并行通信装置

技术领域

1.本实用新型涉及三相电功率计量系统技术领域,具体涉及一种用于三相电流电压采样的mcu与cpld间高速并行通信装置。

背景技术:

2.在高精度三相电功率计量系统中,所有电流电压的采样时刻应保持高度一致才能获得较高精度的瞬时功率计算结果,进而为频率的提取、功率分析、功率积分等工作提供可靠的原始数据。

3.mcu一般是实现控制adc采样和原始数据的计算处理的低成本通用方案,但在三相系统中采样路数较多,一般mcu没有足够的片上资源应对多路adc的并行控制和数据传输。如果采用顺序采样又会大大影响采样时刻的一致性。

4.在需要mcu与cpld进行数据传输的应用场合中,多使用mcu自带spi总线接口或用通用io口模拟串行和并行数据总线与cpld进行通信。mcu自带spi总线接口使用较为方便但接口数据带宽上限往往较低,且spi总线无应答环节。io口模拟串行和并行数据总线可灵活定义总线功能,但需要占用mcu计算资源不适合大规模的持续的数据吞吐,同时数据带宽上限受处理速度影响往往比spi总线还要低。

技术实现要素:

5.针对现有技术的不足,本实用新型提供一种用于三相电流电压采样的mcu与cpld间高速并行通信装置,解决高精度三相电功率计量系统中mcu控制adc进行多路数据并行采样资源不足问题和传输带宽的瓶颈问题。

6.本实用新型是通过如下技术方案实现的:

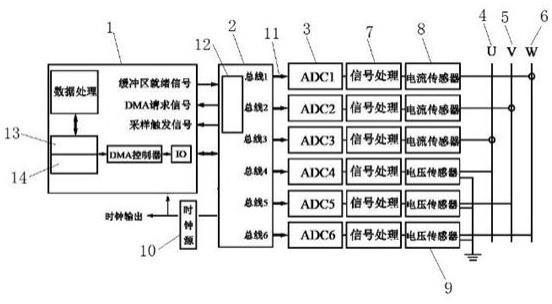

7.提供一种用于三相电流电压采样的mcu与cpld间高速并行通信装置,包括mcu、cpld和分别用于收集三相电u线、v线和w线的电流、电压采样信号的三组adc,cpld通过并行总线分别与三组adc通讯连接,cpld还连接有时钟源,

8.mcu设有数据fifoi和数据fifoii,cpld设有数据fifoiii,

9.mcu通过dma触发信号接收引脚与cpld的dma触发信号发送引脚通讯连接用于接收cpld的dma请求信号,mcu通过缓冲区信号发送引脚与cpld的缓冲区信号接收引脚通讯连接用于接收cpld的缓冲区就绪信号,mcu通过采样触发信号接收引脚与cpld的采样触发信号发送引脚通讯连接用于接收cpld完成一次采样后的采样触发信号,mcu通过内存地址上成组映射的支持dma传输的io端口将mcu的数据fifoi和数据fifoii与cpld的数据fifoiii通讯连接。

10.进一步的,三组adc中第一组用于收集三相电u线电压和电流信号,三组adc中第二组用于收集三相电v线电压和电流信号,三组adc中的第三组用于收集三相电w线电压和电流信号,每组adc均包括两路adc,一路adc通过信号处理电路与电流传感器电连接,另一路

adc通过信号处理电路与电压传感器电连接。

11.进一步的,信号处理电路包括依次电连接的电流电压转换电路、反相加法器、二阶低通滤波器和缓冲跟随器。

12.本实用新型的有益效果:

13.本实用新型通过用cpld做adc采样控制和mcu的通信缓冲芯片。通过设置cpld芯片扩展了mcu控制adc的能力,并巧妙地利用mcu中io端口可映射到内存地址的特性实现了mcu与cpld间高速数据传输。

附图说明

14.图1为本实用新型的结构示意图。

15.图2为本实用新型中信号处理电路的结构示意图。

16.图3为本实用新型中dma双缓冲的工作示意图。

17.图4为本实用新型的时序图。

18.图5为本实用新型的流程框图。

19.图中所示:

20.1、mcu,2、cpld,3、adc,4、u线,5、v线,6、w线,7、信号处理电路,8、电流传感器,9、电压传感器,10、时钟源,11、并行总线,12、数据fifoiii,13、数据fifoi,14、数据fifoii,15、电流电压转换电路,16、反相加法器,17、二阶低通滤波器,18、缓冲跟随器。

具体实施方式

21.为能清楚说明本方案的技术特点,下面通过具体实施方式,对本方案进行阐述。

22.一种用于三相电流电压采样的mcu与cpld间高速并行通信装置,包括mcu1、cpld2和分别用于收集三相电u线4、v线5和w线6的电流、电压采样信号的三组adc,cpld2通过并行总线11分别与三组adc通讯连接,cpld2还连接有时钟源10。

23.其中:三组adc中第一组用于收集三相电u线4电压和电流信号,三组adc中第二组用于收集三相电v5线电压和电流信号,三组adc中的第三组用于收集三相电w6线电压和电流信号,每组adc均包括两路adc,一路adc3通过信号处理电路7与电流传感器8电连接,另一路adc3通过信号处理电路7与电压传感器9电连接。信号处理电路7包括依次电连接的电流电压转换电路15、反相加法器16、二阶低通滤波器17和缓冲跟随器18。其作用为将传感器模拟信号电压调整到adc输入电压范围内并进行低通滤波。

24.六路采样电路同时由cpld2控制,在高精度低相位噪声时钟源10驱动下同时触发进行模拟信号的采样。时钟源10接入mcu1可为其提供运行时钟,同时对外部输出以进行频率信号溯源以及不确定度分析。

25.mcu1设有数据fifoi13和数据fifoii14,如图1所示,还设有数据处理模块、dma控制器等,cpld2设有数据fifoiii12。mcu1通过dma触发信号接收引脚与cpld2的dma触发信号发送引脚通讯连接用于接收cpld2的dma请求信号,mcu1通过缓冲区信号发送引脚与cpld2的缓冲区信号接收引脚通讯连接用于接收cpld2的缓冲区就绪信号,mcu1通过采样触发信号接收引脚与cpld2的采样触发信号发送引脚通讯连接用于接收cpld2完成一次采样后的采样触发信号,为计算程序提供周期节拍。mcu1通过内存地址上成组映射的支持dma传输的

io端口将mcu1的数据fifoi13和数据fifoii14与cpld2的数据fifoiii12通讯连接。cpld2接收到adc3的转换数据后,按自定义格式将数据暂存入fifo队列中供mcu1读取。

26.本实用新型的硬件配置:

27.cpld2通过verilog编程配置时序逻辑和io操作模式。主要模块为:

28.1、adc控制和数据读取时序逻辑,负责操作adc进行电压采样和读取转换数据。

29.2、adc数据格式组合缓存,负责按自定义格式将adc数据暂存入fifo队列中供mcu1读取。

30.3、与mcu1通信接口,负责响应mcu1的数据请求,向并行io总线上发送adc转换数据。cpld2需根据mcu1的dma最大传输速度产生适当频率的时钟信号作为dma请求信号,同时将数据发送到并行io总线供mcu读取。

31.mcu1通过c语言编程实现内部模块的配置,以及与cpld2间的高速通信和数据处理输出等功能。主要功能部分为:

32.1、配置dma控制器实现高速通信。mcu1程序建立一个数据fifo缓冲区,将dma源设置为io口地址,目标设置为fifo指针地址,工作模式设为双缓冲模式。mcu1的dma模块需要选择一个外部触发事件,通常可选取定时器模块的外部输入接口实现。

33.2、fifo缓冲区,开辟两段连续地址的fifo数据结构作为dma双缓冲接收区。在dma完成中断中切换目标地址。

34.3、数据处理,输出。完成波形分析,功率分析等业务功能。

35.本实用新型的工作流程:

36.一次完整的采样工作时序如图4所示。

37.cpld2控制六路adc同时进行采样,并读取数据暂存入fifo队列中供mcu1读取。mcu1发出缓冲区就绪信号后,cpld2开始发送dma请求信号。mcu1接收到dma请求信号后,dma模块开始按预定数据宽度从cpld2预设为数据总线的io口上读取adc数据。数据存入fifoi13或fifoii14中,mcu1从同时在未被占用的fifo中读取数据并进行处理。

38.mcu1的dma传输延时是整个传输过程中耗时最长阶段,也是决定最高传输速率的关键因素。最后cpld2必须在dma传输结束后才能读取数据,否则数据将出现错误,此延时是可通过芯片手册数据估算的。

39.本方案同样适用于mcu与 fpga,mcu与 mcu间的通信。

40.当然,上述说明也并不仅限于上述举例,本实用新型未经描述的技术特征可以通过或采用现有技术实现,在此不再赘述;以上实施例及附图仅用于说明本实用新型的技术方案并非是对本实用新型的限制,参照优选的实施方式对本实用新型进行了详细说明,本领域的普通技术人员应当理解,本技术领域的普通技术人员在本实用新型的实质范围内所做出的变化、改型、添加或替换都不脱离本实用新型的宗旨,也应属于本实用新型的权利要求保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1