TEM样品的制备方法与流程

本发明涉及一种半导体集成电路制造方法,特别涉及一种透射电子显微镜(tem)样品的制备方法。

背景技术:

1、在集成电路生产过程中,tem是不可或缺的研究、分析工具之一。当制程逐步向纳米级发展时,器件尺寸也越来越小,tem高解析度、高精度的优点,使其在失效分析等方面的应用越来越广泛。而聚焦离子束(focused ion beam,fib)精确定位制备tem样品则是半导体领域最为主要的制备手段之一。

2、fib制备tem样品是在芯片的芯片样品的基础上进行制备,使用fib制备芯片的tem样品时,遇到芯片样品厚度差异或者材质差异的情况,特别是芯片样品上有孔洞的情况下,会产生离子束拉痕,又叫窗帘(curtain)效应。这些离子束拉痕会影响tem成像质量,严重时甚至在制备超薄tem样品时会引起tem样品损伤而无法分析。

3、当芯片样品中具有深沟槽结构时,按照现有方法制样容易产生离子束拉痕。特别是当目标结构材质较为脆弱,易受到电子束或热应力影响时,制样则变得更加困难。

4、现有tem样品的制备方法包括如下步骤:

5、步骤一、如图1a所示,提供具有深沟槽102的芯片样品101。

6、通常,所述芯片样品101包括半导体衬底、形成于半导体衬底正面的半导体器件层;所述深沟槽102位于所述半导体器件层。

7、所述半导体衬底包括硅衬底。

8、所述芯片样品101的厚度为500nm以上。所述芯片样品101通过对所述半导体衬底组成的晶圆进行切割和减薄工艺得到。

9、所述芯片样品101中包括多个所述深沟槽102,各所述深沟槽102平行排列。

10、图1a中,所述深沟槽102的长度方向为y方向,所述深沟槽102的宽度方向为x方向,所述深沟槽102沿x方向间隔排列。虚线框103为形成tem样品的目标区域,也即需要分析的区域位于虚线框103中。

11、图1b为图1a对应的剖面图,剖面为xz平面。

12、如图2a所示,形成保护层104,即从顶部填充所述保护层104。如图2b所示,所述保护层104从而所述芯片样品101的顶部对所述深沟槽102进行填充,所述保护层104还延伸到所述深沟槽102外的所述芯片样品101的顶部表面。

13、第一值为所述保护层104能完全填充沟槽的最大深宽比,所述深沟槽102的深宽比大于第一值,所述保护层104对所述深沟槽102为不完全填充并在所述深沟槽102内形成有由不完全填充而产生的孔隙105。

14、步骤二、如图3a所示,使用fib对所述芯片样品101中用于形成tem样品的目标区域进行前后面切割并形成具有目标厚度的所述tem样品106。

15、所述tem样品106的前侧面1061和后侧面1062都和所述深沟槽102的延伸方向相交如图3a所示的垂直相交,这样,如图3b所示,所述深沟槽102中的孔隙105会在所述tem样品106的前侧面1061和后侧面1062暴露出来。在所述前后面切割过程中,会在所述孔隙105底部产生窗帘效应,从而会形成离子束拉痕107。

16、如图4所示,是采用现有tem样品的制备方法制备的tem样品的照片;图4对应于图3b中所述tem样品106的照片,可以看出,保护层104a填充深沟槽后会形成孔隙105a,在孔隙105a的底部会形成离子束拉痕107a。

技术实现思路

1、本发明所要解决的技术问题是提供一种tem样品的制备方法,能在对具有深沟槽的芯片样品进行制样过程中减少或消除离子束拉痕,从而能消除tem样品中的由离子束拉痕造成损伤,被曝光提高tem样品的质量和制样成功率。

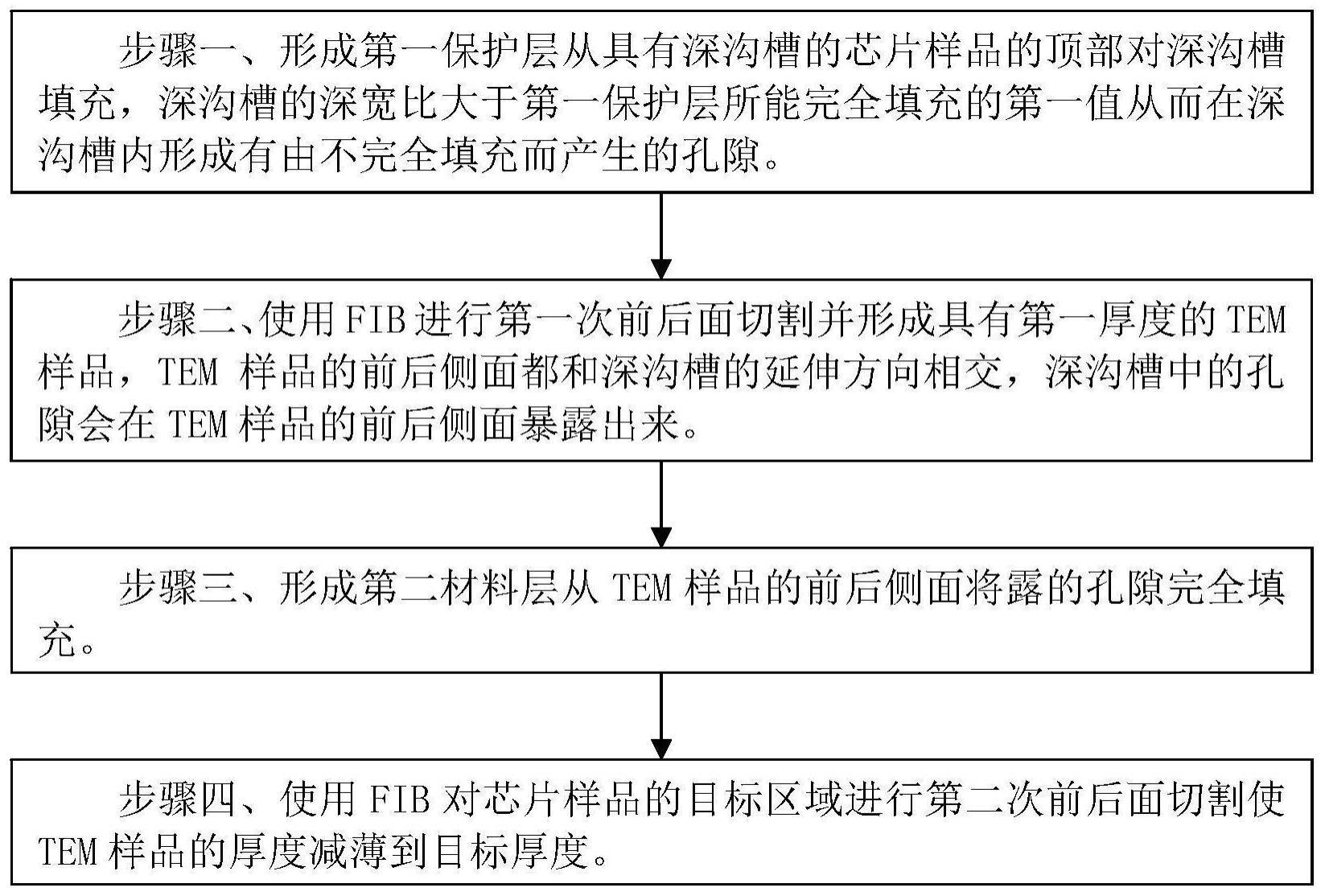

2、为解决上述技术问题,本发明提供的tem样品的制备方法包括如下步骤:

3、步骤一、提供具有深沟槽的芯片样品;形成第一保护层,所述第一保护层从而所述芯片样品的顶部对所述深沟槽进行填充,所述第一保护层还延伸到所述深沟槽外的所述芯片样品的顶部表面;

4、第一值为所述第一保护层能完全填充沟槽的最大深宽比,所述深沟槽的深宽比大于第一值,所述第一保护层对所述深沟槽为不完全填充并在所述深沟槽内形成有由不完全填充而产生的孔隙;

5、步骤二、使用fib对所述芯片样品中用于形成tem样品的目标区域进行第一次前后面切割并形成具有第一厚度的所述tem样品,所述第一厚度大于目标厚度;所述tem样品的前侧面和后侧面都和所述深沟槽的延伸方向相交,所述深沟槽中的孔隙会在所述tem样品的前侧面和后侧面暴露出来;

6、步骤三、形成第二材料层,所述第二材料层从所述tem样品的前侧面和后侧面将露的孔隙完全填充;

7、步骤四、使用fib对应所述芯片样品的目标区域进行第二次前后面切割使所述tem样品的厚度减薄到目标厚度。

8、进一步的改进是,所述芯片样品包括半导体衬底、形成于半导体衬底正面的半导体器件层;所述深沟槽位于所述半导体器件层。

9、进一步的改进是,所述芯片样品中包括多个所述深沟槽,各所述深沟槽平行排列。

10、进一步的改进是,所述半导体器件层中,具有所述深沟槽的结构包括:

11、深沟槽隔离;

12、多晶硅线的排列结构;

13、鳍体的排列结构;

14、金属线的排列结构。

15、进一步的改进是,步骤一中,采用电子束辅助沉积工艺或者胶体涂覆工艺形成所述第一保护层。

16、进一步的改进是,步骤二中,所述tem样品的前侧面和后侧面都和所述深沟槽的延伸方向垂直相交。

17、进一步的改进是,步骤二中,所述第一次前后面切割的切割方向为从所述芯片样品的顶部表面指向底部表面的方向。

18、进一步的改进是,所述第一厚度为100nm~300nm。

19、进一步的改进是,所述目标厚度为30nm~80nm。

20、进一步的改进是,步骤三中,采用电子束辅助沉积工艺形成所述第二材料层。

21、进一步的改进是,所述半导体衬底包括硅衬底。

22、进一步的改进是,所述第一保护层的材料包括金属材料。

23、进一步的改进是,所述第二材料层的材料包括金属材料。

24、进一步的改进是,步骤一中,所述芯片样品的厚度为500nm以上。

25、进一步的改进是,所述芯片样品通过对所述半导体衬底组成的晶圆进行切割和减薄工艺得到。

26、本发明中,对于具有深沟槽的芯片样品,在采用第一保护层对芯片样品进行顶部填充之后,将tem样品的前后面切割进行了拆分,在将tem样品减薄到目标厚度之前,利用tem样品的前侧面和后侧面将深沟槽中填充第一保护层后形成的孔隙被暴露出来的特点,增加了对tem样品进行侧面填充的步骤并利用侧面填充实现对tem样品的深沟槽内的孔隙完全填充,之后再继续进行tem样品的前后面切割即第二次前后面切割,由于进行第二次前后面切割之前,tem样品区域的深沟槽被第一保护层和第二材料层完全填充,故在第二次前后面切割过程中不会离子束拉痕,所以,本发明能在对具有深沟槽的芯片样品进行制样过程中减少或消除离子束拉痕,从而能消除tem样品中的由离子束拉痕造成损伤,被曝光提高tem样品的质量和制样成功率。

27、另外,本发明的第二材料层能采用电子束辅助沉积工艺实现,而第一次前后面切割和第二次前后面切割都是使用fib切割,电子束辅助沉积和fib切割都能在同一fib系统实现,故本发明还具有简单易操作,工艺成本低的特点。

- 还没有人留言评论。精彩留言会获得点赞!