定量评估nmos晶体管焊料层孔隙安全分布区域的方法

技术领域

1.本发明涉及电子工程学领域的检测技术,具体涉及一种定量评估nmos晶体管焊料层孔隙安全分布区域的方法。

背景技术:2.在航天用塑封nmos晶体管的制备过程中,可通过焊料将nmos芯片连接在金属基板上,以实现对nmos芯片的固定和电路导通。nmos芯片的粘结质量主要由焊料层内部存在的孔隙尺寸、孔隙比例和孔隙分布等因素决定。在老化和服役过程中,nmos晶体管处于大电流状态下,焊料层孔隙的存在会显著增大焊料层的热阻,降低器件内部散热路径的导热性,造成芯片温度因散热不佳而显著上升。然而,并不是任何位置的孔隙都会显著增大焊料层的热阻,降低器件散热路径的导热性。因此,需进一步确定焊料层孔隙的安全分布范围,剔除含有显著影响散热性能孔隙的器件,保留含有不显著影响散热性能孔隙的器件,减少nmos晶体管不必要的批退、返厂和报废,提升nmos晶体管的利用率。

3.目前主要通过x射线法、超声波扫描显微镜法和热阻测试法来检测塑封nmos晶体管焊料层的孔隙。其中,x射线法和超声波扫描显微镜法都只能检测nmos晶体管焊料层是否存在孔隙,无法评估焊料层孔隙对器件散热性能的影响程度。传统的热阻测试方法也可检测器件焊料层内部是否存在孔隙,如专利《一种大功率led器件固晶层散热性能的快速评估方法》(申请号201510078344.9)公开了一种检测器件固晶层是否存在缺陷的方法,该方法提取了表征固晶层的特征参数,有效识别了固晶层中存在的孔隙缺陷。但是该专利也只能定性判断固晶层中是否存在缺陷,难以评估不同位置的孔隙对器件散热性能的影响程度,无法确定孔隙的安全分布范围。只有定量确定不同位置的孔隙对器件散热性能的影响程度,才能判定特定位置的孔隙是否会显著影响器件的整体散热性能,从而有效保留不显著增加器件热阻的孔隙,降低器件返厂率和报废率。

技术实现要素:4.本发明的目的在于提供一种定量评估nmos晶体管焊料层孔隙安全分布区域的方法,解决现有技术无法评估焊料层不同位置孔隙对器件散热性能影响程度的问题。

5.为了达到上述的目的,本发明提供一种定量评估nmos晶体管焊料层孔隙安全分布区域的方法,包括:制备一系列焊料层孔隙率相同、孔隙分布位置不同的标定样品;通过超声波扫描显微镜验证各标定样品焊料层孔隙分布情况;采用瞬态热阻法获得孔隙位置与热阻参数的关系;根据孔隙位置与热阻参数的关系,确定焊料层孔隙的安全分布范围。

6.上述定量评估nmos晶体管焊料层孔隙安全分布区域的方法,其中,所述采用瞬态热阻法获得孔隙位置与热阻参数的关系包括:采用瞬态热阻法测定标定样品k系数;在瞬态热阻测试中监测标定样品pn结电压降,通过数学变换得到标定样品的积分函数曲线,提取热阻参数;叠加各标定样品的积分函数曲线,确定特定焊料层孔隙率标定样品的焊料热阻和总热阻,获得焊料层孔隙位置与热阻参数的关系。

7.上述定量评估nmos晶体管焊料层孔隙安全分布区域的方法,其中,所述制备一系列焊料层孔隙率相同、孔隙分布位置不同的标定样品包括:采用设有特定图案的掩膜板在nmos晶体管的金属基板表面的芯片焊盘区域内蒸镀al2o3陶瓷薄膜,构成焊料层孔隙;通过设计掩膜板图案,设计al2o3陶瓷薄膜的面积以及al2o3陶瓷薄膜与芯片焊盘区域中心点的间距;各掩膜板的图案设计,al2o3陶瓷薄膜的面积占芯片焊盘区域面积的比例相同,al2o3陶瓷薄膜与芯片焊盘区域中心点的间距不同,以得到一系列焊料层孔隙率相同、孔隙分布位置不同的标定样品。

8.上述定量评估nmos晶体管焊料层孔隙安全分布区域的方法,其中,所述在瞬态热阻测试中监测标定样品pn结电压降中,在标定样品的金属基板底部涂覆导热硅脂后,将标定样品固定在cu块冷板上,cu块冷板的温度保持恒定。

9.上述定量评估nmos晶体管焊料层孔隙安全分布区域的方法,其中,对每个标定样品,该标定样品的积分函数曲线中,横坐标为热阻值,纵坐标为热容值,原点到第一拐点所对应的横坐标热阻值代表nmos芯片pn结热阻xi,第一拐点到第二拐点所对应的横坐标热阻值代表焊料热阻hi,第二拐点到积分函数曲线最右端对应的横坐标热阻值代表金属基板、导热硅脂和cu块冷板热阻之和mi;原点到积分函数曲线最右端对应的横坐标热阻值代表标定样品的总热阻zi,i=1,2,

┄

,n,n为标定样品数量;所述孔隙位置与热阻参数的关系为:各标定样品的nmos芯片pn结热阻相等;各标定样品的焊料热阻不同,随着焊料层孔隙与芯片焊盘区域中心点间距增大,焊料热阻减小;各标定样品的金属基板、导热硅脂和cu块冷板热阻之和相等;各标定样品的总热阻不同,随着焊料层孔隙与芯片焊盘区域中心点间距增大,总热阻减小;对于任意两个标定样品,总热阻之差等于对应的焊料热阻之差。

10.上述定量评估nmos晶体管焊料层孔隙安全分布区域的方法,其中,所述根据孔隙位置与热阻参数的关系,确定焊料层孔隙的安全分布范围包括:设nmos晶体管热阻标准判据中最大焊料热阻为h,最大总热阻为z;设第i个标定样品焊料层孔隙与芯片焊盘区域中心点的间距为ri,焊料热阻为hi,总热阻zi,i=1,2,

┄

,n,n为标定样品数量,且r1<r2<

┄

<rn;将各标定样品的焊料热阻hi和总热阻zi分别与h和z比对,若满足条件h≥h1,z≥z1,则焊料层孔隙与芯片焊盘区域中心点的间距≥r1的区域为焊料层孔隙的安全分布范围;若满足条件h

i-1

≥h≥hi,z

i-1

≥z≥zi,i≠1,则焊料层孔隙与芯片焊盘区域中心点的间距≥ri的区域为焊料层孔隙的安全分布范围;若满足条件hn≥h,zn≥z,则芯片焊盘区域任何位置都不能存在焊料层孔隙。

11.与现有技术相比,本发明的有益效果包括:

12.1、本发明根据已知焊料层孔隙位置标定样品的积分函数曲线和热阻值,可定量判定不同位置焊料层孔隙对器件散热性能的影响程度,从而确定该类型器件焊料层的孔隙安全分布区域,解决了传统方法难以评估不同位置焊料层孔隙对器件散热性能影响程度的不足;本发明定量确定焊料层孔隙的安全分布区域,剔除含有显著影响散热性能孔隙的器件,保留含有不显著影响散热性能孔隙的器件,减少nmos晶体管不必要的批退、返厂和报废,提升nmos晶体管的利用率;

13.2、本发明不仅在器件焊料层设计制备了不同位置的焊料层孔隙,确定了孔隙位置和热阻参数的关系,还通过超声波扫描显微镜反向验证器件焊料层孔隙率和孔隙分布位置,保证了不同标定样品焊料层孔隙率的一致性,同时避免了相同标定样品设计孔隙位置

与实际孔隙位置的差异性;

14.3、通过调节掩膜板的图案,不仅可改变焊料层的孔隙分布位置,还可改变焊料层的孔隙率,在保证nmos芯片有足够的机械和电学稳定性前提下,焊料层孔隙率可在1-20%范围内变化,针对不同焊料层孔隙率的标定样品,本发明可依次确定对应的焊料层孔隙安全分布区域;

15.4、本发明只需测定已知焊料层孔隙位置标定样品的瞬态热阻参数,便可确定器件的焊料层孔隙安全分布范围,而在该类型器件的实际生产过程中,无需再次测试生产器件的瞬态热阻参数,只需对生产器件进行超声波扫描显微镜检测以确定焊料孔隙位置,再结合焊料层孔隙安全分布范围,即可确定生产器件的散热性能是否满足筛选要求。

附图说明

16.本发明的定量评估nmos晶体管焊料层孔隙安全分布区域的方法由以下的实施例及附图给出。

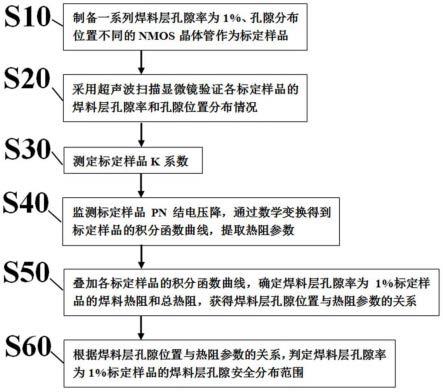

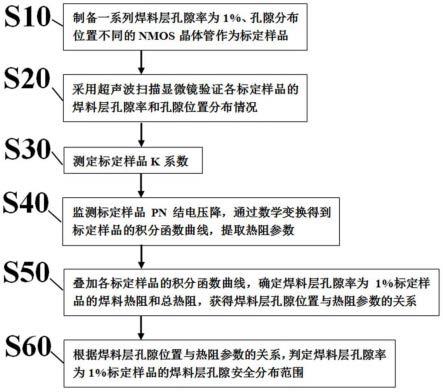

17.图1为本发明较佳实施例的定量评估nmos晶体管焊料层孔隙安全分布区域的方法的流程示意图。

18.图2为本发明较佳实施例中在覆盖掩膜板的金属基板表面蒸镀al2o3陶瓷薄膜的示意图。

19.图3为本发明较佳实施例中金属基板表面芯片焊盘区域涂覆焊料的示意图。

20.图4为本发明较佳实施例中nmos芯片焊接至金属基板表面芯片焊盘区域的示意图。

21.图5为本发明较佳实施例中键合连接nmos芯片与金属基板表面引脚焊盘的示意图。

22.图6为本发明较佳实施例中标定样品注塑成型封帽的示意图。

23.图7为本发明较佳实施例中焊料层孔隙与芯片焊盘区域中心点间距分别为r1、r2、r3和r4的焊料层孔隙分布图。

24.图8为本发明较佳实施例中超声波扫描显微镜检测焊料层孔隙分布位置的截面图。

25.图9为本发明较佳实施例中nmos晶体管瞬态热阻测试电路图。

26.图10为本发明较佳实施例中瞬态热阻测试过程中nmos晶体管一维散热路径截面图。

27.图11为本发明较佳实施例中焊料层孔隙与芯片焊盘区域中心点间距为r1的标定样品所对应的积分函数曲线图。

28.图12为本发明较佳实施例中焊料层孔隙与芯片焊盘区域中心点间距分别为r1、r2、r3和r4的标定样品所对应的积分函数曲线叠加图。

29.图13为本发明较佳实施例中焊料层孔隙率为1%标定样品的焊料层孔隙安全分布区域图。

具体实施方式

30.以下将结合图1~图13对本发明的定量评估nmos晶体管焊料层孔隙安全分布区域

的方法作进一步的详细描述。

31.本发明解决了现有技术无法评估焊料层不同位置孔隙对器件散热性能影响程度的难题。本发明的定量评估nmos晶体管焊料层孔隙安全分布区域的方法包括:制备一系列焊料层孔隙率相同、孔隙分布位置不同的标定样品;通过超声波扫描显微镜验证各标定样品焊料层孔隙分布情况;采用瞬态热阻法获得孔隙位置与热阻参数的关系;根据孔隙位置与热阻参数的关系,确定焊料层孔隙的安全分布范围。

32.下面结合附图和具体实施方式对本发明做进一步详细的描述。

33.图1为本发明较佳实施例的定量评估nmos晶体管焊料层孔隙安全分布区域的方法的流程示意图。

34.参见图1,本发明实施例的定量评估nmos晶体管焊料层孔隙安全分布区域的方法包括如下步骤:

35.s10,制备一系列焊料层孔隙率为1%、孔隙分布位置不同的nmos晶体管作为标定样品;

36.s11,如图2,金属基板111表面的芯片焊盘区域112用于焊接nmos芯片,采用设有特定图案的掩膜板113覆盖金属基板111,除芯片焊盘区域112内有一圆孔区域114未被掩膜板113覆盖外,金属基板111其余区域均被掩膜板113覆盖;在覆盖掩膜板113的芯片焊盘区域112蒸镀厚度为100um的al2o3陶瓷,在未覆盖掩膜板的圆孔区域114形成al2o3陶瓷薄膜115,如图3所示,设al2o3陶瓷薄膜115面积为芯片焊盘区域112面积的1%,al2o3陶瓷薄膜115与芯片焊盘区域112中心点116的间距为r1;

37.s12,如图3,去除掩膜板113,在芯片焊盘区域112内未蒸镀al2o3陶瓷薄膜115的区域涂覆锡铅焊料,作为焊料涂覆区域117;

38.s13,如图4,将nmos芯片118放置在芯片焊盘区域112上,nmos芯片118背面与al2o3陶瓷薄膜115和焊料涂覆区域117接触,将金属基板111放置在加热管119上进行回流焊,使焊料熔化并连接nmos芯片118与芯片焊盘区域112,由于熔化的锡铅焊料不润湿al2o3陶瓷薄膜115,al2o3陶瓷薄膜115则构成特定尺寸的焊料层孔隙120,回流焊结束后自然冷却至室温;

39.s14,如图5,将nmos芯片118与金属基板111表面的引脚焊盘121进行键合连接;如图6,进行注塑成型,形成塑封管壳122,得到焊料层孔隙率为1%,焊料层孔隙120与芯片焊盘区域中心点116间距为r1的标定样品;

40.通过设计不同图案的掩膜板,得到焊料层孔隙率均为1%,焊料层孔隙120与芯片焊盘区域中心点116间距分别为r1、r2、r3和r4的标定样品,如图7所示,本实施例中,设r1<r2<r3<r4;

41.s20,采用超声波扫描显微镜验证各标定样品的焊料层孔隙率和孔隙位置分布情况;

42.如图8所示,采用超声波扫描显微镜123对各标定样品分别进行扫描,超声波依次通过塑封管壳122、nmos芯片118、焊料层孔隙120、焊料涂覆区域117和金属基板111,获得焊料层实际孔隙面积p、芯片焊盘区域面积q和焊料层孔隙120分布位置,计算焊料层实际孔隙率t(t=p/q),若焊料层实际孔隙率、焊料层孔隙120分布位置与试验设计一致,表明焊料层孔隙分布设计方法和制备工艺合理;

43.s30,测定标定样品k系数;

44.s31,按照图9所示的nmos晶体管瞬态热阻测试电路图对标定样品进行电路连接;由于标定样品131(即nmos晶体管)的源极s和漏极d间存在寄生二极管,所以可采用源极-漏极电压降作为温度敏感参数;由于im测试电流133和ih加热电流134实际方向相反,因此在电路中串联三个二极管作为隔离二极管135,使ih加热电流134显示为正值(+),而im测试电流133显示为负值(-);由于标定样品131源极-漏极电压降与t3ster设备的vf电压传感器132方向相反,因此vf电压传感器132显示为负值(-);采用t3ster设备对标定样品131只加载5ma的im测试电流133,不加载ih加热电流134,利用vf电压传感器132实时监测标定样品131的pn结电压降变化;

45.s32,将标定样品131放置在恒温油槽中,恒温油槽温度等于标定样品pn结温度,调节恒温油槽温度使标定样品131的pn结温度从20℃逐步升高至160℃,升温速率为5℃/分钟,温度监测点的间隔设置为5℃,在每个温度监测点待标定样品131结温稳定后测试对应的pn结电压降,测试结束后,绘制该标定样品pn结电压降-结温曲线,即k系数曲线;

46.对各标定样品分别执行步骤s31和步骤s32,即可获得各标定样品的k系数曲线;

47.s40,监测标定样品pn结电压降,通过数学变换得到标定样品的积分函数曲线,提取热阻参数;

48.s41,如图10所示,在标定样品的金属基板111底部涂覆导热硅脂129后,将标定样品131固定在cu块冷板130上,cu块冷板130的温度保持在20℃;在瞬态热阻测试过程中,该标定样品131(nmos晶体管)满足一维散热路径,nmos芯片118产生的热量主要通过焊料涂覆区域117-金属基板111-导热硅脂129-cu块冷板130的散热途径向外传导;

49.s42,采用t3ster设备对标定样品131加载10a的ih加热电流134,待标定样品131的结温达到热稳态后,将ih加热电流134迅速切换至5ma的im测试电流133,采用t3ster设备的vf电压传感器132监测标定样品131的pn结电压降曲线,直至标定样品131的pn结电压降达到稳定值;

50.s43,利用步骤s30获取的标定样品的k系数,将pn结电压降曲线转化为瞬态降温曲线;

51.s44,通过数学变换将瞬态降温曲线转换为积分函数曲线;

52.对各标定样品分别执行步骤s41~步骤s44,得到各标定样品的积分函数曲线,设焊料层孔隙与芯片焊盘区域中心点间距为r1、r2、r3和r4的标定样品所对应的积分函数曲线分别为j1、j2、j3和j4;

53.图11为焊料层孔隙与芯片焊盘区域中心点间距为r1的标定样品所对应的积分函数曲线j1;

54.如图11所示,积分函数曲线j1中,横坐标为热阻值,纵坐标为热容值,原点到第一拐点所对应的横坐标热阻值代表nmos芯片pn结热阻x1,第一拐点到第二拐点所对应的横坐标热阻值代表焊料热阻h1,第二拐点到积分函数曲线最右端对应的横坐标热阻值代表金属基板、导热硅脂和cu块冷板热阻之和m1;原点到积分函数曲线最右端对应的横坐标热阻值代表标定样品的总热阻z1(z1=x1+h1+m1);

55.设焊料层孔隙与芯片焊盘区域中心点间距为r2、r3和r4的标定样品,pn结热阻分别为x2、x3和x4;焊料热阻分别为h2、h3和h4;金属基板、导热硅脂和cu块冷板热阻之和分别

为m2、m3和m4;总热阻分别为z2、z3和z4;

56.s50,叠加各标定样品的积分函数曲线,确定焊料层孔隙率为1%标定样品的焊料热阻和总热阻,获得焊料层孔隙位置与热阻参数的关系;

57.图12所示为焊料层孔隙与芯片焊盘区域中心点间距分别为r1、r2、r3和r4的标定样品所对应的积分函数曲线叠加图;

58.如图12所示,叠加后的积分函数曲线中,焊料层孔隙位置不同的标定样品对应的nmos芯片pn结热阻值是相同的(即x1=x2=x3=x4),从原点到第一拐点的积分函数曲线段也是相互重叠的;

59.如图12所示,焊料层孔隙位置不同的标定样品对应的焊料热阻是不同的,随着焊料层孔隙与芯片焊盘区域中心点间距从r1、r2、r3依次增加至r4,焊料热阻依次从h1、h2、h3减小至h4,第一拐点到第二拐点的积分函数曲线段向左侧偏移,偏移量与焊料层孔隙与芯片焊盘区域中心点间距相关,间距越大,向左偏移量越大;

60.如图12所示,焊料层孔隙位置不同的标定样品对应的金属基板、导热硅脂和cu块冷板热阻之和是相同的(即m1=m2=m3=m4),尽管对应的积分函数曲线段没有相互重叠,但是基本趋势是一致的;

61.如图12所示,随着焊料层孔隙与芯片焊盘区域中心点间距从r1、r2、r3依次增加至r4,原点到积分函数曲线最右端的标定样品总热阻依次从z1、z2、z3减小至z4,对于任意两个标定样品,总热阻之差等于对应的焊料热阻之差(即z4-z1=h4-h1;z3-z1=h3-h1;z2-z1=h2-h1);

62.步骤s60,根据焊料层孔隙位置与热阻参数的关系,判定焊料层孔隙率为1%标定样品的焊料层孔隙安全分布范围;

63.图13所示为焊料层孔隙率为1%标定样品的焊料层孔隙安全分布区域图;如图13所示,以芯片焊盘区域中心点116为原点,设不合格焊料层孔隙分布区域的最大半径为r

i 163,焊料层孔隙与芯片焊盘区域中心点的间距≥ri的区域为合格的焊料层孔隙分布区域161,焊料层孔隙与芯片焊盘区域中心点的间距<ri的区域为不合格的焊料层孔隙分布区域162,其中i=1,2,3,4;

64.如图13所示,设定nmos晶体管热阻标准判据中最大焊料热阻为h,最大总热阻为z;

65.若满足条件a(即h≥h1,z≥z1),则焊料层孔隙与芯片焊盘区域中心点的间距≥r1的区域为待测样品焊料层孔隙的安全分布范围;

66.满足条件b(即h1≥h≥h2,z1≥z≥z2),则焊料层孔隙与芯片焊盘区域中心点的间距≥r2的区域为待测样品焊料层孔隙的安全分布范围;

67.若满足条件c(即h2≥h≥h3,z2≥z≥z3),则焊料层孔隙与芯片焊盘区域中心点的间距≥r3的区域为待测样品焊料层孔隙的安全分布范围;

68.若满足条件d(即h3≥h≥h4,z3≥z≥z4),则焊料层孔隙与芯片焊盘区域中心点的间距≥r4的区域为待测样品焊料层孔隙的安全分布范围;

69.若满足条件e(即h4≥h,z4≥z),则整个芯片焊盘区域112无焊料层孔隙安全分布区域,芯片焊盘区域112任何位置的焊料层孔隙均不可被接收。

70.上述具体实施可由本领域技术人员在不背离本发明原理和宗旨的前提下以不同的方式对其进行局部调整,本发明的保护范围以权利要求书为准且不由上述具体实施所

限,在其范围内的各个实现方案均受本发明之约束。