一种基于FPGA的探测器读出电子学系统

一种基于fpga的探测器读出电子学系统

技术领域

1.本技术属于核电子学领域,具体涉及一种基于fpga的多通道、高密度读出电子学系统。

背景技术:

2.目前,针对各种不同粒子探测器的信号读出,采用最广泛的是全波形数字化。在这种技术中,它首先将输入的核信号进行积分成形,把弱信号变成可观测的大幅度信号,随后进行快速波形采样,采样后的信号送入可编程器件进行实时处理。当通道数目少时,这种技术发挥了很大优势。随着粒子探测器的发展,为了获得高精度的定位性能,多通道粒子探测器应运而生。对于上百通道的高密度、多通道粒子探测器来说,全波形数字化技术将使探测器读出电子学系统变得十分庞大。另一个解决办法是采用专用集成电路asic芯片设计,它将所有复杂的功能都囊括在一款芯片里。asic芯片的功能非常强大,并且兼具通道多,功率低,抗辐照等优秀品质,但是导致其研发周期也是相当漫长,一般在5至10年的时间才能研发出一款具有针对性的、实用的asic芯片,并且造价很高,针对每一个应用场景都需要针对性的研究和开发。

技术实现要素:

3.本发明针对现有多通道粒子探测器信号读出方案中的缺陷,提出了一种紧凑型、低噪声、兼备电荷和时间同时测量的粒子探测器信号读出方案。其技术方案为,一种基于fpga的探测器读出电子学系统,包括多路qtc电路和多路数字部分,每一路qtc电路包括运算放大器、积分电容cf、二极管和电阻r;数字部分包括电压比较器和fpga,所述运算放大器负输入端分别连接电阻r、二极管、积分电容cf和外部探测器,所述电阻r接电源v

dis

,所述二极管和积分电容cf并联,且均接入运算放大器的输出端,运算放大器的正向端连接电源v

+

,其输出端与电压比较器的正向端连接,所述电压比较器的负向端与电源v

th

连接,所述电压比较器集成在fpga上。

4.优选的,所述fpga上集成时间数字转换器tdc,使用时间数字转换器tdc对电压比较器输出的数字脉冲进行数字化。

5.优选的,fpga内部采用sstl接收器作为电压比较器,阈值电源v

th

连接到对应bank的v

ref

引脚,在此bank中,所有的i/o引脚共用一个v

th

。

6.优选的,负电流脉冲测量过程为:二极管的阳极接放大器的负向输入端,阴极接放大器的输出端;在静态情况下,即没有输入电流脉冲的情况,id(t)=ic(t)=0,i

diode

(t)=i0=v

dis

/r,二极管导通,id(t)为探测器的输出电流,ic(t)是经过积分电容cf上电流,i

diode

(t)为经过二极管上的电流,i0为经过电阻r上的电流,此时,电源v

+

等于二极管的导通电压v

on

,运算放大器的输出基线是v

+

减去v

on

等于0v,二极管阳极电压是v

on

,阴极电压是0v。

7.优选的,负电流脉冲测量过程为:

当有电流脉冲注入qtc电路的时候,一开始由于电流脉冲处于上升部分,极短的时间内,id(t)《i0,电源v

dis

和电阻r提供了放电路径;当输入电流id(t)大于放电电流i0时,即id(t)》i0,探测器的电流一方面通过电源v

dis

和电阻r放电,另一方面开始在积分电容cf上进行充电,此后,运算放大器的输出电压大于0v,导致二极管阳极和阴极的压差小于v

on

,二极管截止,即i

diode

(t)≈0,运算放大器的输出电压一直增大,直到探测器的输出电流id(t)再一次小于放电电流i0,在此之后,探测器输出的电流都将经过电源v

dis

和电阻r,不会再有多余的电荷在积分电容cf上进行积分,同时,积分电容cf上已经存储的电荷也开始从v

dis

和电阻r上进行放电,直到将电容上积分的电荷全部泄放,运算放大器输出的基线电压再次变为0v,二极管导通,整个qtc电路再一次回到静态工作时的情况。

8.优选的,负电流脉冲测量过程为:运算放大器开始有输出电压时,二极管截止,经过二极管通路的电流i

diode

(t)≈0,由电荷守恒,运算放大器负输入端的电流和为0,得到如下等式:,其中,ic(t)是经过积分电容cf上电流,即ic(t)=cf(du(t)/dt),假设积分电容cf上开始有积分电荷的时刻为0时刻,此时运算放大器输出电压开始从0v增大,运算放大器输出信号的脉宽为t,在t时刻,运算放大器反馈电容cf所积累的电荷已经全部泄放,因此运算放大器输出电压再次回到0v,在0-t这段时间内,运算放大器的从0v开始增加到最值后再次回到0v,对上式进行积分得到:,为电流脉冲的面积,近似为电荷总量q,得到q=i0×

t,实现了电荷向脉冲宽度的转换。

9.优选的,正电流脉冲测量过程为:1)二极管的阴极接运算放大器的负向输入端,阳极接运算放大器的输出端;2)电源v

+

为1.8v,在电路静态的情况下,即没有输入电流脉冲时,运算放大器的输出电压为v

+

与v

on

之和;与电阻r相连的v

dis

为0v,此时放电电流i0反向,电流值为v

+

/r;静态时,二极管阳极的电压为v

+

与v

on

之和,二极管阴极的电压为v

+

,此时二极管正常导通;当有正电流脉冲输入电路时,在id(t)》i0以后,在积分电容cf上积分,使运算放大器输出端产生负向的脉冲,导致二极管截止,直到积分电容cf上积分的电荷全部被电阻r泄放,电路才会再次回到静态时的情况;3)qtc电路得到了电荷正比于信号脉宽的电压信号,电压比较器将qtc信号与一个指定的阈值v

th

进行比较,电压比较器输出的数字信号宽度,即正比于电流脉冲的总电荷,数字信号的前沿代表了信号的到达时间,以此使能了同时的电荷和时间测量。

10.有益效果1.本方案适用于小型化、低噪声、多通道的核电子学系统设计,并兼备电荷和时间同时测量的能力。

11.2.采用放大器、积分电容、电阻等分立元件实现了单路电荷向信号宽度的转换,同

时利用fpga多资源、多i/o、低功耗等优势,实现多通道、高密度、小型化的粒子探测器读出电子学系统。

附图说明

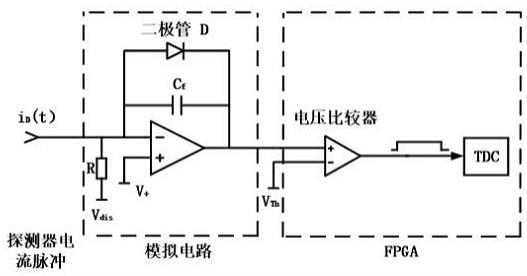

12.图1为基于fpga的紧凑型电荷读出原理图。

13.图2为针对负电流脉冲测量的直接电荷时间转换器qtc原理图。

14.图3为针对正电流脉冲测量的直接电荷时间转换器qtc原理图。

15.图4为基于fpga的小型化核电子学系统。

具体实施方式

16.以下详细说明都是例示性的,旨在对本技术提供进一步的说明。除非另有指明,本文使用的所有技术和科学术语具有与本技术所属技术领域的普通技术人员通常理解的相同含义。需要注意的是,这里所使用的术语仅是为了描述具体实施方式,而非意图限制根据本技术的示例性实施方式。

17.本发明的技术方案通过直接电荷时间转换qtc技术实现:一种基于fpga的探测器读出电子学系统,包括多路qtc电路和多路数字部分,每一路qtc电路包括运算放大器、积分电容cf、二极管和电阻r;数字部分包括电压比较器和fpga,所述运算放大器负输入端分别连接电阻r、二极管、积分电容cf和外部探测器,所述电阻r接电源v

dis

,所述二极管和积分电容cf并联,且均接入运算放大器的输出端,运算放大器的正向端连接电源v

+

,其输出端与电压比较器的正向端连接,所述电压比较器的负向端与电源v

th

连接,所述电压比较器集成在fpga上。在 fpga上集成时间数字转换器tdc,使用时间数字转换器tdc对电压比较器输出的数字脉冲进行数字化。在fpga内部采用sstl接收器作为电压比较器,阈值电源v

th

连接到对应bank的v

ref

引脚,在此bank中,所有的i/o引脚共用一个v

th

。

18.所述的运算放大器用于放大来自粒子探测器的弱电流脉冲信号,通过运算放大器反馈回路中积分电容cf将弱信号进行积分,积分后的电压幅度可达百毫伏特mv或者若干伏特v;所述的积分电容cf与运算放大器构成电荷存储器,对输入的弱电流脉冲所包含的总电荷进行积分和存储;所述的二极管在电路处于静态时,即没有输入电流脉冲的情况下,提供了一个直流电流回路,由于二极管的钳位作用,使运算放大器的负向输入端与输出端之间产生一个恒定的压降,也就是二极管的导通压降,在有输入电流脉冲的情况下,由于运算放大器

‘

虚短’的作用,运算放大器负向输入端的电压不变,而电流脉冲在cf上积分后,运算放大器输出的电压升高或者降低(根据正电流脉冲和负电流脉冲的情况而定),导致二极管两端的压差小于导通电压,此后二极管截止,所有电荷都从电阻r上进行泄放;所述电阻r(用于放电,也称为放电电阻)用于持续地为积分电容cf提供一个放电回路。

19.所述的电源v

+

连接到运算放大器的正向端,在负电流脉冲测量的情况下,此电压值等于二极管的导通压降v

on

,v

+

通过二极管将放大器的输出基线钳位在0v,而在正电流脉

冲测量的情况下,此电压值等于1.8v,此时v

+

通过二极管的钳位作用将运算放大器的输出基线钳位在(v

+

+v

on

,为两个电压之和);所述的电源v

dis

与电阻r共同提供了一个恒定的放电路径;所述的电源v

th

用于提供信号比较所需要的阈值,在负电流脉冲输入的情况下,v

th

略大于运算放大器的输出基线,在正电流脉冲输入的情况下,v

th

略小于放大器的输出基线;所述的fpga在其内部实现的功能包括:使用lvds接收器或者电压参考型接收器(sstl和hstl接收器)实现电压比较器的功能、使用时间数字转换器tdc实现脉冲宽度测量和前沿信息提取的功能、使用内部fifo实现数据缓存和传输的功能、完成高速数据传输引擎的功能。

20.其中,本发明中包括两部分:模拟部分和数字部分。

21.所述的模拟部分包括运算放大器、积分电容cf、二极管、电阻r、电源v

+

、电源v

dis

,这些元件构成了一个电荷时间转换器qtc。

22.所述的数字部分包括电源v

th

和fpga,完成了qtc输出电压信号的脉宽和时间提取。若在fpga内部采用电压参考型接收器作为电压比较器,阈值v

th

连接到fpga的bank上固定的v

ref

引脚,此时这个bank上任意一个i/o引脚都可以作为一个电压比较器的正向输入端,也就可以在fpga内部实现一路电荷和时间测量。因此,对于具有几百个i/o引脚的fpga来说,容易实现几百个通道的高密度、小型化的核电子学系统。

23.结合图2,首先将电荷测量原理表述如下:以负电流脉冲测量为例,此时,二极管的阳极接放大器的负向输入端,阴极接放大器的输出端;在静态情况下,即没有输入电流脉冲的情况,id(t)=ic(t)=0,i

diode

(t)=i0=v

dis

/r,二极管导通,此时,电源v

+

为二极管的导通电压v

on

,放大器的输出基线是v

+-v

on

=0v(即两个电源之差为0v),应当注意的是,此时二极管阳极电压是v

on

,阴极电压是0v;当有电流脉冲注入qtc电路的时候,一开始由于电流脉冲处于上升部分,这段极短的时间内,id(t)《i0,v

dis

和电阻r提供了放电路径;当探测器的输入电流id(t)大于放电电流i0时(i0为经过电阻r上的电流),即id(t)》i0,探测器的电流,一方面通过v

dis

和电阻r的支路放电,另一方面开始在积分电容cf上进行充电,此后,放大器的输出电压大于0v,导致二极管阳极和阴极的压差小于v

on

,二极管截止,即i

diode

(t)≈0,此后放大器的输出电压一直增大,直到探测器的输出电流id(t)再一次小于放电电流i0,在此之后,探测器输出的电流都将经过v

dis

和r的支路,不会再有多余的电荷在电容cf上进行积分,同时,电容cf上已经存储的电荷也开始从v

dis

和r的支路进行放电,直到将电容上积分的电荷全部泄放,放大器输出的基线电压再次变为0v,二极管导通,整个电路再一次回到静态工作时的情况。

24.综上,我们可以对电路的工作原理进行公式推导,由于我们主要关心的是放大器开始有输出电压的时间段,在这段时间内,二极管截止,经过二极管通路的电流i

diode

(t)≈0,由电荷守恒,流入节点a(电阻r和探测器的连接处为节点a,即运算放大器负输入端的电流和为0)的电流和为0,可以得到如下等式:,其中,ic(t)是经过积分电容cf上电流,即ic(t)=cf(du(t)/dt),假设积分电容cf上开始有积分电荷的时刻为0时刻,此时放大器输出电压开始从0v增大,放大器输出信号的脉宽为t,如图2所示,在t时刻,放大器反馈电容cf所积累的电荷已经全部泄放,因此放大器输

出电压再次回到0v。在0-t这段时间内,即放大器的输出电压从0v开始增加到最值后再次回到0v,对上式进行积分得到:,而为电流脉冲的面积,约等于电荷总量q(由于在0时刻前,id(t)《i0,在放大器输出电压大于0之前,有少量电荷通过v

dis

和电阻r的放电,但是由于电流脉冲前沿很快,这部分电荷损失,忽略不计),因此,我们得到q=i0×

t,实现了电荷向脉冲宽度的转换。

25.正电荷与负电荷测量原理类似,借助图3,简述如下:1)二极管阴极接放大器的负向输入端,阳极接放大器的输出端;2)电压v

+

变为1.8v,在电路静态的情况下,即没有输入电流脉冲时,放大器的输出电压变为(v

+

+v

on

,为两个电源之和);3)与电阻r相连的v

dis

变为0v,此时放电电流i0反向,电流值为v

+

/r。静态时,二极管阳极的电压为(v

+

+v

on

,为两个电源之和),二极管阴极的电压为v

+

,此时二极管正常导通。当有正电流脉冲输入电路时,在id(t)》i0以后,在积分电容cf上积分,使放大器输出端产生负向的脉冲,导致二极管截止,直到积分电容cf上积分的电荷全部被电阻r泄放,电路才会再次回到静态时的情况。

26.qtc电路得到了电荷正比于信号脉宽的电压信号。数字部分主要由fpga构成,如图1所示。在fpga内部,首先由等效的电压比较器(lvds接收器或者电压参考型接收器)将qtc信号与一个指定的阈值v

th

进行比较,电压比较器输出的数字信号宽度,即正比于电流脉冲的总电荷,数字信号的前沿代表了信号的到达时间,以此使能了同时的电荷和时间测量。

27.在fpga内部,使用时间数字转换器tdc对电压比较器输出的数字脉冲进行数字化。为了实现高密度的电子学,权衡fpga资源利用率,采用粗时间计数器来实现;为了实现高精度的电荷和时间测量,采用基于时间内插的tdc来测量数字信号脉宽和前沿。

28.图4提供了一种设计实例,在fpga内部采用sstl接收器作为电压比较器,阈值v

th

连接到对应bank的v

ref

引脚,在此bank中,所有的i/o引脚共用一个v

th

。每一路qtc电路由放大器、电容cf、电阻r、二极管、电源v

+

,电源v

dis

构成,采用四路放大器商用芯片,4路qtc电路可以限定在10

×

10 mm2以内,因此100路qtc电路可以限定在50

×

50 mm2,与asic电路的尺寸相当。

29.以上所述仅为本技术的优选实施例而已,并不用于限制本技术,对于本领域的技术人员来说,本技术可以有各种更改和变化。凡在本技术的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本技术的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1