一种基于无机钙钛矿的伽马光子探测器读出电子学系统

1.本发明属于γ成像探测器数据采集系统领域,具体为一种基于无机钙钛矿的伽马光子探测器读出电子学系统。

背景技术:

2.γ射线探测在核医学成像、无损检测、空间物理等领域具有很广泛的应用,人们一直致力于开发高性能的γ光子探测器。相较于x射线,γ光子的能量较高,穿透能力较强,因此要求伽马探测器材料的平均原子序数z较高,探测器的厚度也很厚。传统的高纯锗hpge探测器,对伽马射线进行探测时,可以获得很好的能量分辨率,但是由于其带隙band gap较小,约0.7ev,小于一般半导体探测器的带隙,常温下载流子很容易从价带跳到导带,造成常温下的探测器暗噪声较大,因此hpge探测器只能在低温下工作。为了寻找常温下高能量分辨的探测器,人们利用半导体合成技术研发了新型的γ探测器,如碲化镉cdte、碲锌镉czt等,这些探测器也已经得到商用。

3.为了获得更高能量分辨率的γ探测器,只有空穴作为载流子的无机钙钛矿cspbbr3探测器应运而生。无机钙钛矿cspbbr3作为x射线探测器,包括两种载流子,电子和空穴。由于晶格的缺陷,电子容易被俘获,造成探测器的信噪比较差。而最近,只有空穴作为载流子的无机钙钛矿cspbbr3探测器,克服了电子易俘获的缺陷,通过晶体生长技术实现了只有空穴作为载流子的超高能量分辨率(小于1.4%)γ探测器。此类探测的特征参数μτh(μ是空穴的迁移率,τh是空穴的寿命)较高,导致探测器输出信号的持续时间较长,不仅如此,探测器没有雪崩倍增效应,导致探测器的输出电流脉冲较小。由于此类探测器比较新颖,目前市场上还没有对应的探测器信号处理和数据获取系统。

技术实现要素:

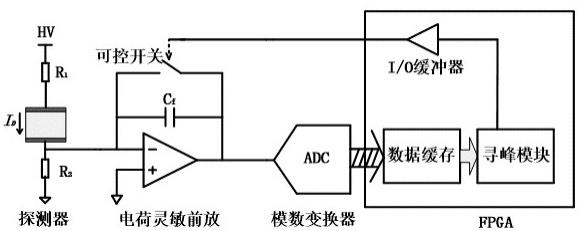

4.基于上述问题,本技术提供一种针对空穴型无机钙钛矿cspbbr3探测器电荷测量方案,其技术内容为,一种基于无机钙钛矿的伽马光子探测器读出电子学系统,包括放电型电荷灵敏放大电路和数字电路,所述放电型电荷灵敏放大电路包括放大器,电容cf和可控开关,所述数字电路包括adc转换器和fpga,所述放大器的负输入端分别连接电容cf、可控开关和探测器,所述电容cf、可控开关并联后与放大器的输出端连接,所述放大器正输入端接地,所述放大器的输出端与adc转换器连接,所述adc转换器与fpga连接,所述可控开关与fpga上的i/o缓冲器连接。

5.优选的,所述探测器两端分别通过电阻r1、电阻r2连接,所述电阻r1接电源hv,电阻r2接地。

6.优选的,所述fpga上设有数据采集模块、数据缓存模块和寻峰模块,所述寻峰模块用于从波形中提取最值。

7.优选的,当fpga内部的i/o缓冲器输出低电平时,可控开关处于打开状态;当i/o缓

冲器处于高电平时,可控开关处于关闭状态。

8.优选的,静态时,即没有电流脉冲注入放大器时,可控开关处于打开状态。

9.优选的,当探测器输出正电流脉冲时,此电流脉冲在电容cf上积分,放大器输出负向的电压脉冲,由于可控开关处于打开状态,电容cf上积分的电荷,没有泄放回路,放大器一直保持输出电压值,adc转换器对放大器输出的波形进行全波形采样,实时送入fpga进行后处理,所述的fpga接收adc转换器采样后的波形数据,在fpga内部实现高速数据缓存,从波形中提取最值,在找到最值后,立即通过fpga的i/o缓冲器来控制可控开关,使其处于闭合状态。

10.优选的,在fpga找到一个事例波形中的最值后,即最小值,i/o缓冲器使可控开关闭合,导致cf上积分的电荷通过开关这一支路迅速泄放,放大器的电压波形迅速回到基线值;之后,fpga内部的i/o缓冲器改变输出状态,使可控开关再次打开,电路回到静态时的工作状态。

11.优选的,所述放电型电荷灵敏放大电路和数字电路均设有多组。

12.有益效果1.空穴载流子型的无机钙钛矿cspbbr3探测器作为γ成像探测器是一种全新的成像方案,本发明为此类新型探测器输出的弱电流脉冲提供了一种多通道、低噪声、高精度的电荷测量方案。

13.2.本发明解决了此类新型γ探测器的信号提取、高速数字化、事例缓存以及数据传输等问题。

14.3.本发明所提供的电荷测量方案很容易进行系统级的扩展,在核医学成像(如单光子发射计算机断层成像spect)、航空航天等领域具有潜在的应用价值。

附图说明

15.图1为基于快速放电型电荷灵敏放大器的电荷测量原理框图。

16.图2为空穴信号输入情况下的放电型电荷灵敏前放原理图。

17.图3为基于fet模拟开关的放电型电荷灵敏放大器原理图。

18.图4为钙钛矿cspbbr

3 γ成像探测器128通道读出电子学系统框图。

19.图5为空穴信号输入情况下的放电型电荷灵敏前放输出的电压波形图。

具体实施方式

20.以下详细说明都是例示性的,旨在对本技术提供进一步的说明。除非另有指明,本文使用的所有技术和科学术语具有与本技术所属技术领域的普通技术人员通常理解的相同含义。需要注意的是,这里所使用的术语仅是为了描述具体实施方式,而非意图限制根据本技术的示例性实施方式。

21.一种基于无机钙钛矿的伽马光子探测器读出电子学系统,包括多组放电型电荷灵敏放大电路和数字电路,每组所述放电型电荷灵敏放大电路包括放大器(所述的放大器具有高输入阻抗,输入阻抗在1tω左右),电容cf和可控开关,每组所述数字电路包括adc转换器和fpga,所述放大器的负输入端分别连接电容cf、可控开关和探测器,所述探测器两端分别通过电阻r1、电阻r2连接,所述电阻r1接电源hv,电阻r2接地(电阻r1电阻r2为偏置电阻)。

所述电容cf、可控开关并联后与放大器的输出端连接,所述放大器正输入端接地,所述放大器的输出端与adc转换器连接,所述adc转换器与fpga连接,所述可控开关与fpga上的i/o缓冲器连接。

22.所述的电容cf与放大器构成了电荷积分电路,将输入的弱电流信号进行积分放大。

23.fpga实现了如下功能:1)对adc转换器的采样波形进行缓冲存储;2)寻峰模块对adc转换器采样的波形寻找最值;3)实现对电荷灵敏放大器反馈环路中的可控开关/fet开关进行开/关控制;4)实现ddr3 sdram控制引擎模块,对处理后的adc采样数据进行实时存储;5)实现pcie控制引擎模块,实时读取外存ddr3存储器的数据。

24.所述fpga上设有数据采集模块、数据缓存模块和寻峰模块,所述寻峰模块用于从波形中提取最值。

25.当fpga内部的i/o缓冲器输出低电平时,可控开关处于打开状态;当i/o缓冲器处于高电平时,可控开关处于关闭状态。

26.静态时,即没有电流脉冲注入放大器时,可控开关处于打开状态。

27.当探测器输出正电流脉冲时,此电流脉冲在电容cf上积分,放大器输出负向的电压脉冲,由于可控开关处于打开状态,电容cf上积分的电荷,没有泄放回路,放大器一直保持输出电压值,adc转换器对放大器输出的波形进行全波形采样,实时送入fpga进行后处理,所述的fpga接收adc转换器采样后的波形数据,在fpga内部实现高速数据缓存,从波形中提取最值,在找到最值后,立即通过fpga的i/o缓冲器来控制可控开关,使其处于闭合状态。

28.在fpga找到一个事例波形中的最值后,即最小值,i/o缓冲器使开关闭合,导致cf上积分的电荷通过开关这一支路迅速泄放,放大器的电压波形迅速回到基线值;之后,fpga内部的i/o缓冲器改变输出状态,使可控开关再次打开,电路回到静态时的工作状态。

29.所述的可控开关属于模拟元器件,可通过单个晶体管或者场效应管fet实现,也可通过商用模拟开关实现。可控开关由fpga的一个i/o引脚控制,通过fpga内部i/o驱动器的三种状态:高电平(一般为2.5v)、低电平(一般为0v)、高阻hz来控制。根据可控开关的控制模式,可任选两种状态控制可控开关的打开和闭合。

30.无机钙钛矿cspbbr3作为γ成像探测器,属于多通道成像应用。本发明的技术方案可以进行多通道扩展。由于本方案所需要的模拟元器件较少,可以放在一起,统称为前端电子学fee,数字部分daq包括多通道adc、高性能fpga和大容量外部存储器,多通道adc采用商用的ads52j90,可配置成16通道、100m采样,也可配置成32通道、50m采样;高性能fpga采用intel公司的stratix iv系列。为实现128通道的电荷测量,fee由128路的ad8065、电容、可控开关构成;daq由4片ads52j90(配置成50m采样、32通道)、一片stratix iv fpga、大容量ddr3 sdram存储器构成。结构简单,灵活性强。

31.如图5所示的波形,虚线表示的是传统rc型电荷灵敏放大器输出的电压波形,为了避免积分电容cf上的电荷损失,反馈电阻r的值(本发明用可控开关替换了r)一般很大,在10-500mω的量级。目的是为了让cf在电荷积分过程中尽可能少地泄放电荷,以此达到电荷灵敏放大器输出电压幅度正比于输入电荷量的要求。图5中所示的实线波形是本发明中放大电路的输出波形,经过adc转换器实时全波形采样后的数字信号送入fpga内部,通过fpga

内部的寻峰模块找到最值,立刻闭合可控开关,使电容cf上积分的电荷全部快速泄放。因此,放电型电荷灵敏前放输出的电压波形只包括了上升沿和很短一段电压保持时间。相较于传统的rc型电荷灵敏放大器而言,放电型电荷灵敏放大器输出的电压脉冲宽度较窄,适用于高计数率下的应用。

32.为了便于理解和实施本发明中的技术方案,以图3为例,选用n型金属氧化物半导体nmos场效应管fet作为可控开关。nmos fet的栅极g作为可控开关的控制端,源极s与放大器的输出相连,漏极d与放大器的负向输入端相连。由于fpga的i/o引脚输出只有三种状态:高电平(实例中2.5v)、低电平(实例中0v)和高阻hz,选用前两个状态高电平和低电平来控制可控开关的打开和闭合。当nmos fet作为开关使用时,如果栅极g和源极s的电压差大于开门阈值电压v

gs(th)

(一般为0.7v左右),nmos fet的漏极d与源极s导通,相当于可控开关闭合;如果栅极g和源极s的电压差小于v

gs(th)

时,nmos fet的漏极d和源极s处于截止状态,此时通过nmos fet的漏电流很小,导致这个支路的等效阻抗很大,相当于rc型电荷灵敏放大器中的mω级电阻r,等效为开关处于打开状态。

33.在实际使用中,为了使nmos fet得到更好的反向截止特性,栅极g和源极s的电压差远小于v

gs(th)

。因此,图3中在放大器的正向输入端引入一个电平vb,本实例中为1v。当fpga的i/o缓冲器输出低电平0v时,nmos fet的栅极g和源极s的电压差为-1v,导致nmos fet的反向截止等效阻抗远大于mω;而在放电工作的情况下,fpga的i/o缓冲器输出2.5v,此时栅极g和源极s的电压差为1.5v》 vgs(th),使nmos fet开关正常导通,不影响正常使用。

34.本发明很容易进行多通道的扩展,以图4为例,结合商用ads52j90高速、多通道adc转换器(通过配置可实现64通道100m采样或者128通道50m采样)实现了128通道全波形采样daq系统。由于无机钙钛矿cspbbr3探测器输出的电流脉冲持续时间很长,对于这样的慢速信号,采用50m采样率或者更低的采样率即可。放电型电荷灵敏前放只包括放大器、可控开关、电容cf三个主要元器件,128通道的前端版fee总尺寸可限定在一定范围内。

35.采用sot23封装的ad8065高输入阻抗放大器,加上4片ads52j90、fpga和ddr3 sdram大容量存储器,实现基于cspbbr3材料的γ成像探测器128通道读出电子学系统。此128通道读出电子学系统包括前端板fee和后端daq系统。

36.所述的前端版fee包括128路放电型电荷灵敏放大电路;所述的后端daq系统包括4片ads52j90、stratix iv fpga和大容量外部存储器。其中,每片ads52j90被配置成50msps、10bit、32通道工作模式,四片共构成了128通道adc。高性能的stratix iv fpga实现了adc数据缓存、寻峰/控制开关、ddr3 sdram存储器的写控制、pcie引擎对ddr3 sdram的读控制等功能。

37.以上所述仅为本技术的优选实施例而已,并不用于限制本技术,对于本领域的技术人员来说,本技术可以有各种更改和变化。凡在本技术的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本技术的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1