信息处理装置及磁传感器系统的制作方法

1.本发明涉及信息处理装置、磁传感器系统。

背景技术:

2.作为公报记载的现有技术,在具有多谐振荡器振荡电路的磁场传感器中,多谐振荡器振荡电路由2个cmos反相器、与电阻串联连接的非晶丝、电容构成,将电源电压设定为3v以下,将电阻r和非晶丝的串联电阻设定为500ω以下,存在构成为2个cmos反相器的输入电压保持为阈值电压的时间宽度根据外部施加磁场而变化的调频型磁场传感器(参照专利文献1)。

3.[现有技术文献]

[0004]

[专利文献]

[0005]

[专利文献1]日本特开2004-108778号公报

技术实现要素:

[0006]

[本发明要解决的课题]

[0007]

例如,在使用磁阻抗效应元件作为感应磁场的感应元件的磁传感器中,向感应元件供给交流电流,并且根据感应元件中的阻抗变化来检测磁性。此时,有时通过感应元件的频率变化来检测出感应元件的阻抗变化。

[0008]

磁阻抗效应元件由于高磁导率合金磁体的趋肤效应,在外部磁场中阻抗灵敏地变化。在趋肤效应中,电流流过的表面层的深度(skindepthδ)由δ=√(2ρ/ωμ)(ρ:电阻率,ω:通电电流的角频率,μ:与通电电流成直角方向的最大微分磁导率)表示,所以频率越高则δ越薄,阻抗变化越大。因此,频率越高,越容易提高使用了磁阻抗效应元件的磁传感器的灵敏度。

[0009]

但是,当从感应元件输出的输出信号的频率变高时,有时测定频率时的采样速度不足,频率的测定精度降低。

[0010]

另外,在检测微小磁场的情况下,所得到的频率变化也变小,有时在有限的采样速度下频率分辨率不充分而无法检测出磁场变化。因此,希望放大由外部磁场引起的频率变化率,提高频率测定的检测极限。

[0011]

本发明提供如下的信息处理装置以及磁传感器系统:即使从磁传感器输出的输出信号的频率变高,频率的测定精度也难以降低,即使是微小频率变化率,频率测定的检测界限也高。

[0012]

[用于解决课题的手段]

[0013]

这样,根据本发明,提供信息处理装置,其具备:取得部,其取得由磁传感器输出的输出信号,输出信号具有根据磁场的强度决定的频率而振荡;频率确定部,其利用输出信号与基准信号的干扰来确定输出信号的频率,基准信号具有作为基准的频率即基准频率,以及磁场算出部,其根据所确定的输出信号的频率来算出磁场的强度。

[0014]

在此,频率确定部可以通过干扰而在维持频率变化量不变的状态下使输出信号的频率成为低频来提高频率变化率,并使用成为低频的频率来确定输出信号的频率。

[0015]

此外,频率确定部可以通过干扰而基于波形来确定输出信号的频率,所述波形是基于输出信号与基准信号的相位差而得到的波形。

[0016]

进而,频率确定部可以基于通过将波形相对于时间平均化而生成的三角波来确定输出信号的频率。

[0017]

进而,频率确定部可以使累计并平均化后的输出信号与基准信号干扰,从而生成三角波。

[0018]

而且,频率确定部可以使用多个频率作为基准频率而使输出信号和基准信号干扰,从而生成三角波。

[0019]

另外,可以通过逻辑运算和/或相位比较器进行干扰。

[0020]

进而,频率确定部可以通过利用超外差方式对输出信号和基准信号进行混频来进行干扰。

[0021]

此外,频率确定部可以利用通过输出信号和基准信号之间的干扰而产生的混叠来确定输出信号的频率。

[0022]

而且,频率确定部可以通过改变针对输出信号的采样频率作为基准信号,由此进行干扰。

[0023]

另外,频率确定部可以使用d-触发器进行干扰。

[0024]

另外,频率确定部可以使用数字信号输入端口的采样时钟信号进行干扰。

[0025]

另外,根据本发明,提供磁传感器系统,其包括:磁传感器,该磁传感器具备:感应元件和电容元件串联连接的延迟生成部、和连接于延迟生成部的电位供给部,感应元件通过磁阻抗效应来感应磁场,电位供给部以使得频率由延迟生成部设定的交流电流流过延迟生成部的方式供给电位,磁传感器输出交流电流作为输出信号;频率确定部,其利用输出信号与基准信号的干扰,确定输出信号的频率,基准信号具有作为基准的频率即基准频率;以及磁场算出部,其根据所确定的输出信号的频率,算出磁场的强度。

[0026]

[发明的效果]

[0027]

根据本发明,能够提供如下的信息处理装置以及磁传感器系统:即使从磁传感器输出的输出信号的频率变高,频率的测定精度也难以降低,即使是微小频率变化率,频率测定的检测界限也高。

附图说明

[0028]

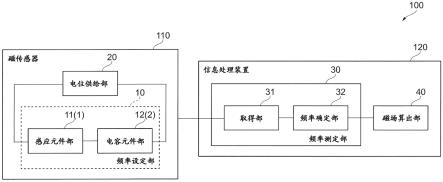

[图1]是说明应用第1实施方式的磁传感器系统的图。

[0029]

[图2]感应元件的一例的说明图。(a)是感应元件的俯视图,(b)是沿着(a)的iib-iib线的感应元件的剖视图。

[0030]

[图3]表示感应元件对磁场的电特性的图。(a)是说明在感应元件的感应部的长边方向上施加的磁场与感应元件的阻抗之间的关系的图。(b)是说明在感应元件的感应部的长边方向上施加的磁场与感应元件的电阻之间的关系的图。(c)是说明在感应元件的感应部的长边方向上施加的磁场与感应元件的电抗之间的关系的图。(d)是说明在感应元件的感应部的长边方向上施加的磁场与感应元件的电感之间的关系的图。

[0031]

[图4]说明应用第1实施方式的磁传感器的图。(a)是用逻辑符号表示的等效电路,(b)是用晶体管表示的等效电路,(c)是将(b)变形后的等效电路。

[0032]

[图5]是说明在频率设定部为rc串联电路的情况下应用第1实施方式的磁传感器的动作的时序图。(a)是图4的(c)所示的磁传感器的等效电路,(b)是以接地电位为基准的α点、β点以及γ点的各电位的时序图,(c)是以γ点的电位为基准的α点、β点的各电位的时序图,(d)是以α点的电位为基准的β点、γ点的各电位的时序图。

[0033]

[图6]是使用逻辑运算使输出信号和基准信号干扰的电路结构的概念图。

[0034]

[图7](a)~(e)是表示逻辑运算部和三角波生成部的动作的图。

[0035]

[图8]是使用超外差方式对输出信号和基准信号进行混频的电路结构的概念图。

[0036]

[图9]是利用混叠(aliasing)来确定输出信号的频率的电路结构的概念图。

[0037]

[图10](a)~(e)是表示对模拟信号的混叠的图。

[0038]

[图11](a)~(e)是表示对数字信号的混叠的图。

[0039]

[图12](a)是在针对数字信号的混叠中,对采样频率为300mhz、输入信号频率从270mhz变为299.9997mhz时的输出频率及其偏差进行测定的结果。(b)是表示在上述(a)的测定中相对于采样频率与输入频率之差而言的频率误差以及偏差的图。

[0040]

[附图标记的说明]

[0041]

1、感应元件,2、电容元件,10、频率设定部,11、感应元件部,12、电容元件部,20、电位供给部,30、频率测定部,31、取得部,32、频率确定部,40、磁场算出部,100、磁传感器系统,110、磁传感器,120、信息处理装置。

具体实施方式

[0042]

以下,参照附图对本发明的实施方式进行说明。

[0043]

(磁传感器系统100)

[0044]

图1是说明应用第1实施方式的磁传感器系统100的图。磁传感器系统100具备磁传感器110和信息处理装置120。

[0045]

磁传感器110是频率随外部磁场引起的感应元件1的特性变化而变化的振荡电路,可以使用各种振荡电路。例如,在由感应元件1的电感和电容元件形成的lc谐振电路中,当感应元件1的电感因外部磁场而发生变化时,lc谐振频率发生变化,振荡频率也发生变化,因此能够用于磁传感器110。此外,在感应元件1的电阻或电感与电容元件组合而成的rlc串联电路中,由于感应元件1的电阻或电感因外部磁场而发生变化,因此在rlc串联电路中产生的延迟时间发生变化。利用了该延迟时间的变化的张弛式振荡电路的振荡频率也因外部磁场而变化,因此能够用于磁传感器110。如图1所示,磁传感器110具备频率设定部10和向频率设定部10供给电压的电位供给部20。频率设定部10具有包含利用所谓磁阻抗效应的感应元件1的感应元件部11、和包含电容元件2的电容元件部12。需要说明的是,电容元件2是蓄积电荷的元件,有时被称为电容器或电容。

[0046]

感应元件部11和电容元件部12串联连接。感应元件1可以用电阻和电感串联连接而成的等效电路来表示,电阻

·

电感分别随外部磁场变化而变化。通过感应元件部11和电容元件部12串联连接而形成rlc串联电路。需要说明的是,在本实施方式中,感应元件部11和电容元件部12作为延迟生成部的一个例子发挥作用。

[0047]

在频率设定部10中,通过感应元件部11使电容元件部12中的电容元件2反复充放电,从而交流电流流过感应元件部11中的感应元件1。此时,感应元件1的电阻和电感根据磁场或磁场的变化而变化。因此,在频率设定部10中,电容元件2反复充放电的周期发生变化。即,感应元件1中流过的交流电流的频率发生变化。

[0048]

感应元件部11除了感应元件1之外,还可以以串联连接或并联连接的方式包含其他电子元件、例如电阻元件、电感元件。电容元件部12除了电容元件2之外,还可以以串联连接或并联连接的方式包含其他电子元件、例如电阻元件、电感元件。以下,为了简化说明,说明感应元件部11由感应元件1构成,电容元件部12由电容元件2构成的情况。而且,将感应元件部11记作感应元件1,将电容元件部12记作电容元件2。也就是说,感应元件1是感应元件部11,电容元件2是电容元件部12。而且,在图1中,将感应元件部11记作11(1),将电容元件部12记作12(2)。

[0049]

信息处理装置120对流过磁传感器110的交流电流进行处理,求出磁场的强度。

[0050]

信息处理装置120具备测定流过磁传感器110的交流电流的频率的频率测定部30、和基于由频率测定部30测定的频率而算出由后述的感应元件1感应的磁场或磁场的变化的磁场算出部40。

[0051]

频率测定部30测定从磁传感器110振荡出的交流电流的频率,并输出到磁场算出部40。如图所示,频率测定部30具备取得部31和频率确定部32。关于频率测定部30,在后面详细叙述。

[0052]

磁场算出部40根据频率测定部30所确定的频率,算出感应元件1所感应的磁场或磁场的变化。磁场算出部40存储感应元件1的电阻

·

电感与所感应的磁场的强度之间的关系。因此,磁场算出部40根据频率测定部30所测定到的频率算出感应元件1的阻抗,并根据阻抗算出由感应元件1所感应的磁场或磁场的变化。

[0053]

(感应元件1的结构)

[0054]

图2是说明感应元件1的一例的图。图2的(a)是感应元件1的俯视图,图2的(b)是沿图2的(a)的iib-iib线的感应元件1的截面图。在图2的(a)中,设纸面的右方向为x方向,设纸面的上方向为y方向,设纸面的表面方向为z方向。在图2的(b)中,设纸面的右方向为x方向,设纸面的上方向为z方向,设纸面的背面方向为y方向。

[0055]

如图2的(b)所示,感应元件1具备设置在非磁体的基板50上的由硬磁体(硬磁体层503)构成的薄膜磁铁60、与薄膜磁铁60相对层叠并感应磁场的感应电路70、以及磁轭80。需要说明的是,关于感应元件1的剖面结构,将在后面详细说明。

[0056]

在此,磁体中的软磁体是指虽然容易由外部磁场磁化,但当去除外部磁场时会迅速地恢复为没有磁化或磁化较小的状态的所谓矫顽力小的材料。磁体中的硬磁体是指当由外部磁场磁化时,即使去除外部磁场也保持磁化的状态的所谓矫顽力大的材料。

[0057]

需要说明的是,在本说明书中,将构成感应元件1的要素(薄膜磁铁60等)用两位数表示,将被加工成要素的层(硬磁体层503等)用500系列的数字表示。而且,对于要素,有时将被加工成要素的层记载在()内。例如薄膜磁铁60的情况下,记作薄膜磁铁60(硬磁体层503)。图中,记作60(503)。此外,对于被加工成要素的层,将要素记载在()内。例如硬磁体层503的情况下,记作硬磁体层503(薄膜磁铁60)。其他情况也相同。

[0058]

根据图2的(a)说明感应元件1的平面结构。作为一例,感应元件1具有四边形的平

面形状。在此,说明在感应元件1的最上部形成的感应电路70和磁轭80。感应元件1的平面形状为数mm见方。需要说明的是,感应元件1的大小也可以是其他值。

[0059]

感应电路70具备由软磁体(软磁体层505)构成的多个感应部71、将感应部71之间串联连接成曲折状的连接部72、以及设置在串联连接的感应部71的一个端部和另一个端部上的端子部73。

[0060]

感应部71的平面形状为具有长边方向和短边方向的长条状。图2的(a)所示的感应部71将x方向作为长边方向,将y方向作为短边方向。而且,在图2的(a)中,4个感应部71在y方向上并列配置。感应部71显示出磁阻抗效应。因此,将感应元件1表述为磁阻抗元件。

[0061]

各感应部71例如长边方向的长度为1mm~10mm,短边方向的宽度为50μm~150μm。厚度(软磁体层505的厚度)为0.5μm~5μm。相邻的感应部71的间隔为50μm~150μm。而且,感应部71的数量在图2的(a)中示出4个,但也可以是除此之外的数量。感应部71的数量例如为20。

[0062]

需要说明的是,关于各个感应部71的大小(长度、面积、厚度等)、感应部71的数量、感应部71彼此的间隔等,只要根据想要感应即想要测量的磁场的大小等来设定即可。需要说明的是,感应部71也可以是1个。

[0063]

连接部72设置在相邻的感应部71的端部之间,将多个感应部71串联连接。即,连接部72被设置成将相邻的感应部71曲折(蜿蜒状)地连接。在图2的(a)所示的具备4个感应部71的感应元件1中,连接部72为3个。连接部72的数量根据感应部71的数量而不同。例如,如果感应部71为6个,则连接部72为5个。此外,如果感应部71为1个,则不具备连接部72。需要说明的是,连接部72的宽度根据流过感应电路70的电流等来设定即可。例如,连接部72的宽度也可以与感应部71相同。

[0064]

端子部73设置在串联连接的感应部71的一个端部和另一个端部上。在图2的(a)中,在纸面下侧的端部设有端子部73a,在纸面上侧的端部设有端子部73b。在不分别区分端子部73a、73b时,记作端子部73。端子部73用于通过引线接合、导电性粘接剂、机械接触等与电路电连接,只要是这些连接所需的大小即可。需要说明的是,在图2的(a)所示的感应元件1中,由于感应部71为4个,所以端子部73a、73b设置在纸面的左侧。在感应部71的数量为奇数的情况下,将2个端子部73a、73b分开设置在纸面的左右即可。

[0065]

如以上说明的那样,感应电路70构成为通过连接部72将感应部71串联连接成曲折状,从设置在两端部的端子部73a、73b流过电流。因此,记作感应电路70。

[0066]

而且,感应元件1包括与感应部71的长边方向的端部相对设置的磁轭80。在此,具备与感应部71的长边方向的两端部相对地分别设置的2个磁轭80a、80b。需要说明的是,在不分别区分磁轭80a、80b的情况下,记作磁轭80。磁轭80将磁力线诱导至感应部71的长边方向的端部。因此,磁轭80由磁力线容易透过的软磁体构成。该例子中,感应部71和磁轭80由相同的软磁体层505构成。需要说明的是,磁力线在感应部71的长边方向上充分透过的情况下,也可以不具备磁轭80。

[0067]

接着,根据图2的(b)说明感应元件1的剖面结构。感应元件1是在非磁体的基板50上依次配置密合层501、控制层502、硬磁体层503(薄膜磁铁60)、电介质层504、软磁体层505(感应部71和磁轭80)而构成的。

[0068]

基板50为由非磁体形成的基板,例如是玻璃、蓝宝石这样的氧化物基板、硅等半导

体基板或者铝、不锈钢、实施了镍磷镀覆的金属等金属基板等。

[0069]

密合层501是用于提高控制层502与基板50的密合性的层。作为密合层501,使用包含cr或ni的合金为宜。作为包含cr或ni的合金,可列举crti、crta、nita等。密合层501的厚度例如为5nm~50nm。需要说明的是,如果控制层502相对于基板50的密合性没有问题,则不需要设置密合层501。需要说明的是,在本说明书中,未示出包含cr或ni的合金的组成比。在下文中也同样。

[0070]

控制层502为以使由硬磁体层503构成的薄膜磁铁60的磁各向异性容易在膜的面内方向上呈现的方式进行控制的层。作为控制层502,使用cr、mo或w或者包含它们的合金(以下,记作构成控制层502的包含cr等的合金。)为宜。作为构成控制层502的包含cr等的合金,可列举crti、crmo、crv、crw等。控制层502的厚度例如为10nm~300nm。

[0071]

构成薄膜磁铁60的硬磁体层503使用以co为主成分且包含cr或pt中的任意一方或双方的合金(以下,记作构成薄膜磁铁60的co合金。)为宜。作为构成薄膜磁铁60的co合金,可列举cocrpt、cocrta、conicr、cocrptb等。需要说明的是,也可以包含fe。硬磁体层503的厚度例如为1μm~3μm。

[0072]

构成控制层502的包含cr等的合金具有bcc(body-centered cubic(体心立方晶格))结构。因此,构成薄膜磁铁60的硬磁体(硬磁体层503)宜为容易在由bcc结构的包含cr等的合金构成的控制层502上进行晶体生长的hcp(hexagonal close-packed(六方最密堆积))结构。若使hcp结构的硬磁体层503在bcc结构上进行晶体生长,则容易以hcp结构的c轴朝向面内的方式进行取向。因此,由硬磁体层503构成的薄膜磁铁60容易在面内方向上具有磁各向异性。需要说明的是,硬磁体层503是由晶体取向不同的集合形成的多晶,各晶体在面内方向上具有磁各向异性。该磁各向异性来源于晶体磁各向异性。

[0073]

需要说明的是,为了促进构成控制层502的包含cr等的合金及构成薄膜磁铁60的co合金的晶体生长,加热至100℃~600℃为宜。通过该加热,构成控制层502的包含cr等的合金容易进行晶体生长,容易以具有hcp结构的硬磁体层503在面内具有易磁化轴的方式进行晶体取向。也就是说,容易对硬磁体层503的面内赋予磁各向异性。

[0074]

电介质层504由非磁性的电介质构成,使薄膜磁铁60与感应部70之间电绝缘。作为构成电介质层504的电介质,可举出sio2、al2o3、tio2等氧化物、或si3n4、aln等氮化物等。另外,电介质层504的厚度例如为0.1μm~30μm。

[0075]

感应电路70中的感应部71的与长边方向交叉的方向、例如与长边方向正交的短边方向(宽度方向)上被赋予单轴磁各向异性。需要说明的是,与长边方向交叉的方向是指只要相对于长边方向具有超过45

°

且90

°

以下的角度即可。

[0076]

作为构成感应部71的软磁体层505,使用在以co为主成分的合金中添加高熔点金属nb、ta、w等而成的非晶合金(以下,记作构成感应部71的co合金。)为宜。作为构成感应部71的co合金,可列举conbzr、cofeta、cowzr等构成感应部71的软磁体的厚度例如为0.2μm~2μm。

[0077]

感应电路70中的连接部72和端子部73由导电性优异的导电体层506构成。例如,使用ag、cu、au、al等,但没有特别限定。需要说明的是,连接部72和端子部73也可以由不同的导体层构成。另外,也可以将连接部72及端子部73与感应部71形成为一体。由此,无需另外形成感应部71、连接部72及端子部73。

[0078]

密合层501、控制层502、硬磁体层503以及电介质层504被加工成平面形状为四边形(参照图2的(a))。而且,在露出的侧面中的x方向的相对的两个侧面上,薄膜磁铁60成为n极(图2的(b)中的(n))及s极(图2的(b)中的(s))。需要说明的是,连接薄膜磁铁60的n极和s极的线朝向感应电路70中的感应部71的长边方向(在此为x方向)。在此,朝向长边方向是指连结n极和s极的线与长边方向所成的角度小于45

°

。需要说明的是,连接n极和s极的线与长边方向所成的角度越小越好。

[0079]

在感应元件1中,从薄膜磁铁60的n极发出的磁力线一度向感应元件1的外部发出。然后,一部分磁力线经由磁轭80a透过感应部71,并经由磁轭80b再次向外部发出。而且,透过感应部71的磁力线与未透过感应部71的磁力线一起返回到薄膜磁铁60的s极。也就是说,薄膜磁铁60在感应部71的长边方向上施加磁场。

[0080]

需要说明的是,将薄膜磁铁60的n极和s极统称为两磁极,在不区分n极和s极的情况下记作磁极。

[0081]

需要说明的是,如图2的(a)所示,磁轭80(磁轭80a、80b)构成为从基板50的表面侧观察到的形状随着接近感应电路70而变窄。这是为了提高感应部71中的磁通密度(聚集磁力线)。也就是说,增强感应部71的磁场,实现灵敏度的进一步提高。需要说明的是,也可以不缩小磁轭80(磁轭80a、80b)的与感应电路70相对的部分的宽度。

[0082]

在此,磁轭80(磁轭80a、80b)与感应电路70的间隔例如为1μm~100μm即可。

[0083]

在上述中,感应部71由一层软磁体层505构成,但也可以将软磁体层505设为上层软磁体层和下层软磁体层的两层,并在上层软磁体层和下层软磁体层之间设置使上层软磁体层和下层软磁体层反铁磁性耦合(afc:anti-ferro-coupling)的反铁磁性耦合层。作为这样的反铁磁性耦合层,可以举出ru等。通过设置反铁磁性耦合层,从而抑制反磁场,提高感应元件1的灵敏度。

[0084]

另外,也可以在构成感应部71的上层软磁体层与下层软磁体层之间设置降低感应部71的电阻的导电体层。作为导电体层,优选使用导电性高的金属或合金,更优选使用导电性高且非磁性的金属或合金。作为这样的导电体,可以举出铝、铜、银等金属。导电体层的厚度例如为10nm~500nm。通过设置导电体层,能够提高流入感应电路70的交流电流的频率。

[0085]

而且,也可以在构成感应部71的上层软磁体层与下层软磁体层之间设置抑制在上层软磁体层及下层软磁体层发生闭合磁畴的磁畴抑制层。作为这样的磁畴抑制层,可以举出ru、sio2等非磁体、crti、alti、crb、crta、cow等非磁性非晶金属。通过抑制感应部71中的闭合磁畴的产生,可抑制由基于磁畴壁的移动的所谓巴克豪森效应引起的噪声的产生。

[0086]

需要说明的是,也可以使构成感应部71的软磁体层505为超过两层的多层,在各层之间设置反铁磁性耦合层、导电体层或磁畴抑制层。此外,可以将上述反铁磁性耦合层、导体层和磁畴抑制层中的两个或全部组合使用。

[0087]

以上,感应元件1除了感应电路70之外,还包括薄膜磁铁60和磁轭80。薄膜磁铁60是为了对感应电路70中的感应部71施加后述的偏置磁场hb而设置的。在从感应元件1的外部施加偏置磁场hb的情况下,感应元件1不需要具有薄膜磁铁60。在该情况下,不需要具备为了薄膜磁铁60而设置的密合层501、控制层502、硬磁体层503以及电介质层504。也就是说,感应元件1只要在基板50上设置感应电路70即可。在该情况下,磁轭80既可以设置,也可以不设置。

[0088]

作为从感应元件1的外部施加偏置磁场hb的方法,可以列举使用永久磁铁的方法、使用偏置线圈的方法。也可以仅将它们配置在感应元件1的附近,但优选使用由铁氧体磁芯等软磁性材料构成的磁路,抑制由永久磁铁、偏置线圈产生的偏置磁场向外部泄漏的结构。

[0089]

在基板50上设置感应电路70的情况下,若基板50为硅等半导体基板或者铝、不锈钢、实施了镍磷镀覆的金属等金属基板等,则导电性高。在这种情况下,可以在基板50的设置有感应电路70的表面上设置使基板50与感应电路70电绝缘的绝缘层。作为构成这样的绝缘体层的绝缘体,可举出与构成电介质层504的电介质同样的sio2、al2o3、tio2等氧化物、或si3n4、aln等氮化物等。

[0090]

本说明书中的感应元件1除了具备图2的(a)、(b)所示的薄膜磁铁60以外,也可以在基板50上设置感应电路70。而且,感应元件1也可以只是感应电路70。

[0091]

(感应元件1的作用)

[0092]

接着,对感应元件1的作用进行说明。

[0093]

图3的(a)是说明在感应元件1的感应部71的长边方向(图2的(a)的x方向)上施加的磁场h与感应元件1的阻抗z之间的关系的图。在图3中,横轴是磁场h,纵轴是阻抗z。需要说明的是,阻抗z是在图2的(a)所示的感应电路70的端子部73a、73b间流过交流电流而测定的。因此,阻抗z是感应电路70的阻抗,但记作感应元件1的阻抗。

[0094]

如图3的(a)所示,感应元件1的阻抗z随着在感应部71的长边方向上施加的磁场h变大而变大。而且,在施加的磁场h小于感应部71的各向异性磁场hk的范围内,若使用阻抗z的变化量δz相对于磁场h的变化量δh而言急剧的部分(δz/δh大),则能够将磁场h的微弱的变化作为阻抗z的变化量δz提取出。在图3的(a)中,将δz/δh大的磁场h的中心表示为磁场hb。也就是说,能够高精度地测定磁场hb附近(图3中箭头所示的范围)的磁场h的变化量(δh)。在此,将阻抗z的变化量δz最急剧的(δz/δh最大)部分、即磁场hb中的每单位磁场的阻抗的变化量zmax与磁场hb中的阻抗z(记作阻抗zb。)的比值(zmax/zb)为灵敏度。灵敏度越高,则磁阻抗效应越大,越容易测量磁场或磁场的变化。并且,流过感应电路70的交流电流的频率越高,灵敏度越高。磁场hb有时被称为偏置磁场。以下,将磁场hb记作偏置磁场hb。

[0095]

感应元件1成为由图2的(b)所示的薄膜磁铁60预先施加了偏置磁场hb的状态。

[0096]

如果着眼于感应元件1作为1个阻抗元件,则能够进行上述说明,但感应元件1能够用电阻和电感串联连接而成的等效电路来表示,由于与电容元件组合形成rlc串联电路,所以在考虑其特性的基础上,需要考虑电阻r、电抗x、电感l的特性。

[0097]

图3的(b)是说明在感应元件1的感应部71的长边方向(图2的(a)的x方向)上施加的磁场h与感应元件1的电阻r之间的关系的图。在图3的(b)中,横轴是磁场h,纵轴是电阻r。

[0098]

图3的(c)是说明在感应元件1的感应部71的长边方向(图2的(a)的x方向)上施加的磁场h与感应元件1的电抗x之间的关系的图。在图3的(c)中,横轴是磁场h,纵轴是电抗x。

[0099]

图3的(d)是说明在感应元件1的感应部71的长边方向(图2的(a)的x方向)上施加的磁场h与感应元件1的电感l之间的关系的图。在图3的(d)中,横轴是磁场h,纵轴是电感l。

[0100]

在此,阻抗z、电阻r、电抗x、电感l具有下述关系。ω是角频率(rad/秒),f是频率(hz)。

[0101]

z=r+jx=r+jωlω=2πf

[0102]

在图3所示的感应元件中,电阻r、电抗x、电感l都与阻抗z相同,在磁场hb附近若磁场h增加,则上述各值也增加,变化变得最大。

[0103]

(磁传感器110)

[0104]

图4是说明应用第1实施方式的磁传感器110的图。图4的(a)是用逻辑符号表示的等效电路,图4的(b)是用晶体管表示的等效电路,图4的(c)是将图4的(b)变形后的等效电路。

[0105]

如图4的(a)所示,磁传感器110具备频率设定部10、和具备两个反相器inv1、inv2的电位供给部20。如上所述,在此说明频率设定部10中感应元件1和电容元件2串联连接的情况。下面,有时将感应元件1记作感应元件1(r)、感应元件1(rl)、电容元件2(c)。感应元件1(r)表示感应元件的等效电路仅为电阻r的情况,感应元件1(rl)表示感应元件的等效电路是电阻r和电感l的串联电路的情况。此外,在图4的(a)中,将感应元件1记作1(rl),将电容元件2记作2(c)。以下相同。需要说明的是,反相器inv1是第1反相器的一例,反相器inv2是第2反相器的一例。

[0106]

反相器inv1具备输入端子in1、输出端子out1。反相器inv2包括输入端in2和输出端out2。以下,将输入端子记作输入,将输出端子记作输出。

[0107]

反相器inv1、inv2是将输入信号的逻辑电平反转作为输出信号的元件。即,反相器inv1在对输入in1输入逻辑电平“h”时,从输出out1输出反转后的逻辑电平“l”,在对输入in1输入逻辑电平“l”时,从输出out1输出反转后的逻辑电平“h”。需要说明的是,在不分别区分反相器inv1、inv2的情况下,记作反相器inv。另外,有时将反相器inv的输出反转的情况记作开关。

[0108]

在此,将感应元件1(rl)的一个端子部73(例如,端子部73a(参照图2的(a)))与电容元件2(c)的一个端子连接的连接点设为α点,将感应元件1(rl)的另一个端子部73(例如,端子部73b(参照图2的(a)))设为β点,将电容元件2(c)的另一个端子设为γ点。需要说明的是,所谓端子,除了图2的(a)所示的为了连接布线而设置的焊盘状的端子之外,还包括设置在电路基板等上的搭载电容元件2的布线图案等。

[0109]

反相器inv1和inv2串联连接。也就是说,反相器inv1的输出out1与反相器inv2的输入in2连接。并且,频率设定部10的β点与反相器inv1的输出out1和反相器inv2的输入in2的连接点连接。也就是说,β点、输出out1以及输入in2是相同的电位。因此,有时记作β点(输出out1)、β点(输入in2)等,表示是相同的电位。并且,频率设定部10的α点与反相器inv1的输入in1连接,频率设定部10的γ点与反相器inv2的输出out2连接。也就是说,α点和反相器inv1的输入in1是相同的电位,γ点和反相器inv2的输出out2是相同的电位。因此,有时记作α点(输入in1)、γ点(输出out2),表示是相同的电位。

[0110]

在图4的(b)中,作为一例,将反相器inv1、inv2表示为cmos结构的反相器。在此,反相器inv1具有p沟道晶体管ptr1和n沟道晶体管ntr1。同样,反相器inv2具有p沟道晶体管ptr2和n沟道晶体管ntr2。并且,在反相器inv1中,晶体管ptr1的栅极与晶体管ntr1的栅极连接而成为输入in1。另外,晶体管ptr1的漏极和晶体管ntr1的漏极连接成为输出out1。同样,在反相器inv2中,晶体管ptr2的栅极与晶体管ntr2的栅极连接而成为输入in2。另外,晶体管ptr2的漏极和晶体管ntr2的漏极连接而成为输出out2。而且,向晶体管ntr1的源极和晶体管ntr2的源极供给作为基准电位的接地电位gnd,向晶体管ptr1的源极和晶体管ptr2

的源极供给电源电位v

cc

。在此,inv1、inv2各自的out1、out2输出的电压电平中,接地电位gnd为逻辑电平“l”,电源电位v

cc

为逻辑电平“h”。

[0111]

通过反相器inv1说明反相器inv1、inv2的动作。

[0112]

当反相器inv1的输入in1为接地电位gnd(逻辑电平“l”)时,晶体管ptr1导通,晶体管ntr1截止,输出out1变为电源电位v

cc

(逻辑电平“h”)。相反,当反相器inv1的输入in1为电源电位v

cc

(逻辑电平“h”)时,晶体管ptr1截止,晶体管ntr1导通,输出out1变为接地电位gnd(逻辑电平“l”)。并且,在输入in1从接地电位gnd侧超过阈值电压vth而向电源电位v

cc

侧转变时,在输入in1达到阈值电压vth的时刻,输出out1从电源电位v

cc

(逻辑电平“h”)反转为接地电位gnd(逻辑电平“l”)。相反,在输入in1从电源电位v

cc

侧低于阈值电压vth而向接地电位gnd侧转变时,在输入in1达到阈值电压vth的时刻,输出out1从接地电位gnd(逻辑电平“l”)反转为电源电位v

cc

(逻辑电平“h”)。

[0113]

在图4的(c)中,将图4的(b)的等效电路变形,使频率设定部10位于图的中央来表示。元件间的连接关系在图4的(b)和图4的(c)中相同。从图4的(c)可知,反相器inv1、inv2构成全桥。

[0114]

(磁传感器110的动作)

[0115]

首先,对频率设定部为rc串联电路的情况进行说明。

[0116]

图5是为了简化,针对感应元件1的等效电路仅为电阻r的情况,说明应用第1实施方式的磁传感器110的动作的时序图。为了简化,不考虑反相器的传播延迟时间,假定瞬时进行输出的反转来进行说明。图5的(a)是图4的(c)所示的磁传感器110的等效电路,图5的(b)是以接地电位gnd为基准的α点、β点以及γ点的各电位的时序图,图5的(c)是以γ点的电位为基准的α点、β点的各电位的时序图,图5的(d)是以α点的电位为基准的β点、γ点的各电位的时序图。需要说明的是,图5的(d)所示的以α点的电位为基准的β点的电位相当于施加在感应元件1(r)上的电压。需要说明的是,电位是指以接地电位gnd为基准的电压,电压是指2点间的电位差,但有时不区分电位和电压这两者。

[0117]

在图5的(b)、图5的(c)、图5的(d)中,横轴为时间,纵轴为电压。然后,在横轴上作为时刻t1~t6,按该顺序经过时间。在此,设接地电位gnd为“0v”,电源电位v

cc

为“5v”。在此,阈值电压vth为接地电位gnd(0v)和电源电位v

cc

(5v)之间的“2.5v”。

[0118]

在图5的(b)中,参照图5的(a)说明以接地电位gnd为基准的β点的电位、γ点的电位和α点的电位。

[0119]

在时刻t1,当α点(输入in1)从0v侧变为阈值电压vth(2.5v)时,反相器inv1反转,β点(输出out1)从5v转变到0v。由此,反相器inv2的β点(输入in2)从5v转变到0v,因此反相器inv2反转,γ点(输出out2)从0v转变到5v。在反相器inv1即将反转之前,α点为阈值电压vth(2.5v),并且γ点为0v。施加于电容元件2(c)的电压为α点与γ点的电位差,因此施加于电容元件2(c)的电压为2.5v。若瞬时进行反相器输出的反转,则电容元件2(c)不瞬时充放电,维持2.5v的电位差,因此若反相器inv2反转而γ点(输出out2)从0v转变到5v,则α点转变到对阈值电压vth(2.5v)加上5v而得的7.5v。

[0120]

然后,蓄积在电容元件2(c)中的电荷经由感应元件1(r)从7.5v的α点流向0v的β点。由此,α点的电位逐渐下降。该下降的过渡响应取决于时间常数τ,该时间常数τ取决于感应元件1的电阻r和电容元件2的电容c。在此,时间常数τ由τ=rc给出。由于时刻t1的电压是vcc

+阈值电压vth,所以从时刻t1经过t秒后的α点的电位v

(t)

成为v

(t)

=(v

cc

+vth)e

-t/τ

,电位从7.5v逐渐下降。

[0121]

然后,在时刻t2,当α点(输入in1)从7.5v下降而成为阈值电压vth时,反相器inv1反转而β点(输出out1)从0v转变到5v。由此,反相器inv2的β点(输入in2)从0v转变到5v,因此反相器inv2反转,γ点(输出out2)从5v转变到0v。在反相器inv1即将反转之前,α点为阈值电压vth(2.5v)。因此,当反相器inv2反转而γ点(输出out2)从5v转变到0v时,α点转变到从阈值电压vth(2.5v)减去5v而得的-2.5v。该上升的过渡响应也取决于时间常数τ。

[0122]

然后,电流从5v的β点向-2.5v的α点流动,使得电荷经由感应元件1(r)蓄积在电容元件2(c)中,从而α点的电位逐渐上升。

[0123]

然后,在时刻t3,当α点(输入in1)从-2.5v上升而成为阈值电压vth(2.5v)时,反相器inv1反转而β点(输出out1)从5v转变到0v。由此,反相器inv2的β点(输入in2)从5v转变到0v,因此反相器inv2反转,γ点(输出out2)从0v转变到5v。在反相器inv1即将反转之前,α点为阈值电压vth(2.5v)。因此,当反相器inv2反转而γ点(输出out2)转变到5v时,α点转变到在阈值电压vth(2.5v)加上5v而得的7.5v。也就是说,时刻t3与时刻t1相同。

[0124]

之后,反复进行从时刻t1到时刻t3的电位变化。

[0125]

在图5的(c)中,参照图5的(a),对以γ点为基准的α点的电压和β点的电压进行说明。需要说明的是,在图5的(c)中,用实线表示α点的电压,用虚线表示β点的电压。α点的电压及β点的电压分别根据图5的(b)中的α点的电位及β点的电位与γ点的电位之差而得到。

[0126]

以γ点为基准的α点的电压是指施加在电容元件2(c)上的电压。另外,以γ点为基准的β点的电压是指施加到频率设定部10的电压。

[0127]

β点在时刻t1从5v转变到-5v,在时刻t2从-5v转变到5v。然后,在时刻t3,与时刻t1同样地从5v转变到-5v。也就是说,β点与γ点的电位差始终为

±

5v。反相器inv1、inv2构成全桥,因此在频率设定部10中在反相器的输出反转时产生10v的电压变化。

[0128]

另一方面,α点在时刻t1成为阈值电压vth(2.5v),在时刻t2转变到向负侧偏移了阈值电压vth的电压(-2.5v),在时刻t3返回到阈值电压vth(2.5v)。

[0129]

因此,电容元件2(c)以

±

vth的电压反复进行充放电。

[0130]

并且,α点以及β点都重复从时刻t1到时刻t3的电压变化。

[0131]

在图5的(d)中,参照图5的(a),对以α点为基准的β点的电压以及γ点的电压进行说明。需要说明的是,在图5的(d)中,用实线表示β点的电压,用虚线表示γ点的电压。β点的电压及γ点的电压分别根据图5的(b)中的β点的电位及γ点的电位与α点的电位之差而得到。需要说明的是,由图5的(a)可知,β点的电压是施加在α点和β点之间,即感应元件1(r)上的电压。

[0132]

γ点是α点与γ点的电位差,因此,是使图5的(c)所示的α点的电压正负相反而得到的。

[0133]

β点在时刻t1从阈值电压vth(2.5v)转变到负侧的阈值电压vth(2.5v)和电源电位v

cc

(5v)相加而得的-7.5v。然后,从时刻t1到时刻t2,电压逐渐上升,在时刻t2,在负侧达到阈值电压vth(-2.5v)。并且,在时刻t2,从-2.5v转变到将阈值电压vth(2.5v)和电源电位v

cc

(5v)相加而得的7.5v。然后,从时刻t2到时刻t3,电压逐渐下降,在时刻t3达到阈值电压vth(2.5v)。并且,在时刻t3,从2.5v转变到负侧的阈值电压vth(2.5v)和电源电位v

cc

(5v)相

加而得的-7.5v。

[0134]

并且,β点反复进行从时刻t1到时刻t3的电压变化。

[0135]

如上所述,在感应元件1(r)上施加以从时刻t1到时刻t3的期间为1周期的交流电压,流过交流电流。交流电流的频率由感应元件1的电阻r和电容元件2的电容c决定。因此,将包含感应元件1的感应元件部11和包含电容元件2的电容元件部12统称并记作频率设定部10。而且,如图3所示,感应元件1的电阻r根据磁场h而变化。因此,通过频率测定部30测定流过磁传感器110的交流电流的频率或频率的变化,从而测量感应元件1所感应到的磁场或磁场的变化。也就是说,由反相器inv1、inv2构成的全桥构成为产生交流电流的振荡电路。

[0136]

接着,说明频率设定部是rlc串联电路的情况。

[0137]

在此,感应元件1(rl)的等效电路是电阻r和电感l的串联电路,并且与电容元件2(c)串联连接以形成rlc串联电路。对该情况下的应用第1实施方式的磁传感器110的动作进行说明。

[0138]

基本的动作与图5所示的频率设定部为rc串联电路的情况类似,但当加上电感l时,在已述的基于τ=rc的衰减上,加上基于ω=1/√lc的振动引起的延迟。在此,ω是lc电路的谐振角频率(rad/秒)。在c恒定的情况下,若l增加,则ω降低,因此振动周期变长。相应地,电压衰减到vth所需的时间延长,因此流过磁传感器110的交流电流的频率降低。

[0139]

这样,交流电流的频率由感应元件1的电阻r、电感l和电容元件2的电容c决定。而且,如图3所示,感应元件1的电阻r和电感l根据磁场h而变化。因此,通过频率测定部30测定流过磁传感器110的交流电流的频率或频率的变化,从而测量感应元件1所感应到的磁场或磁场的变化。

[0140]

需要说明的是,虽然说明了第1实施方式中的磁传感器110为基于rlc串联电路的张弛式振荡电路的情况,但是磁传感器110只要是频率根据由外部磁场引起的感应元件1的特性变化而变化的振荡电路,就能够使用各种各样的振荡电路。

[0141]

例如,可以使用lc振荡电路,该lc振荡电路利用感应元件的电感和电容元件形成lc谐振电路,并且利用lc谐振频率根据感应元件的电感因外部磁场的变化而发生变化这一情况。作为lc振荡电路的例子,可以举出考毕兹振荡电路。若使用感应元件1(rl)来代替lc振荡电路的电感l,则感应元件1(rl)的电感l根据外部磁场的变化而发生变化,因此振荡电路的频率发生变化。

[0142]

(频率测定部30的结构)

[0143]

如上所述,频率测定部30具备取得部31和频率确定部32。取得部31获取从磁传感器110输出的输出信号。该输出信号可以说是如下的交流电流,通过利用磁传感器110,该交流电流具有根据磁场强度决定的频率而振荡。

[0144]

需要说明的是,取得部31不仅能够直接利用从磁传感器110输出的输出信号,还能够进行规定的处理。例如,取得部31对从磁传感器110输出的输出信号进行成形,使其成为方形波。然后将其用作为输出信号。另外,作为规定的处理,取得部31优选对输出信号进行累计并平均化。由此,相位噪声降低,输出信号的频率的测定精度提高。

[0145]

需要说明的是,如果磁传感器110的输出信号的相位噪声少,频率稳定,则能够将磁传感器110的输出不经由取得部31而直接输出到频率确定部32。

[0146]

频率确定部32确定输出信号的频率。在本实施方式中,频率确定部32利用输出信

号和具有作为基准的频率的基准频率的基准信号彼此干扰这一情况,确定输出信号的频率。

[0147]

取得部31、频率确定部32通过硬件资源与软件协作来实现。作为硬件资源,可以举出后述的逻辑ic、混频器、d-触发电路、pc(personal computer)等计算机装置等。另外,作为软件,计算机装置内的未图示的cpu(未图示)将作为软件的程序加载到主存储器(未图示)中并执行,由此进行各种信号的处理。

[0148]

(频率确定部32的结构)

[0149]

接着,详细叙述频率确定部32的结构。

[0150]

以往,测定输出信号的振幅,根据测定的振幅算出磁场强度。这也可以说是测定输出信号的电压,根据测定出的电压算出磁场强度。在该情况下,难以检测出电压的细微变化,由此算出的磁场强度的精度也容易降低。例如,1ppm这样的差异相对于1v的电压而言为1μv,是被噪声掩盖的差异。另外,也有放大电压、放大其差的方法,但由于放大前产生的噪声也被放大,所以难以检测电压的变化。

[0151]

因此,在本实施方式中,通过测定输出信号的频率来解决该问题。这也可以被称为对输出信号进行时间测定。测定频率的细微变化比测定电压的情况更容易,由此算出的磁场强度的精度也容易提高。例如,1ppm这样差异在时间测定中是月差2.6秒的精度,并且在时间测定中是可检测的。

[0152]

但是,在输出信号的频率成为高频的情况下,在仅检测频率的变化的方法中,有时难以进行检测。在这种情况下,为了检测微小的频率变化,需要提高频率分辨率。即,需要提高时间分辨率,需要高速采样。另一方面,当输出信号的频率例如为100mhz以上时,难以进行以高分辨率测定其1个周期的高速采样。例如,在输出信号的频率为200mhz的情况下,1个周期为5n秒。此时的1ppm为5f秒,由于时间过短而难以测定。

[0153]

另一方面,即使输出信号的频率过低,也存在时间变动的磁场强度的时间分辨率降低的问题。例如,在1hz的信号频率下无法表现以1hz的周期变动的磁场强度的波形。在以100点/周期表现以1hz的周期变动的磁场强度的情况下,需要10m秒的时间分辨率。为此,需要在10m秒的期间准确地读取信号频率,但若信号频率为1hz,则需要从1周期的1/100的波形读取信号频率,难以准确地测定。因此,需要变换为能够检测微小的频率变化,并且能够充分提高磁场强度变动的时间分辨率的适当的频率。

[0154]

为了解决该问题,例如,如果对输出信号的频率进行分频,则可以变换为低频,规定的采样速度下的频率分辨率提高。另一方面,在该方法中,由于频率的变化量也一起降低,所以频率的变化率不会提高。

[0155]

例如,在检测200mhz的频率的1ppm差异的情况下,如果分频为1/1000000,则1ppm的时间变化为5n秒,能够测定。但是,由于输出信号的频率也变为1/1000000,所以200mhz的输出信号变为2hz,磁场信号检测的时间分辨率降低。因此,需要尽可能不改变频率的变化量地降低频率,来提高频率的变化率的方法。

[0156]

因此,在本实施方式中,在对输出信号的频率进行测定时,如以下说明那样,利用输出信号与具有作为基准的频率的基准频率的基准信号之间的干扰来进行时间测定,由此实现该问题的解决。

[0157]

[第1实施方式]

[0158]

首先,对第1实施方式进行说明。在第1实施方式中,频率确定部32根据基于输出信号与基准信号的干扰结果、即输出信号与基准信号的相位差而得到的波形,确定输出信号的频率。

[0159]

在此,首先说明通过逻辑运算使输出信号与基准信号干扰的情况。

[0160]

图6是使用逻辑运算使输出信号和基准信号干扰的电路结构的概念图。

[0161]

图示的电路结构具备输出基准信号的基准信号输出部311、对由磁传感器110振荡的输出信号进行分频的输出信号分频部312、对从基准信号输出部311输出的基准信号进行分频的基准信号分频部313、进行逻辑运算的逻辑运算部314、生成三角波的三角波生成部315、进行a/d转换的a/d转换部316、求出三角波的频率的信号处理部317、以及输出频率的输出部318。

[0162]

基准信号输出部311输出预定频率的基准信号。在此,来自磁传感器110的输出信号由取得部31预先变换为方形波。然后,基准信号输出部311输出预定频率的方形波作为基准信号。基准信号输出部311优选具有与输出信号的频率比较接近的频率。因此,基准信号的频率不限于一种,准备具有多个频率的基准信号。具有多个频率的基准信号能够在基准信号分频部313中通过基准信号的分频而生成。

[0163]

输出信号分频部312根据需要对输出信号进行分频。如果进行分频,则相位噪声被累计平均化而降低,但磁场检测的时间分辨率也降低,所以优选抑制为能够降低到能够由逻辑运算部314准确地处理的相位噪声的最低限度的分频比。另外,基准信号分频部313根据需要对基准信号进行分频。输出信号分频部312和基准信号分频部313可以由二进制计数器或预分频器构成。另外,也可以为由时钟发生器等的pll(phase locked loop:相位同步电路)使基准信号输出部311和基准信号分频部313一体化的结构。

[0164]

逻辑运算部314对由输出信号分频单元312分频后的输出信号和由基准信号分频单元313分频后的基准信号进行逻辑运算。这些信号是方形波,将脉冲为on时设为1,将脉冲为off时设为0来进行逻辑运算。逻辑运算没有特别限定,可以使用xor(异或)、nor(或非)、nand(不与)、or(或)、and(与)中的任一种。逻辑运算部314例如可以由逻辑ic构成。另外,也可以使用pll的相位比较器。

[0165]

三角波生成部315根据由逻辑运算部314输出的波形,生成三角波。

[0166]

图7的(a)~(e)是示出逻辑运算部314和三角波生成部315的动作的图。

[0167]

其中,图7的(a)表示将输出信号和基准信号的方形波重叠的情况。在此,输出信号用虚线表示,基准信号用实线表示。

[0168]

而且,图7的(b)表示通过逻辑运算部314进行输出信号和基准信号的逻辑运算,其结果输出的波形。在此,逻辑运算部314通过xor(异或)进行逻辑运算。

[0169]

图7的(c)是图7的(a)、(b)的区域r1的放大图,图7的(d)是图7的(a)、(b)的区域r2的放大图。

[0170]

如图7的(c)的上侧所示,在区域r1中,输出信号的波形和基准信号的波形大致一致。这可以说是两者间的相位大致一致的状态。此时,如果逻辑运算部314通过xor(异或)进行逻辑运算,则在输出信号和基准信号的其中一个为on、另一个为off的情况下,得到成为on的波形。其结果,如图7的(c)的下侧所示,得到on的时间短的方形波。

[0171]

此外,如图7的(d)的上侧所示,在区域r2中,输出信号的波形和基准信号的波形发

生偏移。这可以说是两者间的相位错开的状态。此时,当逻辑运算部314通过xor(异或)进行逻辑运算时,如上所述,在输出信号和基准信号的其中一个为on、另一个为off的情况下,得到成为on的波形。其结果,如图7的(d)的下侧所示,得到on的时间比较长的方形波。

[0172]

也就是说,关于逻辑运算部314通过xor(异或)所生成的波形,输出信号和基准信号的相位越一致,就成为具有越短的脉冲宽度的方形波,越偏离就成为具有越长的脉冲宽度的方形波。即,得到pwm(脉冲宽度调制)输出。

[0173]

然后,三角波生成部315将如图7的(c)、(d)那样生成的方形波的波形相对于时间进行平均化。可以考虑三角波生成部315为lpf(low-passfilter:低通滤波器)。即,将pwm输出变换为三角波。其结果,得到图7的(c)、(d)的粗线所示的波形。也就是说,在图7的(c)的情况下,由于是具有短脉冲宽度的方形波,所以在将该波形相对于时间平均化的情况下,其电压电平低。另一方面,在图7的(d)的情况下,由于是具有长脉冲宽度的方形波,所以在将该波形相对于时间平均化的情况下,其电压电平变高。

[0174]

并且,在将其应用于图7的(b)的情况那样的更长时间的情况下,得到图7的(b)的粗线所示的三角波ws1。

[0175]

该三角波ws1的频率取决于输出信号的频率与基准频率的偏移量。也就是说,输出信号的频率与基准信号的频率越一致,则周期越长。即,三角波ws1的频率变得更小。相对于此,输出信号的频率与基准信号的频率越偏离,差异越大,则周期越短。即,三角波ws1的频率变得更大。

[0176]

三角波ws1的频率由输出信号的频率与基准信号的频率之差的绝对值表示。

[0177]

因此,根据三角波ws1的频率,可知输入到逻辑运算部314的输出信号分频部312的频率与基准信号分频部313的输出的频率之差,进而根据输出信号分频部312与基准信号分频部313的分频比,可知输出信号的频率与基准信号的频率之差。由于基准信号的频率是预先确定的,所以从该差可知输出信号的频率。另一方面,由于三角波ws1的频率由输出信号的频率与基准信号的频率之差的绝对值表示,所以因外部磁场而发生了微小变化的输出信号的频率的变化量被原样维持。三角波ws1维持输出信号的频率的变化量,并且频率降低,因此频率变化率增加。因此,能够测定由外部磁场引起的微小的频率差。

[0178]

需要说明的是,图7的(e)表示在输出信号的频率与基准信号的频率的偏移量比图7的(b)大的情况下生成的三角波ws2。该三角波ws2的周期比三角波ws1短。

[0179]

三角波ws1、ws2的频率低于输出信号的频率。因此,与直接检测输出信号的频率相比,检测三角波ws1、ws2的频率以更低的采样速度就足够了。即,通过检测三角波ws1、ws2的频率,即使不进行高速采样,也可以知道输出信号的频率。

[0180]

在该情况下,频率确定部32根据输出信号与基准信号的干扰结果,使输出信号的频率成为低频并且使变化率增大,通过使用成为低频、大变化率的输出信号来确定输出信号的频率。

[0181]

返回图6,a/d转换部316进行a/d转换,将由三角波生成部315生成的三角波转换为数字信号。a/d转换部316例如是a/d转换器。

[0182]

然后,信号处理部317求出三角波的频率,根据三角波的频率求出输出信号的频率。这可以通过例如fft(fast fourier transform:快速傅立叶变换)来进行。fft例如可以通过向pc取入由a/d变换部316变换后的数字信号,并执行进行fft处理的规定程序来进行。

[0183]

此外,不限于fft,也可以使用测量三角波的1个周期所花费的时间的方法、对规定时间内的三角波的周期数进行计数的方法等各种方法。

[0184]

需要说明的是,在由输出信号分频部312对输出信号进行分频的情况下,根据分频比n进行频率校正。

[0185]

输出部318将求出的输出信号的频率输出到磁场算出部40。

[0186]

在上述的例子中,逻辑运算部314不仅使用逻辑ic,还使用pll(phase locked loop)ic的相位比较器(pfc:phase frequency comparator),从而能够实现同样的功能。即,向相位比较器输入由输出信号分频部312分频后的输出信号和由基准信号分频部313分频后的基准信号。在相位比较器中,比较两者的相位,检测数字锁(digital lock)。这是因为,在两者的相位差例如在15n秒以内连续3次检测出的情况下,检测出数字锁,另外,在两者的相位差例如为30n秒以上的情况下,解除数字锁。然后,使用检测到数字锁时的相位比较器的误差信号脉冲。该误差信号脉冲例如为图7的(b)、(e)所示的脉冲。

[0187]

[第2实施方式]

[0188]

接着,对第2实施方式进行说明。在第2实施方式中,频率确定部32通过对输出信号和基准信号进行混频来进行干扰,并通过超外差方式对输出信号的频率进行变换。

[0189]

图8是使用超外差方式对输出信号和基准信号进行混频的电路结构的概念图。

[0190]

图示的电路结构包括输出基准信号的基准信号输出部321、对输出信号和基准信号进行混频的混频部322、进行a/d转换的a/d转换部323、求出三角波的频率的信号处理部324、以及输出频率的输出部325。

[0191]

基准信号输出部321输出预定频率的基准信号。基准信号例如由时钟发生器生成。然后,输出具有方形波的时钟信号作为基准信号。

[0192]

混频部322对输出信号和基准信号进行混频。因此,混频部322生成具有中频的混频信号,该中频作为输出信号的频率与基准信号的频率之差。中频的频率低于输出信号的频率。即,通过混频部322的混频,使输出信号和基准信号干扰,使输出信号成为低频。即,通过超外差方式,使输出信号成为低频。例如,在输出信号的频率为100mhz、基准信号的频率为99.9mhz的情况下,中频为100khz。

[0193]

进行a/d变换的a/d变换部323、求出ad变换后的波形的频率的信号处理部324、输出频率的输出部325与图6的a/d变换部316、信号处理部317、输出部318相同。另外,也可以在数字输入端口直接取入ad转换前的波形,作为数字信号在信号处理部324中进行处理。在该情况下,不需要a/d转换部323。

[0194]

这样得到的磁场信号能够通过超外差方式的干扰来维持变化量并降低频率,因此能够转换成适合于检测的频率并增大频率变化率,因此能够进行微小磁场信号的高灵敏度测定。

[0195]

[第3实施方式]

[0196]

接着,对第3实施方式进行说明。在第3实施方式中,频率确定部32利用在输出信号与基准信号之间产生的混叠来确定输出信号的频率。

[0197]

图9是利用混叠来确定输出信号的频率的电路结构的概念图。

[0198]

图示的电路结构具备输出基准信号的基准信号输出部331、使输出信号与基准信号干扰而产生混叠的干扰部332、求出通过混叠观测的波形的频率的信号处理部333、以及

输出频率的输出部334。

[0199]

基准信号输出部331输出预定频率的基准信号。基准信号例如由时钟发生器生成。然后,输出具有方形波的时钟信号作为基准信号。

[0200]

需要说明的是,与第1实施方式相同,也可以设置分频部,预先对输出信号和基准信号中的至少一者进行分频。

[0201]

干扰部332使输出信号与基准信号干扰。干扰部332例如是d-触发器。

[0202]

图10的(a)~(e)是以模拟信号的正弦波的采样为例,表示混叠的概念的图。

[0203]

在此,示出了对正弦波信号进行采样时所观测到的频率。在图10的(a)~(e)中,实线表示信号,实线上的点表示对信号进行采样的位置。此外,虚线表示作为采样结果观察到的信号。

[0204]

其中,图10的(a)表示与信号的频率相比采样的频率足够大的情况。在这种情况下,可以通过采样的值来测量信号的波形。

[0205]

另外,图10的(b)、(c)表示信号的频率比图10的(a)的情况大,接近采样频率的情况。其中,是采样数大于信号频率的2倍的情况。在这种情况下,不能准确地再现波形。

[0206]

进而,图10的(d)表示与图10的(b)、(c)的情况相比,信号的频率进一步变大,采样频率正好成为信号频率的2倍的情况。此时所采样的值成为恒定,所采样的波形不表示信号频率。

[0207]

而且,图10的(e)表示与图10的(d)的情况相比信号的频率进一步变大的情况,即采样频率小于信号频率的2倍的情况。其结果,观测到由于干扰而实际上不存在的频率的波形(混叠)。

[0208]

如图10的(e)所示,混叠在信号频率大于采样频率的1/2的情况下产生,通过混叠观测到的波形的频率是信号频率与采样频率之差。这也可以说是(观测的频率的绝对值)=(信号的频率)-(采样的频率)。也就是说,如果知道通过混叠观测的波形的频率,则知道信号的频率。

[0209]

需要说明的是,在此使信号的频率变化,但实际上,干扰部332使采样的频率变化而产生混叠。即,使作为基准信号的时钟信号的频率变化。在这种情况下,可以说干扰部332通过改变作为基准信号的输出信号的采样频率来执行干扰。

[0210]

为了理解混叠的概念,以正弦波的模拟信号进行了说明,但由于在数字信号中也产生同样的混叠,所以能够用于微小的频率变化的测定。

[0211]

图11的(a)~(e)是以数字信号的采样为例,表示在第3实施方式中使用的混叠的概念的图。

[0212]

在此,示出了对数字信号进行采样时所观测到的频率。在图11的(a)~(e)中,实线表示输入到干扰部的数字信号和从干扰部输出的数字信号。

[0213]

在图11中,说明磁传感器110的输出信号相对于基准信号输出部331的基准信号而言为不产生混叠的频率的情况和产生混叠的频率的情况这2种情况下的动作。

[0214]

图11的(a)、(b)、(c)表示磁传感器110的输出信号相对于基准信号输出部331的基准信号而言为不产生混叠的频率的情况的例子,图11的(a)、(d)、(e)表示磁传感器110的输出信号相对于基准信号输出部331的基准信号而言为产生混叠的频率的情况的例子。

[0215]

图11的(a)是基准信号输出部331的基准信号的数字波形。

[0216]

图11的(b)是磁传感器110的输出信号相对于基准信号输出部331的基准信号而言为不产生混叠的频率的情况下的例子中的磁传感器110的输出信号的数字波形。

[0217]

图11的(c)是磁传感器110的输出信号相对于基准信号输出部331的基准信号而言为不产生混叠的频率的情况下的例子中的干扰部332的输出信号的数字波形。

[0218]

图11的(d)是磁传感器110的输出信号相对于基准信号输出部331的基准信号而言为产生混叠的频率的情况下的例子中的磁传感器110的输出信号的数字波形。

[0219]

图11的(e)是磁传感器110的输出信号相对于基准信号输出部331的基准信号为产生混叠的频率的情况下的例子中的干扰部332的输出信号的数字波形。

[0220]

首先,对磁传感器110的输出信号相对于基准信号输出部331的基准信号而言为不产生混叠的频率的情况的例子进行说明。

[0221]

干扰部332是d-触发器。d-触发器输入输出数字信号。即,输入输出逻辑电平“h”和逻辑电平“l”的信号。

[0222]

在此,使用具有clk端子、d端子、q端子这3个端子的d-触发器。clk端子是基准信号的输入端子。d-触发器存储在基准信号上升的瞬间向d端子的输入。d端子是将磁传感器110的输出信号输入到d-触发器的端子。q端子是输出d-触发器所存储的逻辑电平的状态的端子。

[0223]

图11的(a)所示的基准信号从基准信号输出部331输出,输入到干扰部332所示的d-触发器的clk端子。图11的(b)所示的磁传感器110的输出信号被输入到d-触发器的d端子。基准信号上升的瞬间的磁传感器110的输出信号存储在d-触发器中,其逻辑电平的状态从q端子输出,输出图11的(c)所示的数字波形。

[0224]

图11(abc放大)的箭头表示(a)的基准信号上升,(b)的磁传感器110的输出信号存储在d-触发器中,其逻辑电平的状态作为(c)的输出波形从q端子输出的定时。仅在该定时,(c)的输出信号的逻辑电平可发生变化。

[0225]

在箭头(1)中,由于(b)的逻辑电平为“h”,所以(c)的输出的逻辑电平为“h”。在从箭头(1)到箭头(2)的期间,(b)的逻辑电平从“h”反转为“l”,但在(b)反转的瞬间,由于在d-触发器中还没有存储(b)的逻辑电平,所以(c)的逻辑电平仍为“h”。然后,在箭头(2)的定时,(b)的逻辑电平存储在d-触发器中,(c)的逻辑电平反转为“l”。以后,在箭头(3)、箭头(4)的定时,(b)的逻辑电平存储在d-触发器中,但由于(b)的逻辑电平保持“l”不变,所以(c)的逻辑电平保持“l”不变。这样,在磁传感器110的输出信号为小于基准信号输出部331的基准信号的1/2的频率且不产生混叠的情况下,(b)和(c)成为大致相同的频率。相应于(b)的逻辑电平的变化与(a)的基准信号的上升的定时错开的量,(b)和(c)的逻辑电平反转的定时错开,(c)的输出信号的占空比偏离50%。因此,在不产生混叠的条件下,若使磁传感器110的输出信号的频率成为相对于基准信号输出部331的基准信号的频率而言足够小的频率,则能够准确地测定频率。但是,由于不发生混叠引起的干扰,所以磁传感器110的输出信号微小变化时的频率变化率直接成为d-触发器的频率变化率,不发生变化率的放大。

[0226]

接着,说明磁传感器110的输出信号是相对于基准信号输出部331的基准信号而言发生混叠的频率的情况下的例子。

[0227]

图11的(a)所示的基准信号从基准信号输出部331输出,输入到干扰部332所示的d-触发器的clk端子。图11的(d)所示的磁传感器110的输出信号被输入到d-触发器的d端

子。基准信号上升瞬间的磁传感器110的输出信号存储在d-触发器中,其逻辑电平的状态从q端子输出,输出图11的(e)所示的数字波形。

[0228]

图11(ade放大)的箭头表示(a)的基准信号上升,(d)的磁传感器110的输出信号存储在d-触发器中,其逻辑电平的状态作为(e)的输出波形从q端子输出的定时。仅在该定时,(e)的输出信号的逻辑电平可发生变化。

[0229]

在箭头(1)中,由于(d)的逻辑电平为“l”,所以(e)的输出的逻辑电平为“l”。在从箭头(1)到箭头(2)的期间,(d)的逻辑电平从“l”反转为“h”,但在(d)反转的瞬间,由于在d-触发器中还没有存储(d)的逻辑电平,所以(e)的逻辑电平仍为“l”。

[0230]

然后,在箭头(2)的定时,(d)的逻辑电平存储在d-触发器中,(e)的逻辑电平反转为“h”。

[0231]

在从箭头(2)到箭头(3)的期间,(d)的逻辑电平从“h”反转为“l”之后,进一步反转为“h”,但在读取该期间的“l”的逻辑状态的定时,(a)的基准信号没有上升,所以不存储在d-触发器中。由于在箭头(3)中存储在d-触发器中的状态是与在箭头(2)中存储的“h”相同的“h”的逻辑电平,所以(e)的逻辑电平的输出维持“h”。进而,由于在箭头(4)、箭头(5)的定时重复相同的动作,所以(e)的逻辑电平的输出持续维持“h”。(a)的频率比(d)的频率稍高,所以在箭头(2)~箭头(5)的定时,(d)的逻辑电平都保持“h”,但其间(a)和(d)的相位一点一点地继续偏移。

[0232]

然后,当(a)和(d)超过同相位时,这次(a)的逻辑电平上升的定时的(d)的逻辑电平变为“l”,(e)的逻辑电平反转为“l”。之后,(a)的逻辑电平上升瞬间的(d)的逻辑电平维持“l”不变,但其间(a)和(d)的相位一点一点地持续偏移,当(a)和(d)超过反相位时,(a)的逻辑电平再次上升的定时的(d)的逻辑电平变为“h”,(e)的逻辑电平的输出反转为“h”。

[0233]

这样,在(d)的频率为从超过(a)的频率的1/2的频率到不超过基准信号的2倍的频率的范围的情况下,产生混叠。通过(a)和(d)的信号干扰来确定(e)的信号的输出,其频率成为(a)和(d)之差的频率的绝对值。因此,(e)相对于(d)而言低频化,(a)和(d)的频率差越小,则(e)的频率越低。另外,由于外部磁场的变化,磁传感器110的输出信号的频率稍微变化,在(d)的频率中产生微小变化的情况下,由于(a)的频率恒定,所以在作为(a)和(d)之差的绝对值的(e)中维持与(d)同样的频率之差。(e)相对于(d)而言频率降低,维持频率的变化量,因此频率的变化率增大。

[0234]

相应于(d)的逻辑电平的变化与(a)的基准信号的上升沿的定时偏移的量,(e)的逻辑电平的反转的定时从(a)和(d)的干扰定时错开,(e)的输出信号的占空比偏离50%。因此,在产生混叠的条件下,若使磁传感器110的输出信号的频率成为尽可能接近基准信号输出部331的基准信号的频率的频率,则能够准确地测定频率。

[0235]

但是,当频率过于接近时,混叠引起的干扰频率过于低,因此磁场信号检测的时间分辨率降低。另外,当频率过于接近时,由于磁传感器110的输出信号的频率的抖动,存在不能得到稳定的干扰信号的问题。

[0236]

因此,优选磁传感器110的输出信号的频率与基准信号输出部331的基准信号的频率之差在满足磁场信号检测的时间分辨率且能够得到稳定的干扰信号的范围内尽可能小。

[0237]

信号处理部333求出通过混叠观测的波形的频率,并基于求出的频率而求出输出信号的频率。这与第1实施方式相同,例如可以通过fft来进行。此外,并不限于fft,与第1实

施方式同样,可以使用测量干扰部332输出的1个周期所花费的时间的方法、对规定时间内的干扰部332输出的周期数进行计数的方法等各种方法。

[0238]

[第4实施方式]

[0239]

接着,对第4实施方式进行说明。基本动作与第3实施方式相同,利用在输出信号与基准信号之间产生的混叠来确定输出信号的频率。

[0240]

电路结构也与图9相同,但干扰部332利用数字输入端口的数字信号采样功能。

[0241]

通常,以规定或任意设定的采样频率对数字输入端口进行采样。采用与第3实施方式的图11中说明的构成相同的构成进行动作,在采样频率的定时对输入数据进行采样。

[0242]

因此,即使不设置干扰部332,如果磁传感器110的输出信号的频率和采样频率是产生混叠的频率差,则两者干扰而引起混叠,产生输入信号的低频化,变化率增大。

[0243]

为了成为引起混叠的频率差,只要对磁传感器110的输出信号进行分频,调整为数字输入端口的采样频率附近即可。

[0244]

另外,即使将数字输入端口的采样频率设定为磁传感器110的输出频率附近,也能够得到同样的效果。

[0245]

另外,也可以对磁传感器110的输出频率进行分频,并且设定数字输入端口的采样频率,以成为规定的频率。

[0246]

由数字输入端口采样的信号在信号处理部333中变换为频率后,变换为信号磁场,从输出部334输出。

[0247]

第4实施方式不需要干扰部332,所以可以使装置紧凑,另外,由于可以实现低成本化,所以适合于构成同时测量多通道的系统。

[0248]

为了确认该实施方式的性能,使用时钟发生器代替图9的磁传感器110进行了动作确认。时钟发生器由pll构成,以晶体振荡器的准确的时钟为基准生成输出频率。调整输入分频部、电压控制振荡器(vco)、输出分频部的设定,输出输出频率为270mhz~299.9997mhz的各种频率。

[0249]

时钟发生器的输出信号由fpga采样,进行数据处理而输出。fpga具备基准信号输出部331、干扰部332、信号处理部333、输出部334的各功能。基准信号输出部331的功能通过在fpga内的pll中生成采样频率来实现。采样频率设定为300mhz。干扰部332通过利用数字输入端口对输入信号进行采样来实现。由于数字输入端口以由pll生成的采样频率对输入信号进行采样,所以当输入信号成为接近采样频率的频率时,产生混叠,测量两者之差的频率的数字信号。

[0250]

频率的测量是通过对由数字输入端口测量的数字信号的上升沿间(相当于所测量的频率的1个周期)的采样时钟数进行计数来进行的。例如,在所测量的频率为100khz的情况下,所测量的频率的上升沿之间的时间为10μ秒,在此期间,300mhz的采样时钟被计数3000次。所计数的数值通过在fpga中编程的数值运算而被转换为频率,进而,考虑到混叠而被转换为输入信号的频率(信号处理部333的功能)。该值作为图表或值显示在显示器上,并且被写入外部存储装置(输出部334的功能)。需要说明的是,在这种情况下,可以说干扰部332使用数字信号输入端口的采样时钟信号进行干扰。

[0251]

图12的(a)是在将输入信号的频率改变为270mhz~299.9997mhz的情况下利用上述方法测量出的频率及其偏差。

[0252]“采样频率”是由fpga的pll设定的数字输入端口的采样频率,“输入频率”是从时钟发生器输入到fpga的数字输入端口的信号的频率,“δ”是“采样频率”与“输入频率”之差。

[0253]“测量到的频率”是通过fpga的数字输入端口中的混叠进行低频化而测量出的频率,“转换后”是根据“采样频率”和“测量到的频率”之差计算而求出的输入频率,“误差”是根据“输入频率”和“转换后”之差计算出的测定误差(hz),以及将其除以“输入频率”而求出的比例(ppm),“频率偏差”是将“测量到的频率”的标准偏差除以“输入频率”而得到的值。

[0254]“变换后”的频率成为与“输入频率”大致相同的值,在第4实施方式中,表示能够按照理论准确地测定频率。

[0255]

图12的(b)是上述测量中的输出频率的误差(实线)和偏差(虚线)的曲线图。如果采样频率与输入频率之差小,则频率误差以及频率的偏差变小,因此表示能够准确地测定微小频率差。

[0256]

在上述第1实施方式~第4实施方式中,作为输出信号与基准信号的干扰结果,频率确定部32使输出信号的频率成为低频。这是基于输出信号与基准信号的相位差的频率。然后,通过使用成为低频的输出信号来确定输出信号的频率。由此,即使在从磁传感器110输出的输出信号为100mhz以上的高频信号的情况下,通过成为低频,也能够在通常的采样速度下得到充分的频率分辨率。并且,频率的测定精度不易降低,能够更准确地测定磁场的强度。另外,在该方法中,由于频率变化量不降低,频率变化率提高,因此能够进行磁场的高灵敏度的测定。此外,即使在使用分频的情况下,分频比也比以往小,所以也难以产生频率变化量降低的问题。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1