一种基于ATE的SIP芯片内部互连测试方法

一种基于ate的sip芯片内部互连测试方法

技术领域

1.本发明涉及系统级封装(system in package,sip)芯片测试技术领域,特别是一种基于ate的sip芯片内部互连测试方法。

背景技术:

2.近年来,随着纳米级集成电路制造技术的不断突破,摩尔定律发展到达一定瓶颈,sip技术为解决这一难题提供了全新的设计思路。将多个未经封装的裸芯片和电阻电容等无源器件通过sip技术立体集成在一个小型系统中,从而形成具有特定功能的sip芯片。然而,基于sip芯片的先进封装技术不断发展以及soc裸芯制造工艺的不断缩小,使得sip芯片内部的器件密度不断增大,器件种类不断丰富,内部互连线密度不断提升,对sip芯片的测试内部互连提出了更高的要求。

3.20世纪90年代欧美联合测试工作组(joint test action group,简称jtag)首次把边界扫描测试技术的概念引入芯片测试,并最终形成ieee 1149.1标准,得到业界认可。经过几十年的探索研究,jtag测试技术不断推陈出新,形成针对混合信号测试的ieee 1149.4标准,针对高级数字网络的ieee 1149.6标准,针对soc芯片的ieee 1500标准,针对可编程器件在线配置的ieee1532标准等。针对sip芯片的测试,2019年国际电气与电子工程师协会推出ieee 1838标准,该标准在ieee 1149.1和ieee 1500的基础上发展而来,主要用于复杂sip芯片dft电路设计。ieee1838在解决垂直堆叠(例如2.5d、3d)芯片之间的互操作性和可测性问题上给出了理论指导,目前业内还没成熟的兼容ieee 1838的产品出现。当前运用较为成熟和普遍的是基于ieee 1149标准的jtag测试技术,已广泛应用于单芯片、单板系统、多芯片系统模块等电子产品的测试领域,在解决互连测试方面具备坚实的技术基础。

4.在dft技术发展的基础上,针对复杂电子系统的互连测试方案应运而生。国外temento systems公司基于ieee 1149.1标准开发的diatem测试系统专门针对复杂板级数字电路系统进行全面的互连测试。diatem系统预留4个jtag接口,可同时对多扫描链系统进行互连测试。与国外相比,国内针对多芯粒异构sip芯片也进行了测试技术研究,形成了一系列的测试方法,例如,无锡中微腾芯电子有限公司提出了一种用于3d-sip芯片测试向量压缩的方法,建立了3d-sip芯片测试装置及系统,发明了多层堆叠的3d-sip芯片测试法,并形成了相关的测试软件;中国电子科技集团公司第五十八研究所提出了一种基于jtag接口的多芯粒异构sip芯片测试调试技术;西安电子科技大学提出了基于多芯粒异构sip芯片的高速芯片协同测试;天津科技大学提出基于嵌入式技术的多芯粒异构sip芯片专用测试平台研究;中国航天科技集团公司第一研究院提出基于jtag测试技术的多芯粒异构sip芯片测试技术研究;航空工业西安航空计算技术研究所提出了siphky2101a的测试方法研究与测试板设计。

5.通过上述内容可以看出,国外针对jtag总线测试技术研究已经较为成熟,国内在jtag总线控制器方面也形成一定的成果。但是,这些成果主要应用于板级系统,普遍采用jtag总线控制器完成待测对象的测试控制。针对sip芯片在量产阶段的测试研究较少,并且

从现有的复杂sip微系统芯片测试技术来看,普遍采用功能测试的方式进行测试。功能测试的方法须通过ate系统完成复杂的功能码流加载,并且对于一些复杂接口(如emif、pcie、srio等)很难完成与ate系统协同完成功能验证;其次在功能测试发生故障时很难进行准确的故障定位。急需研究一套专用于的sip芯片量产阶段的内部互连测试方法。

6.在sip芯片内部以及dib板外围未进行jtag总线控制器设计时,ate测试系统需完成jtag总线测试时序的收发。然而在ate系统手工编写jtag总线测试向量较为复杂,急需寻求新的方法生成jtag总线测试向量。

技术实现要素:

7.本发明的目的在于克服现有技术的不足,提供一种基于ate的sip芯片内部互连测试方法。

8.本发明的目的是通过以下技术方案来实现的:

9.一种基于ate的sip芯片内部互连测试方法,所述测试方法包括如下步骤:

10.步骤s1、svf编写互连测试程序;

11.步骤s2、将编写好的svf程序解析成模式捕获格式文件;

12.步骤s3、将模式捕获格式文件中符合jtag总线时序的向量进行处理;

13.步骤s4、将获得的测试时序移植到ate测试系统中,根据sip芯片中互联模型的具体形式进行互连测试。

14.进一步地,在所述步骤s4中,sip芯片中的互连模型包括逻辑簇互连模型、存储器互连模型、ate协同互连模型、扫描链互连模型和ate直连模型。

15.进一步地,在采用逻辑簇互连模型或存储器互连模型的情况下,nbs器件的所有io端口被扫描链路环绕,将与nbs器件输入端相连的边界扫描单元设置为输入模式,输出端口相连的边界扫描单元设置为采样模式,采用extest测试指令进行测试。

16.进一步地,具体测试步骤如下:

17.步骤s411:指令寄存器发送extest测试指令;

18.步骤s412:通过与nbs输入端相连的边界扫描单元向nbs输入端口发送一个周期的测试激励;

19.步骤s413:与nbs输出端口相连的边界扫描单元接收第一个测试周期的测试响应与期望值进行分析,同时输入端的边界扫描单元继续发送第二周期的测试激励;

20.重复步骤s413即可完成测试。

21.进一步地,在采用ate协同互连模型的情况下,nbs电路被扫描链路环绕,输入端口与边界扫描链路相连,输出端口与ate系统直接相连。

22.进一步地,具体测试步骤如下:

23.步骤s421:指令寄存器发送预装指令;

24.步骤s422:通过tdi引脚向与nbs器件相连的边界扫描单元发送第一次测试矢量,此时第一次测试激励还没有作用于nbs器件的输入端口;

25.步骤s423:指令寄存器加载外测试指令,此时预装指令发送的第一次测试激励作用于nbs器件的输入端;

26.步骤s424:ate端接收nbs器件的第一次测试响应,与期望值比对,同时tdi端口发

送第二次测试激励;

27.重复执行步骤s424即可完成对nbs器件所有周期的测试向量验证。

28.进一步地,在采用扫描链互连模型的情况下,以半数网络端口为输入端、半数网络端口为输出端,通过边界扫描单元完成输入端数据的设置以及输出端数据的读取。

29.进一步地,具体测试步骤如下:

30.步骤s431:指令寄存器发送预装指令;

31.步骤s432:通过tdi引脚向bs1器件的边界扫描单元发送第一次测试矢量;

32.步骤s433:指令寄存器加载外测试指令;

33.步骤s434:bs2器件端边界扫描单元接收第一次测试响应,与期望值比对,同时tdi端口发送第二次测试激励;

34.重复执行步骤s434即可完成测试。

35.进一步地,在采用ate直连模型的情况下,bs器件的边界扫描单元引脚与ate系统的数字通道直接相连。

36.进一步地,具体测试步骤如下:

37.步骤s441:指令寄存器发送预装指令;

38.步骤s442:通过tdi引脚向与bs器件相连的边界扫描单元发送第一次测试矢量;

39.步骤s443:指令寄存器加载外测试指令;

40.步骤s444:ate端接收第一次测试响应,与期望值比对,同时tdi端口发送第二次测试激励;

41.重复执行步骤s444即可完成测试。

42.nbs器件表示非边界扫描(non-boundary scan,nbs)器件;

43.bs器件表示边界扫描(boundary scan,bs)器件。

44.本发明的有益效果是:

45.针对sip芯片与ate系统之间的不同互连模型,高效快捷地生成jtag总线测试时序,提升测试效率。

附图说明

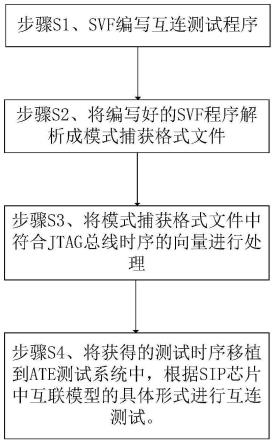

46.图1是本发明实施例基于ate的sip芯片内部互连测试方法的流程图;

47.图2是本发明实施例svf程序的示意图;

48.图3是本发明实施例转换得到的pcf文件示意图;

49.图4是本发明实施例测试时序的示意图;

50.图5是本发明实施例逻辑簇互连模型和存储器互连模型的结构示意图;

51.图6是本发明实施例ate协同互连模型的结构示意图;

52.图7是本发明实施例扫描链互连模型的结构示意图;

53.图8是本发明实施例ate直连模型的结构示意图。

具体实施方式

54.以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本发明的其他优点与功效。本发明还可以通过另外不同的具体实

施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。需说明的是,在不冲突的情况下,以下实施例及实施例中的特征可以相互组合。

55.需要说明的是,以下实施例中所提供的图示仅以示意方式说明本发明的基本构想,遂图式中仅显示与本发明中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的型态、数量及比例可为一种随意的改变,且其组件布局型态也可能更为复杂。

56.实施例一:

57.如图1所示,本发明实施例提出的基于ate的sip芯片内部互连测试方法具体包括如下步骤:

58.步骤s1、svf编写互连测试程序。svf语言在工业界应用较为成熟,是对jtag总线操作的高级描述,其主要应用场景有可编程器件的程序加载和边界扫描测试逻辑描述,二者都是基于jtag接口完成相应的操作。在quartus和ise开发环境中,均可生成用于描述程序设计的svf文件,并且通过仿真器和jtag接口完成svf文件的解码及程序在线加载。svf除了在cpld、fpga可编程器件中的应用外,还常用于板级jtag互连测试。在jtag互连测试中svf主要用于测试流程及方法的描述,具有良好的可读性和通用性。表1展示了ieee1149.1状态机状态与svf指令的对应关系,如表1所示,svf中强制规定的部分测试指令与ieee 1149.1中jtag状态机中的状态一一对应。在边界扫描测试中,主要通过对状态机状态的切换进行测试指令设置与测试数据收发,svf语句可对这一过程进行详细的描述。因此可以根据具体的测试需求编写相应的svf测试程序,再将svf测试文件转换成符合jtag总线的测试时序,即可在ate测试平台完成测试。

59.ieee11.49.1状态名svf指令test-logic-resetresetrun-test/idleidleselect-dr-scandrselectcapture-drdrcaptureshift-drdrshiftexit1-drdrexit1

…………

exit1-irirexit1pause-irirpauseexit2-irirexit2update-irirupdate

60.表1

61.步骤s2、将编写好的svf程序解析成模式捕获格式(pcf)文件。具体地,以图2所示的svf程序为例进行说明,首先,svf程序前14行的作用是控制jtag状态机运行到run-test/idle状态,为后续进行指令寄存器操作和数据寄存器操作做好准备,由tapc的状态机切换原理可知,无论状态机的初始状态在什么位置,只要状态控制引脚tms发出5个及5个以上时钟周期的高电平信号,状态机都会跳转到run-test/idle状态,前14行的svf程序转码过后

在pcf文件中生成的测试矢量为图3中的test logic reset部分,test logic reset部分依次描述了每个时钟周期tck、tms、tdi、tdo的电平状态,紧接着,向指令寄存器发送idcode指令sir 6tdi(04)mask(3f),其中,sir为指令寄存器发送命令,后面的6代表目标器件的指令寄存器长度,tdi(04)表示从tdi端口向指令寄存器写入“000100”idcode指令,mask(3f)表示前面的tdi端口输入的数据低6位有效,sir 6tdi(04)mask(3f)程序对应到pcf文件中的测试矢量如图3的loading device with"idcode"instruction部分,向指令寄存器写入idcode指令后,器件的标识寄存器被连接在tdi/tdo链路中,sdr32tdi(00000000)smask(00000000)tdo(000ae02f)mask(ffffffff)程序用于完成器件标识的读取与验证,其中,sdr为数据寄存器操作指令,由bsdl文件可知,器件的标识数据为000ae02f,tms端口控制状态机运转到shift-dr状态,并在clk时钟的下降沿将标识信息从tdo端口移出,完成id数据读取后tms控制状态机返回到run-test/idle状态,pcf文件中对应的测试矢量如图3的readid部分。

62.步骤s3、将模式捕获格式(pcf)文件中符合jtag总线时序的向量进行处理。以图3所示的pcf文件为例,将文件中的test logic reset部分、loading device with"idcode"instruction部分和readid部分转变为测试时序,具体形式如图4所示。

63.步骤s4、将获得的测试时序移植到ate测试系统中,根据sip芯片中互联模型的具体形式进行互连测试。sip芯片中的互连模型包括逻辑簇互连模型、存储器互连模型、ate协同互连模型、扫描链互连模型、ate直连模型、以及其他模型等。

64.如图5所示,在逻辑簇互连模型中,非边界扫描器件所有io引脚全部连接在边界扫描链路上,这种模型在sip芯片内部较为常见,逻辑簇互连模型与存储器互连模型十分相似,nbs器件的所有io引脚均与边界扫描链路进行连接,因此,上述模型也可称之为存储器互连模型。

65.nbs器件的所有io端口被扫描链路环绕,将与nbs器件输入端相连的边界扫描单元设置为输入模式,输出端口相连的边界扫描单元设置为采样模式,采用extest测试指令进行测试,具体测试步骤如下:

66.步骤s411:指令寄存器发送extest测试指令;

67.步骤s412:通过与nbs输入端相连的边界扫描单元向nbs输入端口发送一个周期的测试激励;

68.步骤s413:与nbs输出端口相连的边界扫描单元接收第一个测试周期的测试响应与期望值进行分析,同时输入端的边界扫描单元继续发送第二周期的测试激励。

69.重复步骤s413即可完成该逻辑簇模型的测试。

70.如图6所示,ate协同互连模型中nbs电路被扫描链路环绕,输入端口与边界扫描链路相连,输出端口与ate系统直接相连,具体测试步骤如下:

71.步骤s421:指令寄存器发送预装指令;

72.步骤s422:通过tdi引脚向与nbs器件相连的边界扫描单元发送第一次测试矢量,此时第一次测试激励还没有作用于nbs器件的输入端口;

73.步骤s423:指令寄存器加载外测试指令,此时预装指令发送的第一次测试激励作用于nbs器件的输入端;

74.步骤s424:ate端接收nbs器件的第一次测试响应,与期望值比对,同时tdi端口发

送第二次测试激励。

75.重复执行步骤s424即可完成对nbs器件所有周期的测试向量验证。

76.如图7所示,扫描链互连模型中两个bs器件的边界扫描单元互相连接,所有的互连端口均与边界扫描链路连接,该种互连模型在sip芯片中也十分常见。针对扫描链互连模型的测试方法仍然延续板级互连测试系统中的测试方法,以半数网络端口为输入端、半数网络端口为输出端,通过边界扫描单元完成输入端数据的设置以及输出端数据的读取,具体测试步骤如下:

77.步骤s431:指令寄存器发送预装指令;

78.步骤s432:通过tdi引脚向bs1器件的边界扫描单元发送第一次测试矢量;

79.步骤s433:指令寄存器加载外测试指令;

80.步骤s434:bs2器件端边界扫描单元接收第一次测试响应,与期望值比对,同时tdi端口发送第二次测试激励。

81.重复执行步骤s434即可完成对扫描链互连模型完成测试。

82.如图8所示,ate直连模型中边界扫描器件的io口直接与ate建立物理连接。针对ate直连模型的测试,ate系统可以作为输入端发送高低电平,边界扫描单元检测ate发送的高低时序,从而完成ate直连网络的测试。反之,以边界扫描单元作为输入端发送高低电平,ate端来检测边界扫描单元发送的高低电平。bs器件的边界扫描单元引脚与ate系统的数字通道直接相连,具体测试步骤如下:

83.步骤s441:指令寄存器发送预装指令;

84.步骤s442:通过tdi引脚向与bs器件相连的边界扫描单元发送第一次测试矢量;

85.步骤s443:指令寄存器加载外测试指令;

86.步骤s444:ate端接收第一次测试响应,与期望值比对,同时tdi端口发送第二次测试激励。

87.重复执行步骤s444即可完成对ate直连模型完成测试。

88.以上所述实施例仅表达了本发明的具体实施方式,其描述较为具体和详细,但并不能因此而理解为对本发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1