一种超导电路低温到室温的高速信号传输装置及测试系统

1.本发明涉及超导电路传输技术领域,特别是涉及一种超导电路低温到室温的高速信号传输装置及测试系统。

背景技术:

2.超导计算机因为其高速与低功耗特性受到各方的关注和积极研究。其中,超导计算机的核心sfq(单磁通量子)电路的高速信号处理能力及输入输出能力至关重要,而sfq电路又需要工作在4.2k的低温环境。故超导电路高速信号的输入输出涉及到低温(4.2k)到室温(300k)的跨温区互联。并且,低温(4.2k)sfq电路的输出信号十分微弱(几mv),需要利用低噪声的读出电路将信号读出并放大,但同时放大后的信号必须保持为数字信号的格式,才能在输出到室温(300k)被后端室温电子系统进行采集并分析。随着超导芯片电路的日益复杂化和多芯片模块的日益集成化,对芯片的测试提出了越来越高的需求。

3.现有的超导逻辑电路测试系统,基于美国researchelectronicsdevelopment,inc生产的多通道octopux,该设备明确说明用于超导逻辑电路的低频测试,支持最高信号频率为1mhz。这样的测试在超导逻辑电路的开发阶段验证完全满足超导逻辑电路的功能测试和验证。但是,超导逻辑电路相对cmos逻辑电路的优势在于其工作主频可高达数十ghz,因此,需要能支持更高速度的一套超导逻辑电路的测试和适用于未来超导逻辑电路应用的技术方案,发挥超导逻辑电路的高速不可替代的优势。

4.目前超导sfq电路的高频测试,常采用片上高频测试的方法,低频输入,使片上产生高频信号,再降频到低频输出。高频时钟个数受限于sr数量,测试pattern数量有限,且并非严格意义上的高频输入/输出测试。

技术实现要素:

5.本发明所要解决的技术问题是提供一种超导电路低温到室温的高速信号传输装置及测试系统,实现了严格意义上的高频输入/输出测试。

6.本发明解决其技术问题所采用的技术方案是:提供一种超导电路低温到室温的高速信号传输装置,包括测试杆,所述测试杆一端连接低温样品腔,另一端连接室温安装盒;所述低温样品腔内设置有低温端高频测试pcb,所述低温端高频测试pcb上设有超导芯片安装位和输入/输出端口,所述输入/输出端口与所述低温端高频测试pcb上的线路相连,所述输入/输出端口为ssmp连接器;所述室温安装盒侧面设有输入端口和输出端口,所述输入端口为sma连接器,所述室温安装盒内设置有室温放大器,所述室温放大器的输入端与sma连接器相连,输出端与所述输出端口相连;所述测试杆内设置有低温-室温同轴线缆,所述低温-室温同轴线缆的低温端与所述ssmp连接器接口相连,室温端与所述sma连接器相连。

7.所述低温端高频测试pcb采用rogers4350板材与fr4层压板制成,所述低温端高频测试pcb上的线路经过50欧姆阻抗匹配。

8.所述低温-室温同轴线缆为半刚性同轴线缆,采用铍铜制成,所述低温-室温同轴

线缆的低温端的接口为ssmp连接器,所述ssmp连接器与所述低温端高频测试pcb上的ssmp连接器互为一对公母;所述低温-室温同轴线缆的室温端直接与所述室温安装盒上的sma连接器相连。

9.所述室温放大器包括级联的一级低噪声放大器和二级限幅放大器,所述一级低噪声放大器,工作频率为50khz~12ghz,增益大于25db,输入信号灵敏度为mv级;所述二级限幅放大器支持传输速率最高达到12.5gbps,差分增益为44db,输入信号灵敏度为2mvp-p,输出电压最高达到880mvp-p。

10.本发明解决其技术问题所采用的技术方案是:提供一种超导芯片测试系统,包括上述的超导电路低温到室温的高速信号传输装置,所述超导芯片安装位上安装有待测超导芯片,所述室温安装盒的输出端口分别与示波器和数据采集分析系统相连,所述示波器用于采样信号和波形测试,以实现输出波形分析和高速信号传输眼图分析;所述数据采集分析系统用于进行误码率测试。

11.所述待测超导芯片通过低温胶固定于超导芯片安装位上,并通过引线键合实现与所述低温端高频测试pcb上的线路的连接。

12.所述数据采集分析系统包括相互连接的fpga和上位机;所述fpga包括依次连接的gty模块和bert模块,所述gty模块用于将高速串行数据转换为并行数据;所述bert模块用于计算并行数据中的ber;所述上位机用于解析fpga输出的数据,并进行显示。

13.有益效果

14.由于采用了上述的技术方案,本发明与现有技术相比,具有以下的优点和积极效果:本发明中超导芯片的输出高速信号由低温端pcb上ssmp接口传输到同轴线缆,再由同轴线缆传输到测试杆室温安装盒sma接口,再连接室温线缆和室温放大器将传导到室温的微弱超导信号(几mv)进行放大整形处理,变为信号幅值大于几百mv的数字信号,由传输线缆连接到测试设备进行信号输出和数据采集分析。与现有的高频测试方法相比,本发明能支持更高速度的超导逻辑电路的测试,且整个信号传输过程都是高频信号,实现了严格意义上的高频输入/输出测试。

附图说明

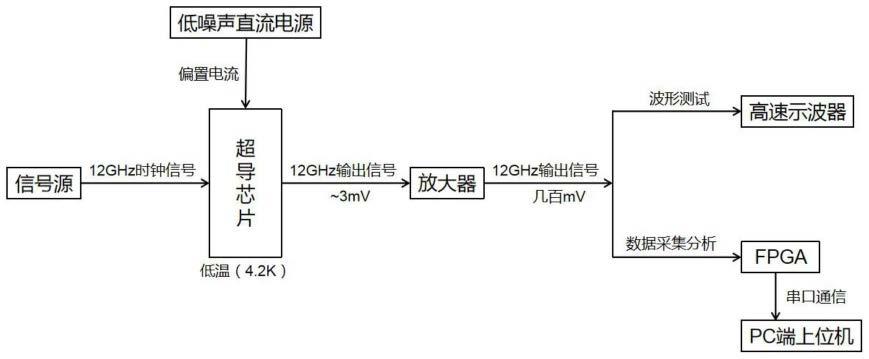

15.图1是本发明实施方式的硬件连接图;

16.图2是本发明实施方式的测试示意图;

17.图3是本发明实施方式中低温端高频测试pcb的示意图;

18.图4是本发明实施方式中ssmp连接器的示意图;

19.图5是本发明实施方式中低温-室温同轴线缆的示意图;

20.图6是本发明实施方式中低温-室温同轴线缆与低温端高频测试pcb的连接示意图;

21.图7是本发明实施方式中室温放大器的示意图;

22.图8是本发明实施方式中12gbps输出信号波形和信号传输眼图;

23.图9是本发明实施方式中fpga中的工程模型图;

24.图10是本发明实施方式中fpga的bert实现原理图。

具体实施方式

25.下面结合具体实施例,进一步阐述本发明。应理解,这些实施例仅用于说明本发明而不用于限制本发明的范围。此外应理解,在阅读了本发明讲授的内容之后,本领域技术人员可以对本发明作各种改动或修改,这些等价形式同样落于本技术所附权利要求书所限定的范围。

26.本发明的实施方式涉及一种超导电路低温到室温的高速信号传输装置,如图1和图2所示,包括测试杆1,所述测试杆1一端连接低温样品腔2,另一端连接室温安装盒3;所述低温样品腔2内设置有低温端高频测试pcb,所述低温端高频测试pcb上设有超导芯片安装位和输入/输出端口,所述输入/输出端口与所述低温端高频测试pcb上的线路相连,所述输入/输出端口为ssmp连接器;所述室温安装盒3侧面设有输入端口和输出端口,所述输入端口为sma连接器,所述室温安装盒3内设置有室温放大器,所述室温放大器的输入端与sma连接器相连,输出端与所述输出端口相连;所述测试杆1内设置有低温-室温同轴线缆,所述低温-室温同轴线缆的低温端与所述ssmp连接器接口相连,室温端与所述sma连接器相连。

27.本实施方式的高速信号传输装置能够应用于超导芯片的测试,下面针对高速超导电路器件,尤其是一款基于超导sfq电路的12ghz高速线性反馈移位寄存随机数发生器芯片,进一步说明采用本实施方式的高速信号传输装置的测试系统。

28.该测试系统包含:低温端高频测试pcb,液氦杜瓦和测试杆组成的低温系统,低温到室温输出放大互联链路,室温端数据采集分析fpga,pc端上位机界面演示系统等(如图1)。其中,超导芯片通过低温胶放置固定于低温端高频测试pcb21的超导芯片安装位22上,并通过引线键合实现超导芯片与低温端高频测试pcb21上线路的连接。低温端高频测试pcb21放置于测试杆1的低温样品腔2内,通过将测试杆1插入液氦杜瓦4(低温样品腔向下浸入液氦中)实现超导芯片的低温(4.2k)环境(如图2)。低温-室温互联同轴线缆贯穿整个测试杆1杆体内,两端分别连接低温样品腔2和室温安装盒3,实现低温与室温的互联与信号传输。超导芯片的高频输入输出通过低温端高频测试pcb21上的ssmp高速接口23直接与低温-室温同轴线缆连接。超导芯片测试需要的偏置电流与时钟信号通过测试杆的室温安装盒3上的sma接口由室温端提供进入测试杆1,再由同轴线缆传到低温端。超导芯片的输出高速信号由低温端高频测试pcb21上的ssmp接口23传输到同轴线缆,再由同轴线缆传输到测试杆室温安装盒3的sma接口,再连接室温线缆和室温放大器将传导到室温的微弱超导信号(几mv)进行放大整形处理,变为信号幅值大于几百mv的数字信号,由传输线缆连接到测试设备进行信号输出和数据采集分析。

29.本实施方式中的超导芯片为一款基于超导sfq电路的12ghz高速线性反馈移位寄存随机数发生器芯片。芯片电路的时钟频率为12ghz,随机数生成速率为12gbps,产生的随机数数量为1.4

×

10

14

,输出信号幅度为3mv,工作温度在4.2k。其中,输入的12ghz时钟信号由信号源提供。芯片工作需要的偏置电流由低噪声直流电源提供。

30.本实施方中的高频测试pcb21(如图3),为超导芯片低温测试pcb,安装于测试杆的低温样品端,工作温度4.2k,采用rogers4350板材与fr4层压板,板上走线经过50欧姆阻抗匹配,支持传输信号频率几十ghz。

31.所述的低温端高频测试pcb21上的高速输入/输出接口23采用ssmp连接器(如图4),直接与低温-室温同轴线缆连接,实现与室温端互联,支持信号传输速率达几十gbps。传

统的样品端测试pcb与测试杆低温端样品座通过直接焊接和压接的方式实现互联,支持信号传输速率《1mbps,仅适用于低频测试。

32.所述的低温-室温互联传输通过多根同轴线缆(如图5)。所述的同轴线缆为导体材质为铍铜的半刚性同轴线缆,热容低,用于低温环境,可尽可能阻止高温端的热量传入。所述的同轴线缆低温端接口为ssmp连接器,与低温端高频测试pcb上的ssmp连接器互为一对公母,可实现对插连接(如图6);所述的同轴线缆的室温端接口直接与固定装配于室温端安装盒侧壁的sma连接器相连,可实现与室温测试设备的连接。

33.所述的室温放大器(如图7),为工作在室温(300k)的放大链路,包含一级低噪声放大器和二级限幅放大器。增益可达50db以上,带宽到12ghz。可以将超导芯片从低温传输到室温的输出信号(几mv量级,经过传输线缆损耗后小于1mv)经过放大处理,信号幅值达到几百mv以上,在室温下被室温端设备进行数据采集和分析。支持vpp≥3mv、12gbps的信号传输,误码率《10-12

。

34.所述的一级低噪声放大器,工作频率50khz~12ghz,增益大于25db,输入信号灵敏度为mv级,噪声4db左右。所述的二级限幅放大器,支持传输速率到12.5gbps,差分增益44db,输入信号灵敏度2mvp-p,输出电压达880mvp-p。

35.所述的超导电路的输出信号经过室温放大器放大后,可用高速示波器进行采样和波形测试,包括输出波形分析和高速信号传输眼图分析(如图8)。高速波形测试具体步骤为:1)超导芯片去磁deflux。2)向超导芯片各直流偏置电流端子外加通过低速测试获得的工作margin的中心值的偏置。在高速时钟输入用端子中,输入正弦波i(t)=i

in

sin(2πft),观测输出波形out。高速时钟信号由信号源psg提供。输出波形由示波器观测。将波形数据进行二值化,将第i周期的输出逻辑值(“0”或“1”)设为f(i),并使用以下关系公式判定正常工作:

36.f(i)=xor[f(i-47),f(i-42)]

[0037]

如果电路不正确工作,则调整直流偏置电流,以寻找正常工作点。如果得到了完全正常工作的偏置点,则测试各直流偏置电流和时钟信号输入电流振幅的工作区域。通过个别的改变各电流来记录输出波形,并测试工作margin。每个芯片电路均经过多次高速测试,确保电路工作稳定。

[0038]

数据采集分析为相互连接的fpga和pc上位机,其能进行误码率测试,可以更具体和准确的分析输出随机数码流的质量。所述的fpga进行超导电路输出数据信号(放大后)码流误码率(ber)的计算原理为:超导芯片输出的高速串行数据首先进入到fpga中的gty模块(该模块可以将高速串行数据转换为并行数据),然后并行数据进入到bert模块(该模块可以计算出数据中的ber)(如图9),最后将ber结果通过串口发送给电脑端,电脑端用python编程来解析数据,并在gui界面中显示。

[0039]

其中,bert模块的实现原理为:根据prbs-47的生成过程,bit(i)=xor[bit(i-47),bit(i-42)](其中i指第i个bit),可知每一位都是由它之前的第42位和第47位异或得到的。所以,可以根据这个规则来得到数据的预期码,进而计算出接收数据的ber。fpga中的实现原理为(如图10):在寄存器处理单元中,a,b是两个64位的寄存器(这里将64位视为一帧数据),a中的第0位是最先到的bit,b中的第127位是最后到的bit。每一个clock上升沿都会将b寄存器的数据更新到a中,同时b中会补充新的一帧,此时得到了一个128位的先后到

达的数据。根据前面的规则可知,第0位与第5位异或就是第47位的预期码,第1位与第6位异或就是第48位的预期码,按此规律,每一个clock都可以得到b寄存器的真实码和对应的预期码。将该真实码和预期码异或,会得到一个64位宽的数据,其中为1的位置代表出现了误码,因此只需要统计1的个数(即num of errors),就得到了误码的个数,再统计出总的bits数(即totalbits),然后根据下式即可得到ber:

[0040][0041]

输出误码率(ber)测试的测试条件同输出波形测试,高速时钟信号由信号源psg提供,只是输出信号经过放大后连接fpga,再通过串口连接到pc端上位机,对输出伪随机数码流进行误码判断。

[0042]

不难发现,本发明中超导芯片的输出高速信号由低温端pcb上ssmp接口传输到同轴线缆,再由同轴线缆传输到测试杆室温安装盒sma接口,再连接室温线缆和室温放大器将传导到室温的微弱超导信号(几mv)进行放大整形处理,变为信号幅值大于几百mv的数字信号,由传输线缆连接到测试设备进行信号输出和数据采集分析。与现有的高频测试方法相比,本发明能支持更高速度的超导逻辑电路的测试,且整个信号传输过程都是高频信号,实现了严格意义上的高频输入/输出测试。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1