一种基于MEMS工艺的微尺度二维阵列式集成测温方法与流程

一种基于mems工艺的微尺度二维阵列式集成测温方法

技术领域

1.本发明属于微尺度测温领域,特别是涉及一种基于mems工艺的微尺度二维阵列式集成测温方法。

背景技术:

2.微技术和纳米技术的最新进展已经产生了涉及大量微通道的微流体设备,以便使用非常少量的流体进行分析。为了进一步开发芯片实验室和微型全分析系统等设备,了解微通道中多相流、单相流传输过程的物理特性非常重要。此外、监测和优化流体/壁温、压力和速度等流动条件是必不可少的,这需要将检测系统集成在微通道中,例如将用于监测通道壁边界条件的硅基温度传感器阵列集成到微通道中。微通道的水力直径、宽高比、粗糙度、表面结构和表面改性等方面已经存在了大量的研究,但是不同学者的研究结果之间存在一定差异,甚至有自相矛盾处,尤其是流动换热领域的实验结果。

3.产生这一问题的主要原因在于微尺度测温技术并没有随着微机械的发展而变得更加完善和准确,很大程度上借鉴了传统的测试方法和测试手段,如spizzichino m等人的热电偶线测温方案:

4.spizzichino m,sinibaldi g,romano g p.experimental investigation on fluid mechanics of micro-channel heat transfer devices[j].experimental thermal and fluid science(exp therm fluid sci),2020,118:110141.

[0005]

少数根据微机电系统集成开发的微传感器技术,尚处在研究阶段,理论和工艺上仍有欠缺。同时目前提出的集成测温技术,仍然是以单点测温为主,如zhenlanxue等人利用金薄膜热电阻作为集成的温度传感器。

[0006]

zhenlanxue,huiheqiu.integrating micromachined fast response temperature sensor array in a glass microchannel[j].sensors and actuators a,122,2005,189

–

195.

[0007]

然而,传感器数量增加所带来的工艺、测试等问题限制了数据点的数目,相对于微尺度先进测温技术的需求来说,仍然有所不足。因此需要开发一套以mems工艺为基础的测温阵列技术,突破传统工艺的限制,实现温度传感器的集成设计和布置,采用先进的设计理念和数学模型,实现温度传感器的阵列布置,从原有的一维测温技术迈向二维温度场的测试,形成微尺度测试技术领域标准化的测试方法,得到精确的统一的研究结论,产生先进的科研成果和实用的工业产品。

[0008]

在当前的微尺度测温方案中,主要存在两大问题。首先是测试精度不足,实验数据依赖传统测温方法,以市场中销售的热电偶或者热电阻为主,直接布置在所需要测试设备的表面,布置所产生的手工误差处于毫米级,而微尺度通道的水力直径一般是微米级的,这样的测试精度在微尺度测温中是难以忍受的。其次是数据点数目不足,当前无论是传统的热电偶或者薄膜热电阻的手工布置,还是较为先进的热电偶、热电阻集成布置,都是处于单点测温的范围,对于单个实验件来说,数据点的数目一般不会超过十个,能够得到的数据极

为有限,因此对完整地描述微尺度通道内的流场信息的目标仍然是相差甚远。此外,红外测温是目前一种常用的二维测温手段,也被应用于微尺度领域中,但是像素点的大小普遍在几十微米的量级,同时需要对于实验件的材料、观测的位置有着严格的限制,对于温度测试的精度稍弱于热电偶和热电阻,加上高分辨率的光学器件所带来的高昂的价格,往往令许多研究人员望而却步。

技术实现要素:

[0009]

本发明是为了提出一种相比于现有的测温方法集成化程度更高、数据点数目更多的微尺度二维阵列式集成测温技术,实现微尺度测温方案的二维化、集成化、标准化测量要求。依托于当前mems加工技术,将测温热电阻从传统的毫米级布置精度达到上升到微米级,布置方式更加合理,实现通道的原位测量。依托于二维电阻网络的设计,通过电阻网络的外端阻值测试,反演内部阻值,根据金属的电阻温度特性,推导得到相应的温度场,实现微尺度温度场的高精度集成化测试,降低各类误差。

[0010]

为实现上述目的,本发明提供了一种基于mems工艺的微尺度二维阵列式集成测温方法,包括:

[0011]

s1.基于mems磁控溅射工艺将二维测温热电阻网络集成在微流体设备中;

[0012]

s2.建立数据点与外端阻值的数学关系模型;

[0013]

s3.测试得到所述电阻网络的外端阻值,反演得到所述电阻网络的内部阻值,基于所述电阻网络中的电阻温度特性以及所述关系模型,推导得到所述微流体设备的微通道内的温度场分布。

[0014]

可选的,所述微流体设备包括:玻璃片、中间硅片和下硅片;

[0015]

步骤s1中,所述将二维测温热电阻网络集成在微通道设备中的步骤为:

[0016]

s11.加工玻璃片;

[0017]

s12.加工中间硅片;

[0018]

s13.加工下硅片;

[0019]

s14.将玻璃片、中间硅片和下硅片依次键合。

[0020]

可选的,所述数据点与引线的关系为:

[0021][0022]

其中,n为所述数据点个数,b为所述引线个数。

[0023]

可选的,所述二维测温电阻网络的所述数据点的数目小于等于测试数据的个数。

[0024]

可选的,所述电阻网络中各电阻的材质、尺寸、阻值均相同。

[0025]

可选的,所述电阻网络中各电阻均为薄膜铂热电阻。

[0026]

可选的,步骤s2中,所述数学关系模型为:

[0027][0028]

其中n为两两互相联通的数据点之间电阻线的数目,a1~an为两两互相联通的数据

点之间电阻线的阻值,b为外部测试点的数目,为外部测试点之间的阻值,为外部测试点和所述数据点阻值之间的函数关系式,具体的函数形式根据电阻网络的形式确定。

[0029]

可选的,步骤s3中,所述反演的具体方法有两种:分别为迭代法和拉普拉斯矩阵法。

[0030]

可选的,所述迭代法是根据原始值对原方程组进行迭代计算,具体的解析式的形式根据电阻网络确定,可采取的理论方法有二分法、简单迭代法、牛顿法和弦割法,得到内部数据点之间电阻线的阻值,对内部数据点之间的阻值和温度建立线性方程组,采用最优化方法求解线性方程组,得到优化解如最小二乘解等,即为电阻网络的内部温度场;

[0031]

所述拉普拉斯矩阵法则是首先根据电阻网络构建拉普拉斯矩阵,拉普拉斯矩阵就是代表数据点之间电阻线的阻值和外部测试值之间的联系,之后对拉普拉斯矩阵求解广义逆,期间利用最优化方法如kkt方法,根据外部测试值得到内部数据点之间的阻值,对内部数据点之间的阻值和温度建立线性方程组,最后再次采用最优化方法求解线性方程组,得到优化解如最小二乘解,即为电阻网络的内部温度场。

[0032]

本发明的技术效果为:

[0033]

本发明将二维电阻网络与微尺度测温进行有机结合,通过电阻网络的外端阻值测试,建立数学模型,反演内部阻值,根据金属的电阻温度特性,推导得到二维温度场,创新性地实现了用接触式测温方法获得高精度温度场。

[0034]

本发明通过二维电阻网络的灵活设计,在满足数据点的数目小于等于测试数据的数目的前提下,依据不同的测试场景和工艺条件,二维电阻网络可以设计成任意形状和任意疏密程度,丰富了加工方法的和实际应用的多样性和可控性。

[0035]

本发明通过引线pad交叉组合测试的方法,与二维电阻网络的设计相结合,在引线pad之间进行两两排列组合测试,显著减小了相同数据点下引线pad的数目。

[0036]

本发明通过薄膜热电阻的集成化布置,利用mems磁控溅射工艺布布置薄膜热电阻二维网络,达到微米级的布置精度和加工精度,实现集成化测量。

附图说明

[0037]

构成本技术的一部分的附图用来提供对本技术的进一步理解,本技术的示意性实施例及其说明用于解释本技术,并不构成对本技术的不当限定。在附图中:

[0038]

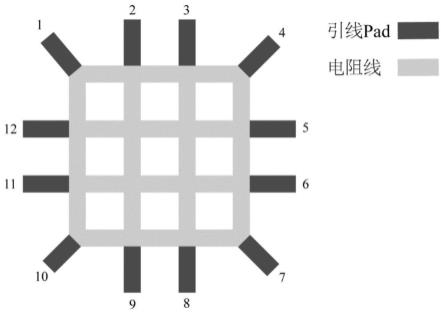

图1为本发明实施例中的阐述微尺度二维阵列式测试技术4*4矩形阵列式电阻网络方案示意图;

[0039]

图2为本发明实施例中的阐述微尺度二维阵列式测试技术4*4至m*n矩形阵列式电阻网络原理图;

[0040]

图3为本发明实施例中的阐述微尺度二维阵列式测试技术与传统测试技术对比的示意图;

[0041]

图4为本发明实施例中的阐述基于mems的微尺度二维阵列式集成测温实验件概念图;

[0042]

图5为本发明实施例中的实验件加工工艺流程图;

[0043]

图6为本发明实施例中的玻璃片加工工艺俯视图;

[0044]

图7为本发明实施例中的中间硅片加工工艺俯视图;

[0045]

图8为本发明实施例中的中间硅片加工工艺底视图;

[0046]

图9为本发明实施例中的下硅片加工工艺俯视图。

[0047]

其中:

[0048]

图6中:1-加热膜pad引线通孔;

[0049]

图7中:1-微通道;2-扰流柱;3-键合面;4-加热膜pad引线通孔;

[0050]

图8中:1-二维阵列式薄膜热电阻;2-薄膜热电阻pad;

[0051]

图9中:1-加热膜;2-加热膜pad;3-薄膜热电阻pad引线通孔;

具体实施方式

[0052]

需要说明的是,在不冲突的情况下,本技术中的实施例及实施例中的特征可以相互组合。下面将参考附图并结合实施例来详细说明本技术。

[0053]

实施例一

[0054]

如图1-9所示,本实施例中提供一种基于mems工艺的微尺度二维阵列式集成测温方法,包括:

[0055]

在微尺度薄膜热电阻的集成工艺设计上,本发明的方案采用以二维电阻网络为基础的阵列式测温系统,取代原有的单点热电阻方案,通过电阻网络的外端阻值测试,得到电阻网络的内部阻值,然后利用薄膜热电阻本身的电阻温度特性,推导得到温度场的分布。本发明方案中的二维电阻网络可以是任意形状和任意疏密程度,只需要满足数据点的数目小于等于测试数据的个数。

[0056]

在二维阵列式集成测温系统的测试原理上,本发明方案采用了前沿学术研究中的电阻网络进行温度传感器的布局,如图1所示。本发明方案中并不局限于数据点的数目和电阻网络的形状,为便于理解,以4*4矩形阵列式电阻网络为例进行原理分析,如图2所示。对于4*4的矩形阵列式电阻网络来说,数据点共有16个,分布在电阻线之间的交接点,每两个数据点之间的电阻线可以等效为电阻,该电阻的阻值会随温度的变化而变化,电阻网络从外部可以引出12个pad,两两之间相连可以得到66个外部测试阻值ri,这些外部测试阻值和16个温度数据点之间可以建立对应的数学模型:

[0057][0058]

可以看出,外部测试阻值的数目超过数据点的数目,因此可以采用最优化方法,拟合方程结果,得到最优解。同时证明可以减小引线pad的数量,排除坏点,提高工艺制造过程中的容错率,将二维电阻网络引入测温系统中,使得本发明从测试原理出发优化了整体的测温系统。

[0059]

在二维阵列式集成测温系统的测试逻辑上,本发明采用多个引线pad互相连通的交叉测试方法。相对于传统单点测试的方案来说,实现了引线pad数目的显著降低。在传统的单点测试方案中,一个薄膜热电阻的由正负极组成,两个引线pad,得到一个数据点,即使考虑到接地端的共用,若需要测得a个数据点,需要有效pad个数至少为a+1个;然而对于二

维阵列式测试方案来说,任意两个引线pad之间都相互连通,可以得到相应的电阻值,若需要测得a个数据点,仅仅需要b个有效pad的个数,使得因变量个数大于自变量个数,从而方程有解。在图3中可以看出,所需要测试点的数据越多,二维阵列式测温方案相对于传统测试方法的优势就越明显。

[0060]

在二维阵列式集成测温系统的集成工艺上,采用mems集成测温技术,在通道下表面磁控溅射薄膜热电阻,实现微米量级的布置精度,实现高精度的原位测量,利用icp等离子体刻蚀技术,加工复杂结构的微通道,同时预留引线点,做到集成化的测温系统设计。

[0061]

依据专利发明方案,提出一例基于mems工艺的微尺度二维阵列式集成测温技术设计方案,并给出各自对应的加工方案。设计方案方面,本集成测温技术是由两个部分组成,第一部分是二维阵列式集成实验件设计(如图4所示),第二部分是基于mems工艺的加工(如图5所示)。

[0062]

本实验件的设计以矩形阵列为主,设计了5*4的长方形矩形阵列,总共有外部引线数目8个,可测得28个值,总共有数据点20个,测试点的数目大于数据点的数目,以下方程有解:

[0063][0064]

测试点的数目大于数据点的数目,因此本实验在进行后处理的过程中采用最优化方法中的最小二乘法对测得的数据进行拟合和分析,从而得到最终的内部电阻值,最后根据铂金属的电阻温度特性,推导得到温度场分布。

[0065]

本实验件的加工设计是由三层晶圆键合(如图5)完成,三层晶圆从上到下依次为玻璃片、中间硅片和下硅片,键合方式分别为硅-玻璃阳极键合,硅-硅辅助键合。玻璃片和中间硅片的阳极键合主要起到密封微通道(如图7中1和2所示)的作用,中间硅片和下硅片的辅助键合主要起到下硅片的加热膜(如图9中1所示)和微通道(如图7中1和2所示)及薄膜热电阻(如图8中1所示)集成的作用。玻璃片工艺的主要目的是留出下硅片加热膜的引线位置(如图6中1所示),中间硅片工艺的主要目的是集成底部的二维阵列式薄膜热电阻网络(如图8中1和2所示),下硅片工艺的主要目的是集成与设计加热区域尺寸相同的加热膜(如图9中1所示),工艺步骤如下(如图6):

[0066]

1、玻璃片的加工流程

[0067]

步骤一:对玻璃片进行清洗,去除玻璃片表面的灰尘、杂质和有机物,具体步骤是去离子水-酒精-丙酮-酒精-去离子水,清洗完成后采用烘箱烘干玻璃片表面水分。

[0068]

步骤二:将4英寸500μm厚的玻璃片进行激光切割打孔,加工下硅片的引线通孔(如图6中1所示)。

[0069]

步骤三:对打孔后玻璃片进行清洗,去除玻璃片表面的灰尘、杂质和有机物,具体步骤是去离子水-酒精-丙酮-酒精-去离子水,清洗完成后采用烘箱烘干玻璃片表面水分。

[0070]

2、中间硅片的加工流程

[0071]

步骤一:对硅片进行清洗,去除硅片表面的灰尘、杂质和有机物,具体步骤是去离子水-酒精-丙酮-酒精-去离子水,清洗完成后采用烘箱烘干硅片表面水分。

[0072]

步骤二:将4英寸340μm厚的双抛氧化本征硅片,氧化层厚度为2um,首先旋涂光刻胶s1813,其次紫外曝光图7中的结构图案,用专门的显影剂进行显影,然后浸入boe溶液中,一段时间后选择性去除正面通道、背面通孔、对准标记处氧化层,清洗硅片。

[0073]

步骤三:涂胶曝光,采用光刻胶作为掩膜,紫外曝光显影后,图案化磁控溅射ti粘附层,厚度6nm,图案化磁控溅射pt薄膜,厚度300nm(如图8中1所示)。图案化磁控溅射au薄膜,厚度300nm,作为薄膜热电阻的引线部分(如图8中2所示)。

[0074]

步骤四:低真空或氮气环境高温退火,升温速率300℃/h,温度600℃,保温时间4h,自然冷却,通过金属再结晶,使薄膜的电学性能更加稳定,同时减小薄膜应力。

[0075]

步骤五:完成正面通道300μm的刻蚀(如图7中1和2所示),后刻蚀引线通孔结构(如图7中4所示)。

[0076]

3、下硅片的加工流程

[0077]

步骤一:对硅片进行清洗,去除硅片表面的灰尘、杂质和有机物,具体步骤是去离子水-酒精-丙酮-酒精-去离子水,清洗完成后采用烘箱烘干硅片表面水分。

[0078]

步骤二:将4英寸500μm厚的双抛氧化硅片,氧化层厚度为2um,首先旋涂光刻胶s1813,其次紫外曝光(如图9中3所示)中的结构图案,用专门的显影剂进行显影,然后浸入boe溶液中,一段时间后选择性去除硅片正面、背面通孔以及对准标记处的氧化层(如图9中3所示)。

[0079]

步骤三:涂胶曝光,采用光刻胶作为掩膜,紫外曝光显影后,图案化磁控溅射ti粘附层,厚度10nm,图案化磁控溅射pt薄膜,厚度100nm,作为下硅片加热膜(如图9中1所示),图案化磁控溅射au薄膜,厚度300nm,作为下硅片的加热膜引线部分(如图9中2所示)。

[0080]

步骤四:低真空或氮气环境高温退火,升温速率300℃/h,温度600℃,保温时间4h,自然冷却,通过金属再结晶,使薄膜的电学性能更加稳定,同时减小薄膜应力。

[0081]

步骤五:等离子体刻蚀通孔,完成引线通孔的刻蚀(如图9中3所示)。

[0082]

4.多层晶圆依次键合

[0083]

步骤一:进行对上硅片和玻璃进行标准的硅-玻璃阳极键合。

[0084]

步骤二:在下硅片表面旋涂bcb辅助键合胶,放入键合机中,在真空条件下对玻璃-上硅片和下硅片进行辅助键合。

[0085]

以上所述,仅为本技术较佳的具体实施方式,但本技术的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本技术揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本技术的保护范围之内。因此,本技术的保护范围应该以权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1