一种毫米波雷达回波信号处理方法及系统与流程

本发明涉及雷达传感器,特别是涉及一种毫米波雷达回波信号处理方法及系统。

背景技术:

1、毫米波雷达指的是工作在30~300ghz波段(对应波长为1~100mm)的雷达装置。由于它具有不受气候与光线条件影响、探测距离远、轻量化、需要的运算量小、制造成本低等特点,被认为是自动驾驶技术中最重要的传感器技术之一,被用于高精度、立体化的测速、测距与避障等功能。

2、目前自动驾驶技术中使用的毫米波雷达的主流雷达波形是调频啁啾波(fmcw)。在这种波形体制下,雷达发射一系列啁啾波脉冲,它们构成一个雷达帧。每个回波脉冲内的时间尺度被称为快时间尺度,也叫做距离维。整个雷达帧内多个脉冲之间的时间尺度为称为慢时间尺度,也叫做速度维。对于每个回波脉冲,雷达进行距离维傅里叶变换,获取探测目标的距离维信息。然后对于整个雷达帧,再进行速度维傅里叶变换,获取探测目标的速度维信息。

3、在传统雷达芯片方案中,mmic芯片将啁啾波脉冲的数字基带信号通过片间数据接口传输到硬件加速器(hwa)或dsp芯片上进行硬件信号处理。为了获得更好的探测性能,数字基带信号的数据量也需要相应地上升,这对片间数据接口的传输速率提出了重大挑战。

技术实现思路

1、本发明目的是针对背景技术中存在的问题,提出一种毫米波雷达回波信号处理方法及系统解决雷达mmic芯片与数字基带芯片之间的传输瓶颈问题,增大雷达芯片能够处理的基带数据规模,从而提升雷达探测能力。

2、本发明的技术方案,一种毫米波雷达回波信号处理方法,包括以下具体步骤:

3、s1、进行雷达探测,通过接收阵列接收雷达发射信号经过反射后的回波信号;对回波信号进行处理获取雷达回波数字基带信号;

4、s2、对获取的雷达回波数字基带信号进行第一步数字基带信号处理;

5、s21、将接收到的时域的雷达信号序列进行快时间尺度上的傅里叶变换,获得雷达距离维傅里叶域信号序列;

6、s22、对雷达距离维傅里叶域信号序列进行数据压缩处理;

7、s23、通过高速数据接口将经过第一步数字基带信号处理的雷达回波数字基带中间信号传输到执行第二步数字基带处理的硬件上,并暂时存储在该硬件的存储器内;

8、s24、当时间和序列数量长度相当于整个雷达帧的雷达回波数字基带中间信号都存储到执行第二步数字基带处理的硬件上后进行下一步;

9、s3、对经过第一步数字基带信号处理的雷达回波数字基带中间信号进行第二步数字基带信号处理;

10、s31、从一个雷达帧的雷达回波数字基带中间信号中沿着慢时间维度将第一条信号序列取出,即为雷达速度维待处理信号序列;

11、s32、对雷达速度维待处理信号序列进行数据解压缩处理;

12、s33、对雷达速度维待处理信号序列进行慢时间尺度上的傅里叶变换,获得雷达速度维傅里叶域信号序列;

13、s34、对雷达速度维傅里叶域信号序列进行数据压缩处理;

14、s35、将压缩后的雷达速度维傅里叶域信号序列沿着慢时间维度存入执行第二步数字基带处理的硬件的存储器内;

15、s36、重复执行s31-s35步骤,直到此雷达帧的雷达回波数字基带中间信号的信号序列全部被取出、处理并重新存入存储器内;

16、重复执行s31时,从一个雷达帧的雷达回波数字基带中间信号中沿着慢时间维度将下一条信号序列取出,即为雷达速度维待处理信号序列。

17、优选的,s1中通过射频前端模块进行下变频、低通滤波、模数转换、校准处理将回波信号转化为雷达回波数字基带信号。

18、优选的,第一步数字基带信号处理还包括天线耦合系数消除;

19、执行s21后从雷达距离维傅里叶域信号序列减去天线耦合系数序列;该天线耦合系数序列应当是事先获取并存储在雷达回波信号处理系统当中。

20、优选的,s22中的压缩算法为块浮点算法或指数哥伦布码算法。

21、优选的,第二步数字基带信号处理包括静态分量去除;

22、执行s32后从雷达速度维待处理信号序列减去它的平均数。

23、优选的,在第二步数字基带信号处理中,若执行第二步数字基带信号处理的硬件的存储器容量足够,则可以不进行s34的数据压缩操作。

24、优选的,第二步数字基带信号处理中,根据雷达发射信号采用的复用方式,进行相应的解复用处理。

25、优选的,在第二步数字基带信号处理之后还包括恒虚警率检测和到达角检测;

26、运行恒虚警率检测和到达角检测步骤在第二步数字基带信号处理的硬件上进行或在包括第二步数字基带信号处理的硬件在内的多个硬件的合作下进行。

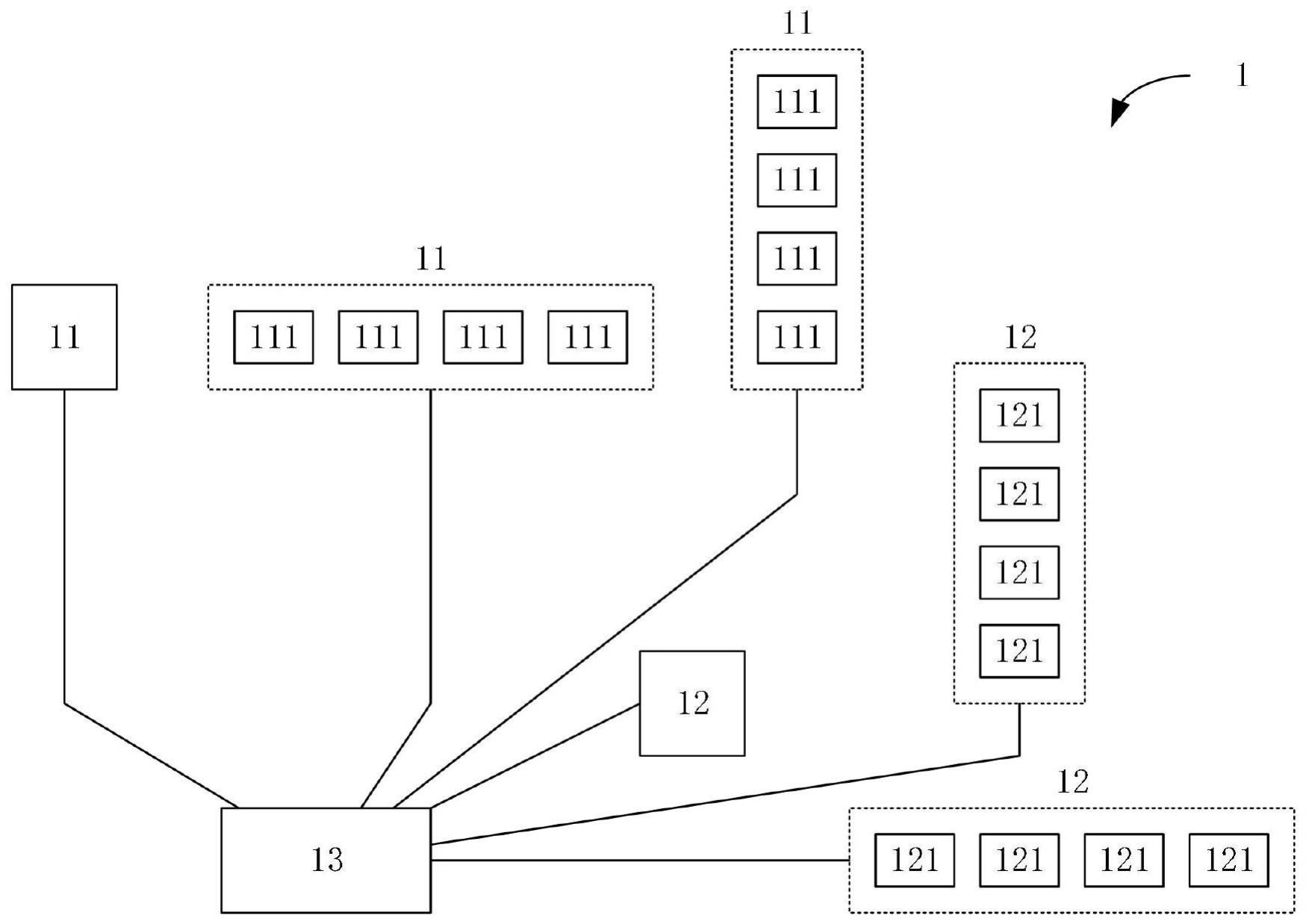

27、一种毫米波雷达回波信号处理系统,执行如权利要求1-8任一项所述的毫米波雷达回波信号处理方法,包括一个或多个发射阵列、至少一个接收阵列和至少一个信号处理器;

28、发射阵列发射的雷达波信号在经过周围环境中的探测目标反射后提供目标信息;

29、一个发射阵列包括一个或多个发射阵元;

30、每一个发射阵元可以对应于单个或复数个发射天线;

31、每一个发射阵元可以包含一个或多个相位控制单元;

32、接收阵列接收发射信号经过环境目标反射的回波信号;接收阵列检测回波信号的相位、幅度信息;

33、一个接收阵列包括一个或复数个接收阵元;

34、每一个接收阵元可以对应于单个或复数个接收天线;

35、对于每一个发射阵列或接收阵列,若它对应于多个阵元,那么其阵元间距小于或等于λ/2,其中λ为雷达波形的波长;

36、多个阵元可以排列在一条直线上,或者排列成一个平面;

37、信号处理器包含一块mmic芯片、高速数据接口和一块mcu芯片;

38、mmic芯片包含一个射频前端模块和一个hwa-mmic模块;

39、mcu芯片包含一个hwa-mcu模块和一个mcu片上存储器;

40、hwa-mmic模块和mcu片上存储器通过高速数据接口连接。

41、优选的,射频前端模块具备下变频、低通滤波、模数转换、校准功能;射频前端模块将接收到的雷达回波模拟射频信号转换为适于处理的数字基带信号;

42、hwa-mmic模块具备天线耦合系数去除、快时间尺度傅里叶变换、数据压缩功能;

43、hwa-mcu模块具备数据解压缩、数据压缩、慢时间尺度傅里叶变换、静态分量去除、雷达信号解复用、恒虚警率检测功能。

44、与现有技术相比,本发明具有如下有益的技术效果:

45、在传统雷达芯片方案中,mmic芯片将啁啾波脉冲的数字基带信号通过片间数据接口传输到硬件加速器(hwa)或dsp芯片上进行硬件信号处理;本发明将雷达回波信号的数字基带处理拆分为两部分,其中第一部分前置到mmic芯片上完成,第二部分仍旧在硬件加速器或dsp芯片上完成。第一部分数字基带信号处理中包括数据压缩的处理步骤。雷达回波信号在完成第一部分数字基带信号处理后再通过片间数据接口进行传输,和传统方案相比,大大降低了片间传输的数据量,从而增大雷达系统能够处理的基带数据规模,提升雷达探测能力。

- 还没有人留言评论。精彩留言会获得点赞!