一种半导体芯片用电性能检测装置的制作方法

1.本实用新型涉及一种检测装置,尤其涉及一种用于半导体的半导体芯片用电性能检测装置。

背景技术:

2.芯片是在电子学中是将电路(主要包括半导体设备,也包括被动组件等)小型化的方式,并时常制造在半导体晶圆表面上;在半导体芯片大规模研发及生产过程中均需要各类性能检测,而芯片测试座为测试中关键部件,芯片测试座的功能是将芯片定位后通过线路板之间电子信号电流传输从而达到测试效果,测试座的质量和匹配程度直接影响测试判断准确性。

3.目前比较常见的以pogo pin为主,pogo pin是一种应用于手机等电子产品中的精密连接器,广泛应用于半导体设备中,起连接测试作用;但是pogo pin的使用寿命比较低,容易磨损,需要经常维护更换,后期维护成本以及生产成本高,产能低下,无法满足批量化芯片的测试需求。

技术实现要素:

4.本实用新型目的是为了克服现有技术的不足而提供一种结构组成简单,测试精准可靠,便于后期更新和维护的半导体用半导体芯片用电性能检测装置。

5.为达到上述目的,本实用新型采用的技术方案是:一种半导体芯片用电性能检测装置,包括:

6.盖板,所述盖板上开有用于放置芯片的芯片限位口;

7.承载模组,设置在所述盖板的下方;

8.异形片模组,设于所述承载模组内部;

9.保护板,设于所述承载模组的下方;其中,所述盖板、承载模组以及保护板依次上下相连;

10.所述异形片模组包括两组相对设置的开尔文模组,每组开尔文模组包括多个开尔文组件;所述开尔文组件包括第一异形片和嵌设在第一异形片内的第二异形片;所述两个开尔文模组之间还设有两个第三异形片;

11.其中,所述第一异形片、第二异形片和第三异形片的的一端与芯片限位口内的芯片接触,另一端贯穿出所述保护板。

12.进一步的,所述芯片限位口设置在所述盖板的中心处。

13.进一步的,所述第一异形片包括通过第一基板相连的第一上力臂和第一下力臂,所述上力臂的前端往上延伸出一第一针尖,所述下力臂的前端往下延伸出一第一针腿;所述第一基板的上下两端分别设有第一上限位部和第一下限位部。

14.进一步的,所述第二异形片包括嵌设于所述第一上力臂和第一下力臂之间的第二基板,所述第二基板的上下两端分别设有第二上限位部和第二下限位部;所述第二基板的

一侧设有上下设置的第二上力臂和第二下力臂;其中,所述第二上力臂往上延伸出一与第一针尖相对设置的第二针尖,所述第二下力臂往下延伸出一与第一针腿相对设置的第二针腿。

15.进一步的,所述承载模组包括:

16.顶板,所述顶板内开有用于每组开尔文组件中的第一针尖和第二针尖同步穿过的第一通孔以及第三异形片的针尖通过的第二通孔,所述顶板的底部开有适配第一上限位部的第一卡槽;

17.第一层板,设于所述顶板的下表面,所述第一层板上开有用于第一基板通过的第一开口、适配第一上力臂和第二上力臂的第三通孔、适配第二上限位部的第二卡槽以及适配第三异形片的上力臂穿过的第四通孔;

18.第二层板,设于所述第一层板的下方,所述第二层板上设有用于适配第一基板的第二开口,在第二开口的一侧下方设有适配第一下力臂的导引口、适配第二下限位部的第三卡槽、用于第二上力臂和第二下力臂穿过的的第四卡槽以及适配第三异形片的下力臂穿过的第五通孔、第三异形片的基板贯穿的第六通孔;

19.底板,所述底板设于所述第二层板的下方,在所述底板上开有适配第一下限位部的第四卡槽、适配第一针腿和第二针腿穿过的第八通孔,以及适配第三异形片的针腿穿过的第九通孔。

20.进一步的,所述盖板、承载模组和保护板通过贯穿设置的螺栓和螺母进行固定。

21.由于上述技术方案的运用,本实用新型与现有技术相比具有下列优点:

22.本实用新型方案的半导体芯片用电性能检测装置,整体的结构简单紧凑,组成简单,方便制造及后期使用维护,能够直接有效的降低生产成本,提高生产效率,第二异形片内嵌在第一异形片内,异形片模组占用的空间少,节省了空间;另外增加了异形片与芯片管脚的接触性以及测试片与pcb的接触的定位精度,提高了接触的可靠性,同时异形片的寿命及测试性能的提升,且可以根据客户的测试需求调整原材料,符合实际的测试需求。

附图说明

23.下面结合附图对本实用新型技术方案作进一步说明:

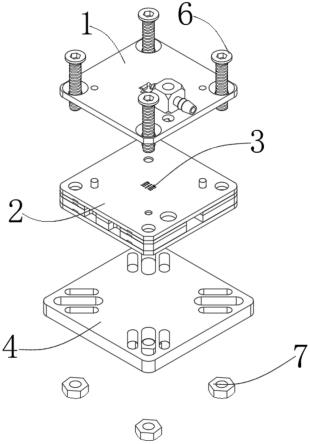

24.图1为本实用新型一实施例的立体结构分解示意图;

25.图2为本实用新型一实施例的俯视图;

26.图3为图2中的a部放大图;

27.图4为图2中c-c的局部剖视图;

28.图5为图5中的b部放大图;

29.图6为本实用新型一实施例中装配有异形片模组的承载模组的立体结构分解示意图;

30.图7为图6中的e部放大图;

31.图8为本实用新型一实施例中开尔文组件的主视图;

32.图9为图6中的d部放大图;

33.图10为图6中的f部放大图;

34.图11为本实用新型一实施例中略去顶板后承载模组装配有两个开尔文组件时的

结构示意图;

35.图12为本实用新型一实施例中第二层板的立体结构示意图;

36.图13为本实用新型一实施例中底板的立体结构示意图;

37.其中:盖板1、承载模组2、异形片模组3、保护板4、芯片5、螺栓6、螺母7、芯片限位口10、顶板20、第一层板21、第二层板22、底板23、开尔文组件30、第一异形片31、第二异形片32、第三异形片33、第一通孔200、第二通孔201、第一卡槽202、第一开口210、第三通孔211、第二卡槽212、第四通孔213、第二开口220、第三卡槽221、第五通孔222、第六通孔223、第七通孔224、第四卡槽230、第八通孔231、第九通孔232、第一基板310、第一上力臂311、第一下力臂312、第一针尖313、第一针腿314、第一上限位部315、第一下限位部316、第二基板320、第二上力臂321、第二下力臂322、第二针尖323、第二针腿324、第二上限位部325、第二下限位部326。

具体实施方式

38.下面结合附图及具体实施例对本实用新型作进一步的详细说明。

39.参阅图1-3,本实用新型一实施例所述的一种半导体芯片用电性能检测装置,包括盖板1、承载模组2、异形片模组3和保护板4;盖板1、承载模组2、异形片模组3和保护板4通过贯穿设置的多个螺栓6和螺母7依次上下固定在一起;盖板1上开有芯片限位口10,芯片5放置在芯片限位口10内,本实施例中的整体结构简单,方便后期维护和更换不同的部件;本实施例中,芯片限位口10设置在盖板1的中心处。

40.参阅4-7,异形片模组3设置在承载模组2的内部,异形片模组3包括两组相对垂直设置的开尔文模组,每组开尔文模组包括四个平行设置的开尔文组件30,每个开尔文组件30包括第一异形片31和嵌设在第一异形片31内的第二异形片32;另外在两个开尔文模组之间还设有两个垂直设置的第三异形片33,本实施例中的第一异形片21与第三异形片33的结构相同。

41.参阅图8,第一异形片31包括通过第一基板310上下设置的第一上力臂311和第一下力臂312,上力臂311的前端往上延伸出一第一针尖313,下力臂312的前端往下延伸出一第一针腿314;在第一基板310的上下两端分别设有第一上限位部315和第一下限位部316。

42.第二异形片32包括第二基板320,第二基板320设置在第一上力臂311和第一下力臂312之间,第二基板320的上下两端分别设有第二上限位部325和第二下限位部326;第二基板320的一侧设有上下设置的第二上力臂321和第二下力臂322;第二上力臂321往上延伸出一与第一针尖313相对设置的第二针尖323,第二下力臂322往下延伸出一与第一针腿314相对设置的第二针腿324;由于第二异形片32嵌设在第一异形片31的内部,这样就有效的优化了异形片模组3的结构,节省了异形片模组3在承载模组2内占用的空间。

43.参阅5-6和9-13,承载模组2包括依次上下相连设置的顶板20、第一层板21、第二层板22和底板23;顶板20内开有用于每组开尔文组件中的第一针尖313和第二针尖323同步穿过的第一通孔200,第一通孔200包括两列,每列包括四个平行设置的四个第一通孔200,与开尔文组件30对应设置。

44.另外,顶板20上还开有用于两个第三异形片33的针尖通过的两个垂直设置的第二通孔201;同时,在顶板20的底部开有适配第一异形片31中第一上限位部315的第一卡槽

202。

45.第一层板21连接在顶板20的下表面上,在第一层板21上开有用于第一基板310通过的第一开口210以及适配第一上力臂311和第二上力臂321的第三通孔211,第三通孔211一共有两列,每列包括四个平行设置的第三通孔;适配第二上限位部325的第二卡槽212以及适配两个第三异形片33穿过的垂直设置的两个第四通孔213。

46.第二层板22连接在第一层板21的下方,在第二层板22上设有用于适配第一基板的第二开口220,在第二开口220的一侧下方设有适配第一下力臂的导引口225,以及适配第二下限位部的第三卡槽221,用于第二上力臂和第二下力臂穿过的第四卡槽222,适配第三异形片力臂的第五通孔224以及基板的第六通孔223。

47.底板23连接在第二层板22的下方,在底板23上开有适配第一下限位部的第四卡槽230、适配第一针腿和第二针腿的第八通孔231,以及适配第三异形片232的针腿穿过的第九通孔232。

48.参阅图5,其为异形片模组3中的单个开尔文组件安装到承载模组2时的结构示意图:第一异形片31的第一基板310从上往下竖向设置在第一开口210和第二开口220内,并且对应的第一上限位部315和第一下限位部316分别设置在第一卡槽202和第四卡槽230;同时第一下力臂312沿着导引口225往下,使得第一针腿314卡设在第八通孔231内后穿出,而第一上力臂311沿着第一层板上的第三通孔211往上伸出后,第一针尖313从第一通孔200内穿出与芯片5接触。

49.在第二异形片32中,第二基板320的第二上限位部325和第二下限位部326分别卡设在第二卡槽212和第三卡槽221内进行固定;同时第二下力臂322往下延伸穿过第四卡槽222和导引口225后,第二针腿314从第八通孔231内卡设后穿出;而第二上力臂321从上沿着第四卡槽222往上延伸,然后第二针尖323从第一通孔200内穿出与芯片5接触,并与第一针尖313相对设置;本实施例中的第一针腿和第二针腿从保护板穿出后与pcb测试板相接触,从而对芯片进行相关的性能检测。

50.由于第三异形片33的结构与第一异形片31相同,这样将两个第三异形片的安装到承载模组时的结构为:第三异形片33的基板贯穿设置在第六通孔223内,然后第三异形片的下力臂穿过第七通孔224过后,第三异形片33的针腿从第九通孔232内穿出后与pcb板接触,而第三异形片33的上力臂穿过第四通孔213后,第三异形片33的针腿从第二通孔201内穿出,并与后续的pcb测试板相通。

51.具体的,通过上述对三个异形片结构描述,可以发现三个异形片构成的异形片模组,其整体结构占用空间少,并且三个异形片的结构紧凑,对应的针尖和针腿能够与芯片和pcb测试板有更好的接触,接触稳定,且定位精度高,符合实际的测试需求;另外,本施例中的三个异形片的均采用高耐磨超导合金材质以及力学原理结构,提升了使用性能和寿命。

52.本实用新型的半导体芯片用电性能检测装置,整体的结构简单紧凑,组成简单,方便制造及后期使用维护,能够直接有效的降低生产成本,提高生产效率,第二异形片内嵌在第一异形片内,异形片模组占用的空间少,节省了空间;另外增加了异形片与芯片管脚的接触性以及测试片与pcb的接触的定位精度,提高了接触的可靠性,同时异形片的寿命及测试性能的提升,且可以根据客户的测试需求调整原材料,符合实际的测试需求。

53.以上仅是本实用新型的具体应用范例,对本实用新型的保护范围不构成任何限

制。凡采用等同变换或者等效替换而形成的技术方案,均落在本实用新型权利保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1