一种TPC探测器的前端读出电子学电路

本发明涉及核技术应用领域,特别是关于一种tpc(时间投影室)探测器的前端读出电子学电路。

背景技术:

1、重离子碰撞实验是实验室研究冷密核物质性质近乎唯一的手段。低温高密核物质测量谱仪(csr external-target experiment,cee)将是中国第一台运行于gev能区的、完全自主研制的大型核物理实验装置。该谱仪研制完成后,将运行于兰州重离子研究装置(hirfl)40mev低温能区的重粒子碰撞实验中,从而促进低温和高重子数密度条件下核物质的相结构、高密低温时的非对称核物质状态方程等问题的研究。

2、cee由大型磁铁和多种探测器组成,作为核心探测器之一的tpc,具有高接受度、高计数率和大面积的特点,用于实现π、p、d、t、3he、4he等轻带电粒子的测量以及三维径迹的精确重构。为了实现上述物理目标,对配套读出电子学的设计指标要求是:1)模拟测量通道15000路;2)mip约为1.4fc;3)动态范围为:1.2fc~100fc;4)最高可处理事例率高达20khz。

3、然而,现有技术中并没有满足上述全部指标的可处理128路tpc探测器输入信号的前端读出电子学电路。

技术实现思路

1、针对上述问题,本发明的目的是提供一种能够处理128路tpc探测器输入信号的tpc探测器的前端读出电子学电路。

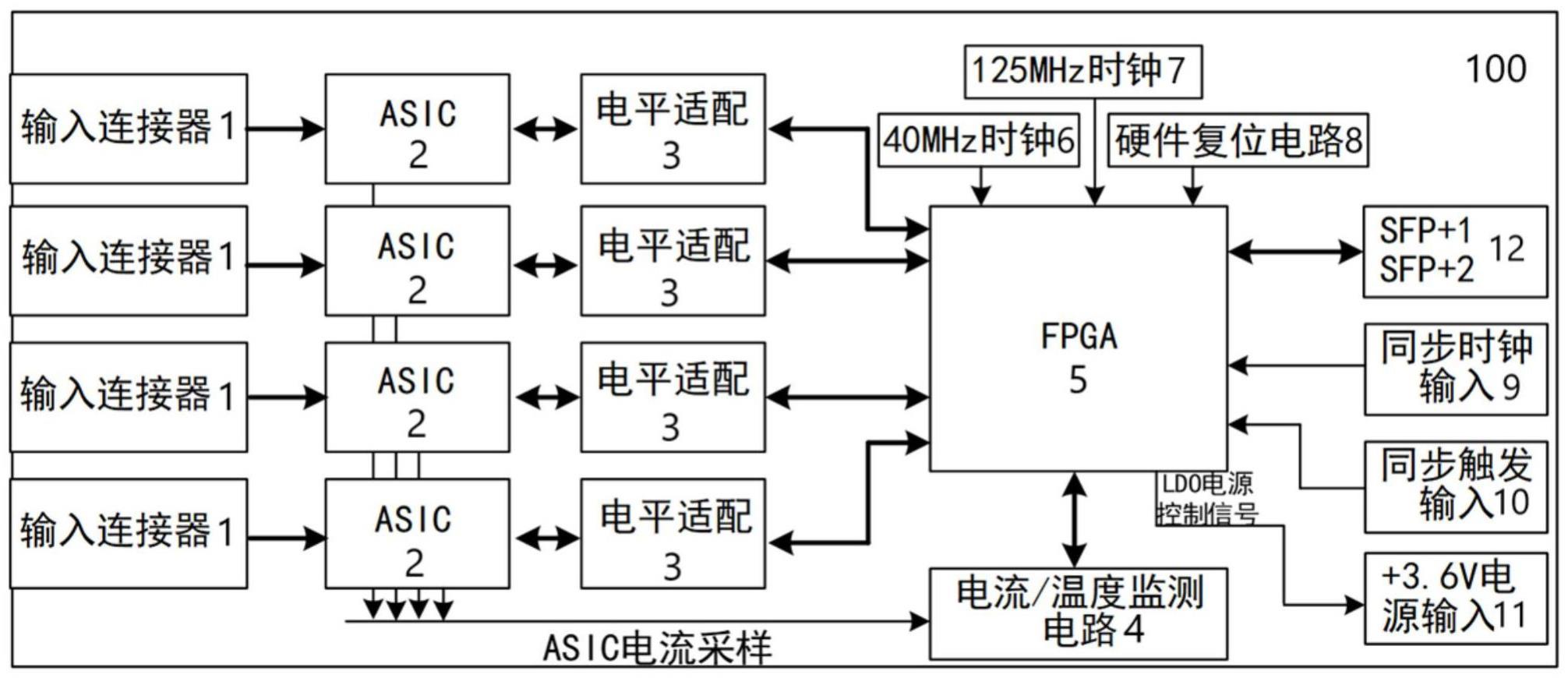

2、为实现上述目的,本发明采取以下技术方案:第一方面,提供一种tpc探测器的前端读出电子学电路,包括输入连接器、asic芯片、电平适配转换模块、电流和温度监测电路、fpga芯片、时钟电路、硬件复位电路以及电源输入接口;

3、若干所述输入连接器分别连接tpc探测器,用于获取tpc探测器输出的模拟信号;

4、若干所述asic芯片分别连接对应所述输入连接器,用于基于触发模式,对对应所述输入连接器获取的模拟信号进行采样和数据处理,对处理后的探测器数据组帧并输出串行链路数据至对应所述电平适配转换模块;

5、所述电流和温度监测电路用于实时监测每一所述asic芯片和fpga芯片供电管脚的电流信号和壳体温度信号;

6、所述fpga芯片用于对所述asic芯片进行配置,确定所述asic芯片的触发模式;对所述电平适配转换模块发送的串行链路数据进行数据处理;

7、所述时钟电路用于为所述fpga芯片提供工作时钟;

8、所述硬件复位电路用于进行硬件初始化;

9、所述电源输入接口用于连接电源,为该前端读出电子学电路的各用电部件进行供电。

10、进一步地,还包括同步时钟输入接口、同步触发输入接口和sfp光纤接口;

11、所述同步时钟输入接口用于从外部输入同步时钟,实现全部前端读出电子学电路之间的时间戳同步;

12、所述同步触发输入接口用于当前端读出电子学电路配置在有触发的触发模式时从外部输入有效触发信号;

13、所述sfp光纤接口用于连接光纤介质,将缓存在所述fpga芯片内的数据处理后的串行链路数据输出至后端daq电路。

14、进一步地,所述asic芯片的数量为四个,每一所述asic芯片内均设置有:

15、32路模拟输入通道,用于获取对应所述输入连接器获取的tpc探测器输出的1路模拟信号;

16、32个模拟信号处理单元,用于对tpc探测器输出的1路模拟信号进行放大和整形处理,输出处理后的模拟信号;

17、32个adc电路,用于对各所述模拟输入通道输入的tpc探测器输出信号进行模数转换;

18、32个数字信号处理单元,用于对模数转换后的tpc探测器数据组成子包帧头和子包数据,并输出组帧后的tpc探测器数据;

19、11条异步差分串行链路,用于将组帧后的tpc探测器数据即串行链路数据输出至电平适配转换模块。

20、进一步地,所述fpga芯片内设置有复位管理模块、指令收发模块、驱动模块、触发判选模块、同步时钟管理模块、系统时钟管理模块、探测器数据管理模块、探测器数据轮询发送模块和遥测轮询模块;

21、所述复位管理模块用于接收硬件复位信号或复位控制信号,生成异步硬件复位信号,并发送至所述fpga芯片内的其他模块以及所有所述asic芯片;

22、所述指令收发模块用于接收配置或控制指令,进行判选后提取配置参数和生成控制信号,并输出至所述fpga芯片内对应的功能模块;以及当接收到查询指令后,读取应答状态参数,组成应答指令帧;

23、所述驱动模块用于对全部所述asic芯片进行配置和控制;

24、所述触发判选模块用于通过所述同步触发输入接口接收触发信号,进行有效性判选和脉宽处理后扇出至所有所述asic芯片,使得所述asic芯片进入一次数据采集和处理过程;

25、所述同步时钟管理模块用于根据外部输入的同步时钟,生成整个前端读出电子学电路使用的同步时间戳并向所述探测器数据轮询发送模块提供时间戳数据;以及向所述触发判选模块提供触发信号;

26、所述系统时钟管理模块用于接收本地时钟,并通过内部的数字锁相环电路,生成不同频率的工作时钟;

27、所述探测器数据管理模块用于当接收到启动采集指令后,控制所述asic芯片处于工作状态并接收所述asic芯片的串行链路数据,进行处理后得到tpc探测器的缓存数据;

28、所述探测器数据轮询发送模块用于实时轮询缓存数据,读取非空缓存数据并发送所述至光纤通信模块;

29、所述遥测轮询模块用于实时获取每一所述asic芯片和fpga芯片供电管脚的电流信号和壳体温度信号,并进行模数转换。

30、进一步地,所述fpga芯片内还设置有断电保护模块,用于从所述遥测轮询模块实时获取每一所述asic芯片供电管脚的电流信号并与预先设定的断电阈值进行对比,若电流信号连续超过断电阈值预设次数,则控制所述asic芯片断电。

31、进一步地,所述探测器数据管理模块的数量为四个,每一所述探测器数据管理模块内均设置有:

32、11个串并转换模块,用于基于配置或控制指令,同时接收对应所述asic芯片的串行链路数据,进行串并转换、校验筛选和合并后得到并行数据;

33、11个一级缓存写控制模块,用于对对应所述串并转换模块输出的并行数据进行判读校验,如果判断出并行数据的数据格式和数值正确,则将若干并行数据进行合并后输出至对应一级fifo模块中进行缓存,直到该所述异步差分串行链路输出的数据完毕为止;

34、3个一级读出二级写入控制模块,用于汇总合并多个所述一级fifo模块中的数据,并转存至二级fifo模块。

35、第二方面,提供一种128路读出验证系统,包括:

36、如权利要求1至6任一项所述的tpc探测器的前端读出电子学电路;

37、触发子系统,用于向所述tpc探测器的前端读出电子学电路提供输入信号和触发信号;

38、工控机,用于配置所述tpc探测器的前端读出电子学电路为无触发模式和有触发模式两种触发模式;

39、daq电路,用于发送配置或控制指令至所述tpc探测器的前端读出电子学电路,以及接收所述tpc探测器的前端读出电子学电路发送的tpc探测器的缓存数据、每一asic芯片和fpga芯片供电管脚的电流信号和壳体温度信号。

40、第三方面,提供一种128路读出验证系统的使用方法,包括:

41、构建如权利要求7所述的128路读出验证系统;

42、对前端读出电子学电路中的fpga芯片进行全局复位后,等待接收daq电路下发的配置或控制指令;

43、daq电路下发触发模式配置指令至fpga芯片,fpga芯片解析后输出至asic芯片,确定asic芯片的触发模式;

44、daq电路下发asic同步指令至fpga芯片,fpga芯片解析后输出至asic芯片,进行fpga芯片与asic芯片的同步;

45、daq电路下发启动采集指令至fpga芯片,fpga芯片解析后产生启动采集控制信号,使得fpga芯片处于等待接收asic芯片串行链路数据状态;

46、各asic芯片根据配置的触发模式,对tpc探测器输出的模拟信号进行处理后通过电平适配转换模块输出至fpga芯片;

47、fpga对电平适配转换模块输出的串行链路数据进行数据处理后输出至daq电路;

48、daq电路对接收的数据进行二次汇总后转发至工控机,完成一次触发信号的数据处理过程;

49、实验结束时,daq电路下发停止采集指令至fpga芯片,fpga芯片解析后产生停止采集控制信号至fpga芯片,前端读出电子学电路停止工作。

50、进一步地,还包括:

51、在tpc探测器的数据处理过程中,fpga芯片中的遥测轮询模块并行运行,不断将每一asic芯片和fpga芯片供电管脚的电流信号和壳体温度信号进行缓存,并连续刷新,当接收到遥测轮询指令后,将最新的状态参数填入应答帧后上行反馈至工控机。

52、进一步地,还包括:

53、当某一asic芯片在运行过程中因出现单粒子闩锁现象而导致芯片功耗异常增大、并保持功耗过载状态时,fpga芯片中的断电保护模块监测到该异常状态后,对异常asic芯片进行断电;在确认排除异常后,通过指令再次使得该asic芯片重新单独上电,继续工作。

54、本发明由于采取以上技术方案,其具有以下优点:

55、1、本发明采用的asic芯片可对输入的tpc探测器信号采样处理后,直接输出带有通信协议帧的数据包至fpga芯片,从而能够省却外置adc芯片及相关电路,进一步提高电路集成度,实现装置小型化和低功耗设计目标。

56、2、本发明最高可处理粒子事件率达到50khz,且支持连续无触发模式,满足tpc探测器在更高流强下的信号处理与读出需求,同时,为了兼容现有读出电子学架构,还支持传统的有触发模式,能够全波形记录绝大部分有效事件,进一步提升数据精度和探测器系统粒子鉴别能力。

57、3、本发明由于设置有asic芯片,支持过阈零压缩功能和脉冲积分求和零压缩功能,能够滤除大部分无效数据,从而提高有效数据传输带宽。

58、4、本发明的fpga芯片设置有光纤通信模块,传输带宽达到3.125gbps,能够满足在无触发全波形采样模式下,大块数据高速实时传输的需求。

59、5、本发明设计有多重硬件保护和固件数据检错机制,可靠性和安全性较高,环境适应性强。

60、6、由于粒子束团中会偶尔含有高能粒子而产生过载信号,致使asic芯片发生深度饱和甚至是闩锁效应,从而导致其功耗异常增大,为避免asic芯片长时间功率过载造成工作异常甚至烧毁,本发明设置有电流和温度监测电路监测每一asic芯片供电管脚的电流信号和温度信号,电流信号由fpga芯片实时读取,当fpga芯片监测到过载电流,则直接控制asic芯片断电,从而起到保护作用。

61、7、本发明的硬件设计集成度更高,能耗更低,安全性和可靠性高、工作适应性强。

62、8、本发明的fpga芯片除接收和处理asic芯片输出的tpc探测器数据外,还实现对全部asic芯片的配置、电源控制、温度及电流监测等功能。另外,fpga芯片还能够灵活的使能asic芯片的工作通道,从而最大限度的节省功耗。

63、综上所述,本发明可以广泛应用于tpc探测器中。

- 还没有人留言评论。精彩留言会获得点赞!