伪差分电容检测电路及检测方法与流程

本发明属于电容检测,具体涉及一种伪差分电容检测电路及检测方法。

背景技术:

1、现有技术中电容检测系统通常采用基准电压对待检测电容进行充电,然后使用积分器将电容信息转化为积分器输出的电压信号,最后使用一个adc将电压信号转换成数字信号输出。这样的结构工作原理清晰,利于分析各个部分的影响,但是测试流程复杂,需要等待前一个阶段完成之后才能进行下一个阶段的处理,这样就降低了整个系统的工作速度,增加了系统的平均功耗,并且积分器的输出电压与积分电容相关,积分电容会存在工艺上的偏差,导致电压和电容的对应关系存在增益误差。

2、另一种检测速度较快的电容检测系统需要用到片外的cmod电容作为积分电容来量化被检测的电容,并且比较器检测点位于cmod的上极板,容易受到外部干扰信号的影响。

3、因此,针对上述技术问题,有必要提供一种伪差分电容检测电路及检测方法。

技术实现思路

1、有鉴于此,本发明的目的在于提供一种伪差分电容检测电路及检测方法,以对待测电容进行量化检测。

2、为了实现上述目的,本发明一实施例提供的技术方案如下:

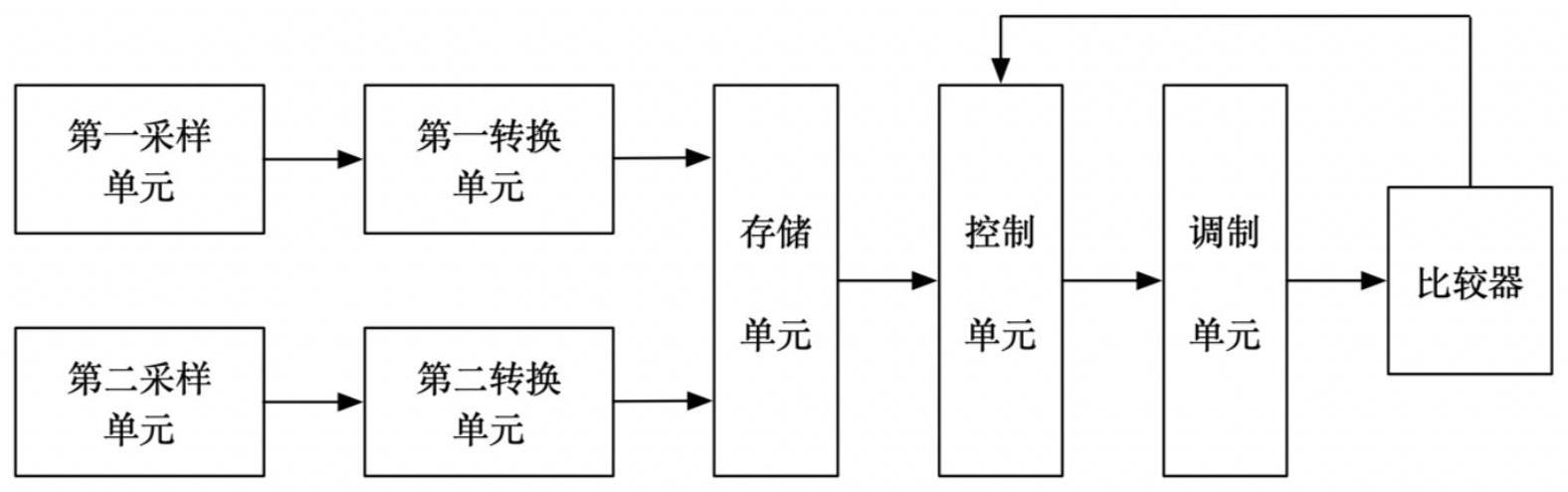

3、一种伪差分电容检测电路,所述电路包括:

4、第一采样单元,包括与参考电容cf分别相连的第一充电单元及第一电荷转移单元,第一充电单元包括用于对参考电容cf进行充电,第一电荷转移单元用于向参考电容cf注入和/或抽取电荷;

5、第二采样单元,包括与待测电容cs分别相连的第二充电单元及第二电荷转移单元,第二充电单元包括用于对待测电容cs进行充电,第二电荷转移单元用于向待测电容cs注入和/或抽取电荷;

6、第一转换单元,用于将参考电容cf上的电荷信号转换为第一电压信号;

7、第二转换单元,用于将待测电容cs上的电荷信号转换为第二电压信号;

8、存储单元,包括与第一转换单元相连的第一存储电容cm1及与第二转换单元相连的第二存储电容cm2,分别用于存储第一电压信号和第二电压信号;

9、调制单元,包括第一调制电容cmod1及第二调制电容cmod2;

10、控制单元,连接于存储单元和调制单元之间,包括若干开关;

11、比较器,第一输入端和第二输入端分别与第一调制电容cmod1及第二调制电容cmod2相连,输出端与控制单元相连,所述比较器根据第一调制电容cmod1及第二调制电容cmod2的调制后的电压获取控制信号,以控制所述控制单元。

12、一实施例中,所述第一充电单元包括第一开关s1,第一开关s1的第一端与参考电压vref相连,第二端与参考电容cf的第一端相连,参考电容cf的第二端与地电位相连;

13、所述第二充电单元包括第二开关s2,第二开关s2的第一端与参考电压vref相连,第二端与待测电容cs的第一端相连,待测电容cs的第二端与地电位相连。

14、一实施例中,所述第一电荷转移单元包括第一电荷注入单元及第一电荷抽取单元;所述第一电荷注入单元包括第一电流源idac1及第三开关s3,第一电流源idac1的输入端与电源电压相连,输出端与第三开关s3的第一端相连,第三开关s3的第二端与参考电容cf的第一端相连;第一电荷抽取单元包括第二电流源idac2及第四开关s4,第四开关s4的第一端与参考电容cf的第一端相连,第二端与第二电流源idac2的输入端相连,第二电流源idac2的输出端与地电位相连;

15、所述第二电荷转移单元包括第二电荷注入单元及第二电荷抽取单元;所述第二电荷注入单元包括第三电流源idac3及第五开关s5,第三电流源idac3的输入端与电源电压相连,输出端与第五开关s5的第一端相连,第五开关s5的第二端与待测电容cs的第一端相连;第二电荷抽取单元包括第四电流源idac4及第六开关s6,第六开关s6的第一端与待测电容cs的第一端相连,第二端与第四电流源idac4的输入端相连,第四电流源idac4的输出端与地电位相连。

16、一实施例中,所述第三电流源idac3提供的第三电流为第一电流源idac1提供的第一电流的n倍,所述第四电流源idac4提供的第四电流为第二电流源idac2提供的第二电流的n倍,n为电容补偿倍数。

17、一实施例中,所述第一转换单元包括第一缓冲器、第七开关s7及第八开关s8,所述第七开关s7的第一端与参考电容cf的第一端相连,第二端与第一缓冲器的第一输入端相连,第一缓冲器的第二输入端及输出端分别与第八开关s8的第一端相连;

18、所述第二转换单元包括第二缓冲器、第九开关s9及第十开关s10,所述第九开关s9的第一端与待测电容cs的第一端相连,第二端与第二缓冲器的第一输入端相连,第二缓冲器的第二输入端及输出端分别与第十开关s10的第一端相连;

19、所述第一存储电容cm1的第一端与第八开关s8的第二端相连,第二端与地电位相连;

20、所述第二存储电容cm2的第一端与第十开关s10的第二端相连,第二端与地电位相连。

21、一实施例中,所述控制单元包括第十一开关s11、第十二开关s12、第十三开关s14及第十四开关s14;

22、所述第十一开关s11的第一端与第一存储电容cm1的第一端相连,第二端与第一调制电容cmod1的第一端相连;

23、所述第十二开关s12的第一端与第一存储电容cm1的第一端相连,第二端与第二调制电容cmod2的第一端相连;

24、所述第十三开关s13的第一端与第二存储电容cm2的第一端相连,第二端与第一调制电容cmod1的第一端相连;

25、所述第十四开关s14的第一端与第二存储电容cm2的第一端相连,第二端与第二调制电容cmod2的第一端相连;

26、所述第一调制电容cmod1的第二端和第二调制电容cmod2的第二端均与地电位相连。

27、一实施例中,所述电路还包括与比较器相连的d触发器,所述比较器的第一输入端与第一调制电容cmod1的第一端相连,第二输入端与第二调制电容cmod2的第一端相连,所述比较器的输出端与d触发器的输入端d相连,所述d触发器的输出端q用于输出控制信号以控制第十三开关s13和/或第十四开关s14。

28、一实施例中,所述第一存储电容cm1、第二存储电容cm2、第一调制电容cmod1及第二调制电容cmod2均为片内电容,参考电容cf为片内电容或片外电容。

29、一实施例中,所述第一存储电容cm1、第二存储电容cm2、第一调制电容cmod1、第二调制电容cmod2、参考电容cf及待测电容cs满足:

30、cmod1<cs,cmod2<cs;

31、cmod1/cm1≥100;

32、cmod2/cm2≥100;

33、cmod1/(cm1+cf)=0.1~10;

34、cmod2/(cm2+cs)=0.05~10;

35、cmod1/(cm2+cs)=0.05~10;

36、cmod2/(cm1+cf)=0.1~10。

37、一实施例中,所述第一存储电容cm1、第二存储电容cm2、第一调制电容cmod1、第二调制电容cmod2、参考电容cf及待测电容cs的大小分别为:

38、cs=0~200pf;

39、cf=5~50pf;

40、cm1=cm2=10~1000ff;

41、cmod1=cmod2=1~100pf。

42、一实施例中,所述待测电容cs的大小为:cs=dutycycle(q)*cf*(n+1),其中,dutycycle(q)为比较器输出的控制信号的占空比,电容补偿倍数n=idac3/idac1=idac4/idac2。

43、本发明另一实施例提供的技术方案如下:

44、一种伪差分电容检测方法,所述方法包括:

45、分别对参考电容cf和待测电容cs进行充电;

46、分别向参考电容cf和待测电容cs注入或抽取电荷;

47、将参考电容cf上的电荷信号及待测电容cs上的电荷信号分别转换为第一电压信号和第二电压信号,并分别存储于第一存储电容cm1和第二存储电容cm2中;

48、将第一存储电容cm1和第二存储电容cm2中的电荷转移至第一调制电容cmod1或第二调制电容cmod2中,通过第一调制电容cmod1及第二调制电容cmod2分别对第一电压信号及第二电压信号进行调制;

49、对第一调制电容cmod1及第二调制电容cmod2中的电压信号进行比较,获取控制信号q;

50、根据控制信号q的占空比、参考电容cf、及注入或抽取电荷的电流比获取待测电容cs的大小。

51、一实施例中,所述方法包括若干量化周期,每个量化周期包括以下步骤:

52、分别对参考电容cf和待测电容cs进行充电;

53、通过第一电流和第三电流分别向参考电容cf和待测电容cs注入电荷;

54、将参考电容cf上的电荷信号及待测电容cs上的电荷信号分别转换为第一电压信号和第二电压信号,并分别存储于第一存储电容cm1和第二存储电容cm2中;

55、将第一存储电容cm1和第二存储电容cm2中的电荷分别转移至第一调制电容cmod1和第二调制电容cmod2中,通过第一调制电容cmod1及第二调制电容cmod2对第一电压信号及第二电压信号进行调制;

56、对第一调制电容cmod1及第二调制电容cmod2中的电压信号进行比较,获取控制信号q1;

57、分别对参考电容cf和待测电容cs进行充电;

58、通过第二电流和第四电流分别向参考电容cf和待测电容cs抽取电荷;

59、将参考电容cf上的电荷信号及待测电容cs上的电荷信号分别转换为第一电压信号和第二电压信号,并分别存储于第一存储电容cm1和第二存储电容cm2中;

60、将第一存储电容cm1和第二存储电容cm2中的电荷分别转移至第二调制电容cmod2和第一调制电容cmod1中,通过第二调制电容cmod2及第一调制电容cmod1分别对第一电压信号及第二电压信号进行调制;

61、对第一调制电容cmod1及第二调制电容cmod2中的电压信号进行比较,获取控制信号q2。

62、一实施例中,所述方法还包括:

63、若控制信号q1为高电平,则通过第一调制电容cmod1及第二调制电容cmod2分别对第一电压信号及第二电压信号进行调制;若控制信号q1为低电平,则通过第一调制电容cmod1对第一电压信号进行调制;及,

64、若控制信号q2为高电平,则通过第二调制电容cmod2及第一调制电容cmod1分别对第一电压信号及第二电压信号进行调制;若控制信号q2为低电平,则通过第二调制电容cmod2对第一电压信号进行调制。

65、一实施例中,所述待测电容cs的大小为:cs=dutycycle(q)*cf*(n+1),其中,dutycycle(q)为比较器输出的控制信号q的占空比,电容补偿倍数n=idac3/idac1=idac4/idac2,idac1、idac2、idac3、idac4分别为第一电流、第二电流、第三电流及第四电流的大小,这四个电流均可以从idac阵列中按照不同的比值选取出来。

66、本发明具有以下有益效果:

67、本发明中的电容检测电路及检测方法采用伪差分结构,对于共模干扰具备很强的抑制能力,保证了芯片性能,提高了检测精度;

68、另外,参考电容、存储电容及调制电容均为片内电容,避免了片外电容易受外部干扰的问题,减少了该模块所需要的pad数量。

- 还没有人留言评论。精彩留言会获得点赞!