一种用于功率器件的dv/dt耐受能力测试电路及方法

本发明涉及功率半导体器件,尤其涉及一种用于功率器件的dv/dt耐受能力测试电路及方法。

背景技术:

1、功率半导体器件作为电力电子装置的核心器件,保证其高可靠性、高性能和低能耗运行至关重要。碳化硅mosfet由于其优异的性能优势近十年里得到迅速发展,广泛应用于新能源产业。由于碳化硅mosfet开关速度快,开关转换时间仅为几十纳秒的数量级,导致其在开关瞬间存在很高的漏极电压变化率(dv/dt)和漏极电流变化率(di/dt)。开关和机器所经历的高dv/dt会在一定时间内降低绕组绝缘能力或导致器件边缘终端退化。同时高dv/dt可能引起电路中功率器件的误导通,导致输入电源对地短路,产生大的击穿电流,导致器件损坏。

2、功率器件的dv/dt耐受能力测试电路需要产生非常高的dv/dt值并对被测器件高dv/dt冲击耐受情况进行检测。现有一种用于功率半导体器件dv/dt测试的模块化marx发生器,测试电路结构如图1所示,该测试电路通过多个模块化的功率mosfet实现dv/dt值可调。利用二极管单向导电性,通过控制mosfet的开关状态实现多个电容串、并连连接的状态切换,使得多个电容两端电压发生堆叠,产生很高的电压瞬态变化和可定制调节的高dv/dt值。如图2所示,公开了一种新型电路结构,利用雪崩bjt二次击穿产生极高dv/dt用以评估高dv/dt对碳化硅mosfet的影响,由顶部的电容存储电压脉冲能量,四个硅雪崩三极管(bjt)图腾柱配置堆叠,通过控制最上方雪崩bjt导通使得下方3个雪崩bjt发生二次击穿,产生所需的高dv/dt。通过输出电路的两个肖特基二极管形成“or”电路结构,使得漏源极偏置电压能迅速施加到被测器件。如图3所示,公开了一种用于在被测器件上感应出高dv/dt的测试电路,该测试电路通过强制使电容c2的一端接地,使得电容两端电压迅速施加到被测器件两端,得到很大的dv/dt电压脉冲。所得dv/dt仅受到主电路寄生参数限制,并且很大程度上由电容c2两端电压和mosfet(q1)导通速度决定。

3、对于图1的技术方案,其在要求母线电压恒定的情况下产生的dv/dt最大值受到mosfet的开通速度限制,所能产生的dv/dt值较小,图2和图3的技术方案使用了雪崩bjt,可实现的dv/dt值可调节性较差,而且,为了评估被测器件的dv/dt耐受能力,上述技术方案都需要使用超高精度的示波器和电压探头,对测试设备精度要求非常高,成本高昂。

4、需要说明的是,在上述背景技术部分公开的信息只用于加强对本公开的背景的理解,因此可以包括不构成对本领域普通技术人员已知的现有技术的信息。

技术实现思路

1、本发明的目的在于克服现有技术的缺点,提供了一种用于功率器件的dv/dt耐受能力测试电路及方法,解决了现有技术存在的问题。

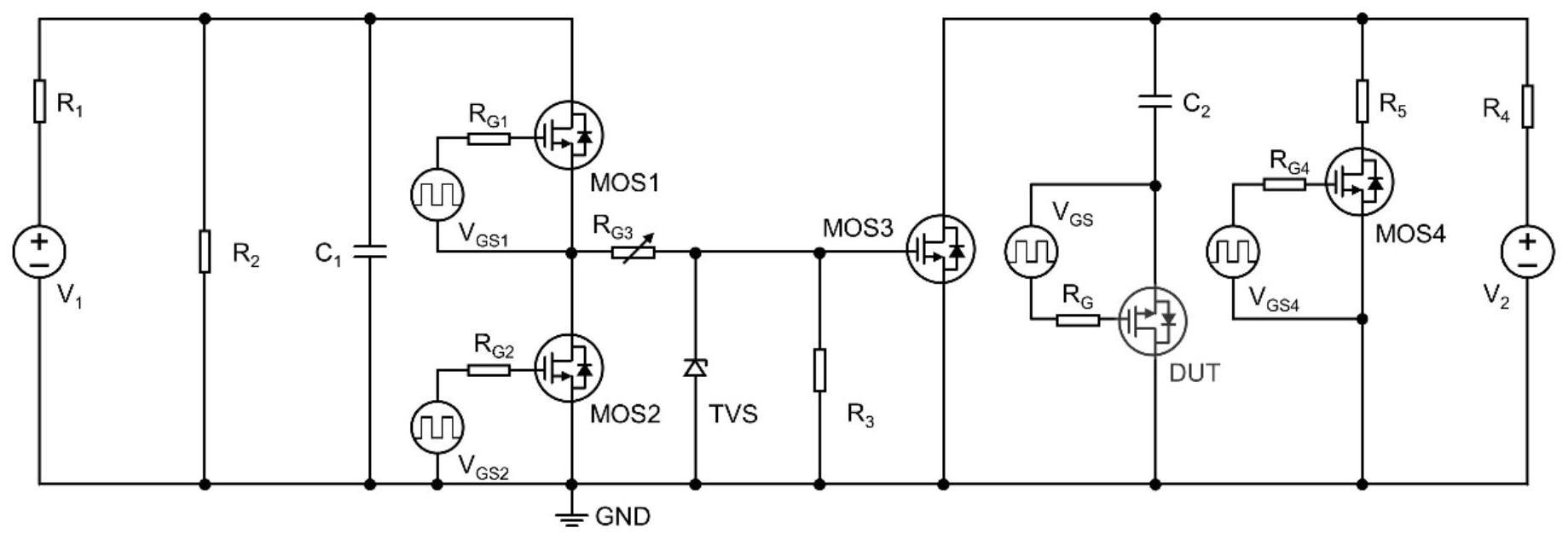

2、本发明的目的通过以下技术方案来实现:一种用于功率器件的dv/dt耐受能力测试电路,它包括栅极大电流驱动电路和主电路;所述主电路包括开关管mos3、被测器件dut、驱动脉冲发生器vgs、电容c2、电阻rg和r4,以及高压直流电压源v2;高压直流电压源v2的正极通过电阻r4连接开关管mos3的漏极,负极接地;所述驱动脉冲发生器vgs一端通过电阻rg与被测器件dut栅极连接,另一端与被测器件dut源极连接;被测器件dut的漏极与开关管mos3的源极均接地,源极通过电容c2与开关管mos3的漏极连接;

3、所述栅极大电流驱动电路与所述开关管mos3的栅极连接,用于给开关管mos3内部的寄生电容充电和放电,使开关管mos3快速开通和关断,并泄放瞬时过电流防止大栅极电压击穿开关管mos3的栅极,将开关管mos3的栅极电压钳制在安全值,以及调节开关管mos3的开通速度,从而调节主电路dv/dt的大小;在开关管mos3开通的瞬间,电容c2与mos3相连的一端被强制接地,使得电容c2两端电压被迅速施加到被测器件dut的漏极和源极两端,进而产生大的dv/dt脉冲电压对被测器件dut的dv/dt耐受能力进行测试。

4、还包括漏电流检测放电支路,所述漏电流检测放电支路包括驱动脉冲发生器vgs4、开关管mos4、电阻rg4和r5;

5、驱动脉冲发生器vgs4的一端接地,另一端通过电阻rg4与开关管mos4的栅极连接,开关管mos4的漏极与电阻r5的一端连接,电阻r5的另一端与开关管mos3的漏极连接,开关管mos4的源极接地;电容c2通过漏电流检测放电支路流经被测器件dut形成回路,在开关管mos3关断以及开关管mos4开通时,电容c2通过电阻r5、开关管mos4和被测器件dut所在回路进行低速率放电;进而通过在被测器件dut漏源极两端接入示波器或是采样电路检测dut漏源极电压变化情况,对比相同时间下被测器件dut两端的电压变化值,间接反映被测器件在经过大dv/dt冲击后的漏电流变化情况,判断所施加的高dv/dt冲击脉冲应力是否使得被测器件dut发生老化,进而判断被测器件的dv/dt耐受能力。

6、漏电流检测放电支路使得对被测器件的dv/dt耐受能力检测不需要在高dv/dt冲击阶段实时进行,将检测阶段和高dv/dt冲击阶段分开,检测阶段检测回路电流小,放电速度低,放电电流大小主要由dut漏电流决定。电阻r5可以在dut发生短路故障时限制c2放电电流,保护回路中其他器件不被烧坏,同时可以在检测阶段增大检测回路损耗,便于控制c2放电所需时间。在进行老化测试时被测器件的非破坏性老化也能通过被测器件在相同时间的漏源极电压下降值大小判断。

7、所述栅极大电流驱动电路包括高压直流电压源v1,驱动脉冲发生器vgs1,电阻r1、r2、r3、rg1和rg3,开关管mos1;

8、高压直流电压源v1的正极通过电阻r1连接开关管mos1的漏极,负极接地,电阻r2和电容c1的一端均连接开关管mos1的漏极,另一端接地,电阻r3一端与开关管mos3的栅极连接,另一端接地,开关管mos1的源极通过电阻rg3连接开关管mos3的栅极,驱动脉冲发生器vgs1的一端通过电阻rg1与开关管mos1的栅极连接,另一端与开关管mos1的源极连接。电容c1存储能量,在开关管mos1开通的瞬间迅速给开关管mos3内部的寄生电容充电,使开关管mos3快速开通,电阻rg3用于调节开关管mos3的开通速度,从而调节主电路dv/dt大小,开关管mos1保障开关管mos3的可靠开通和关断。

9、所述栅极大电流驱动电路还包括驱动脉冲发生器vgs2、电阻rg2与开关管mos2;

10、所述驱动脉冲发生器vgs2的一端通过电阻rg2与开关管mos2的栅极连接,另一端接地,开关管mos2的漏极与开关管mos1的源极连接,开关管mos2的源极接地;电阻r3和开关管mos2在开关管mos1关断时为mos3内部的寄生输入电容提供放电通路,单相半桥式结构连接的开关管mos1和mos2保障开关管mos3的可靠开通和关断。

11、所述栅极大电流驱动电路还包括电压钳制部件,电压钳制部件连接在开关管mos3的栅极和源极之间,当开关管mos3的栅极电压小时,电压钳制部件处于截止状态,当开关管mos3的栅极电压到达电压钳制部件的反向击穿电压时,电压钳制部件迅速由高电阻状态突变为低电阻导通状态,泄放瞬时过电流,将开关管mos3的栅极电压钳制在安全值。

12、一种用于功率器件的dv/dt耐受能力测试方法,所述测试方法包括准备阶段、高dv/dt冲击阶段和检测阶段;

13、所述高dv/dt冲击阶段包括:

14、经过准备阶段对被测器件dut内部的寄生电容充分放电后,通过控制开关管mos1开通,开关管mos2关断,使得电容c1两端电压突变而处于放电状态,产生大的感应电流给开关管mos3内部的寄生电容充电,使得开关管mos3因栅极电压迅速升高超过阈值电压而迅速导通;

15、开关管mos4关断,当开关管mos3栅极电压达到电压钳制部件的反向击穿电压或动作电压时,电压钳制部件由高电阻状态迅速突变为低电阻状态而导通,泄放瞬时过电流,将开关管mos3栅极电压钳制在安全值,防止开关管mos3被击穿,当mos3导通时,会将电容c2与mos3相连的一端强制接地,使得电容c2两端电压迅速施加到被测器件dut的两端,进而产生大的dv/dt脉冲电压应力对被测器件dut的dv/dt耐受能力进行测试。

16、所述准备阶段包括:

17、控制开关管mos1关断,开关管mos2开通,导致开关管mos3的栅极接地而处于关断状态,开关管mos3内部的寄生电容放电,电容c1充电,同时控制mos4关断,电容c2的一端通过r4与高压直流电压源v2正极端相连,另一端通过dut的寄生体二极管接地,高压直流电压源v2电压通过r4直接施加到电容c2两端,电容c2充电,被测器件寄生漏源极寄生电容放电。

18、所述检测阶段包括:

19、控制开关管mos1关断,开关管mos2开通,开关管mos3的栅极接地而处于关断状态,控制开关管mos4开通,电容c2通过电阻r5和开关管mos4施加到被测器件dut的两端,通过被测器件的漏电流缓慢放电,并通过示波器或是采样电路检测被测器件dut两端电压变化情况,对比相同时间下被测器件dut两端的电压变化值,判断所施加的高dv/dt冲击应力是否使得被测器件dut发生老化。

20、本发明具有以下优点:一种用于功率器件的dv/dt耐受能力测试电路及方法,可靠性更高,dv/dt脉冲电压大小可调节,另一方面,间接测量的观测方式不但可以检测被测器件的最大dv/dt耐受能力,还可以检测被测器件在高dv/dt冲击下的非破坏性老化情况,对测试设备的精度要求不高,可以大幅降低测试设备成本,可实现性高。

- 还没有人留言评论。精彩留言会获得点赞!