一种面向2.5D双芯粒互连封装系统的测试电路的制作方法

本发明涉及超大规模数字集成电路测试,特别涉及一种面向2.5d双芯粒互连封装系统的测试电路。

背景技术:

1、随着集成电路晶体管密度的提升,工艺技术发展的成本呈指数级增长,soc性能提高面临挑战,摩尔定律接近极限。基于芯粒技术的三维高密度异构集成是拓展摩尔定律的新一代技术载体。2.5d封装将多个芯粒(chiplet)封装在一个硅中介层(si-interposer)上,利用硅中介层上的微细线路实现芯片之间的高速、高密度、低延迟的互连。

2、互连测试是芯粒系统测试过程中的一个重要环节,其目的是验证芯粒各个功能模块之间的通信是否正常。ieee 1149系列标准中对芯片边界扫描测试技术给出相关规范,采用tap(test access port,测试访问端口)控制器对边界扫描电路进行配置和数据移位,可应用于测试多芯粒模块中的互连,但测试周期长;ieee 1838对3d封装的芯片测试给出相关规范,采用多层tap及灵活并行端口等方式对多个芯粒进行独立测试,但对绑定后芯粒系统中位于中介层的互连引脚依然存在测试调度差、测试配置复杂、测试向量冗长的问题。因此,提出一种易于调度的测试结构并缩短测试向量长度对2.5d双芯粒互连封装系统的测试具有重要意义。

技术实现思路

1、本发明的目的在于提供一种面向2.5d双芯粒互连封装系统的测试电路,以解决背景技术中的问题。

2、为解决上述技术问题,本发明提供了一种面向2.5d双芯粒互连封装系统的测试电路,该测试电路包括片间互连测试配置结构与面向片间互联的测试向量重定向结构,实现基于互连封装的芯粒系统中单个芯粒功能端口与中介层中未引出的互连端口的测试;其中,

3、通过jtag接口向测试电路输入定义的配置向量及数据向量,配置向量向扫描测试单元组输入配置扫描链重定向的控制信号,从而完成测试配置信号与测试数据的移位和输出。

4、在一种实施方式中,所述片间互连测试配置结构包括由tap控制器连接的边界扫描测试模式寄存器、测试模式配置解码器、由测试模式解码信号控制的测试配置输出选择器以及由测试模式配置选择信号控制的测试系统输出选择器。

5、在一种实施方式中,定义测试模式配置解码器的解码方式为:

6、(1)在扫描模式0下,test_mode[3:0]信号解码为test_mode_en=1’b1,当前芯粒的测试模式有效;

7、(2)在扫描模式1下,若测试序列为芯粒功能端口测试序列,则传输方向与芯粒序号一致时,test_mode[3:0]信号解码为test_mode_en=1’b1,当前芯粒的测试模式有效;其他情况下test_mode[3:0]信号解码为test_mode_en=1’b0,当前芯粒测试模式无效;

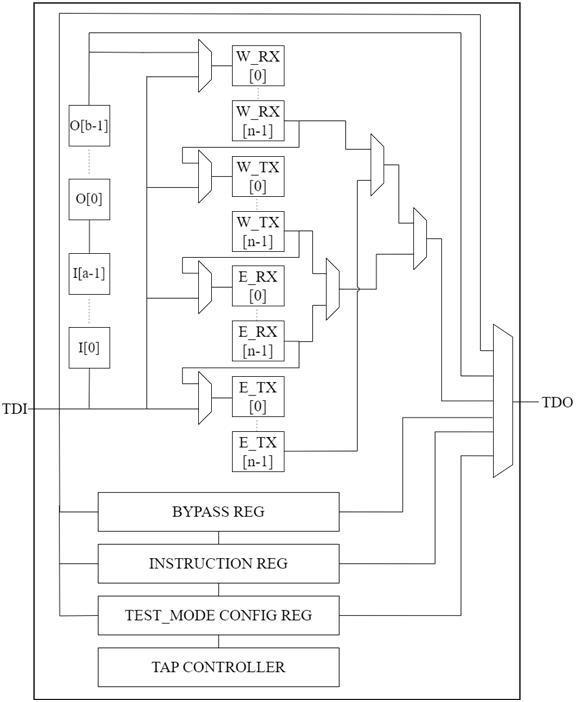

8、(3)在扫描模式1下,若测试序列为双芯粒系统互连端口测试序列,test_mode[3:0]信号始终解码为test_mode_en=1’b1,即当前芯粒测试模式始终有效。

9、在一种实施方式中,定义测试模式解码信号控制的测试配置输出选择器为:输入端0接入tdi,输入端1接入测试数据寄存器输出,选择信号为测试模式解码test_mode_en;测试模式解码为test_mode_en=1’b0时,配置选择器输出tdi,即tdi不经过测试电路直接输出,实现单芯粒功能端口的测试、旁路;测试模式解码为test_mode_en=1’b1时,配置选择器输出测试数据寄存器的值,完成接入端口的测试。

10、在一种实施方式中,定义由测试模式配置选择信号控制的测试系统输出选择器为:输入端0为测试配置选择器输出,输入端1为配置扫描测试模式寄存器的msb,选择信号为配置扫描测试模式寄存器使能crsel;当配置扫描测试模式寄存器使能crsel=1’b0时,测试系统输出选择器输出测试配置选择器的输出信号;配置扫描测试模式寄存器使能crsel=1’b0时,测试系统输出选择器由lsb至msb串行输出扫描测试模式配置信号test_mode[3:0]的值,当test_mode[3:0]默认值为4’b0011时,观测tdo串行输出1’b1,1’b1,1’b0,1’b0即完成配置。

11、在一种实施方式中,所述面向片间互联的测试向量重定向结构包括:

12、(1)由tap控制器生成的选择信号bs_mode、bs_regroup、bs_direction及n_chiplet;

13、(2)重定向的边界测试扫描单元组,包括单芯粒独立的功能端口组group_func_io及片间互连端口组group_w_rx、group_w_tx、group_e_rx和group_e_tx;

14、(3)由选择信号bs_mode控制的选择器边界扫描链输入选择器组,其中,每一个边界扫描单元组输入选择器的输入端0接入上一扫描单元组的扫描输出,输入端1接入测试系统扫描输入;当边界扫描模式配置信号bs_mode为1’b0时,配置边界扫描单元保留裸芯中所有端口接入边界扫描链的方式,即按照:

15、group_func_ioàgroup_w_rxàgroup_w_txàgroup_e_rxàgroup_e_tx的顺序,每一组的扫描输入si为前一组的扫描输出so,对chiplet_0共有(a+b+4n)个端口、对chiplet_1共有(c+d+4n)个端口接入扫描链;bs_mode为1’b1时,配置边界扫描单元组的输入为测试系统扫描输入,所有扫描单元组的输入都为tdi,对chiplet_0共有(a+b)个或n个端口接入扫描链,对chiplet_1共有(c+d)个或n个端口接入扫描链;

16、(4)由选择信号bs_mode、bs_regroup、bs_direction及n_chiplet控制的选择器边界扫描链输出选择器组,其中,由bs_mode控制的边界扫描单元组输出选择器mux0,其输入端0为单元组e_tx输出,输入端1接入片间互连重定向结构的so输出;由bs_regroup控制的边界扫描单元组输出选择器mux1,其输入端0接入功能io组的扫描输出,输入端1接入片间互连组的扫描输出;由bs_direction控制的边界扫描单元组输出选择器mux2,其输入端0接入group_e_tx或group_w_rx的边界扫描输出,输入端1接入group_e_rx或group_w_tx的边界扫描输出;由n_chiplet控制的边界扫描单元组输出选择器mux3及mux4,mux3的输入端0接入group_e_tx的扫描输出,输入端1接入group_w_rx的扫描输出,mux4的输入端0接入group_e_rx的扫描输出,输入端1接入group_w_tx的扫描输出。

17、在一种实施方式中,面向片间互联的测试向量重定向结构可配置的重定向方式包括:

18、(1)test_mode[3:0]=4’b0xxx,测试数据流为:tdi à group_func_io à group_w_rx à group_w_tx à group_e_rx à group_e_tx à tdo;

19、(2)test_mode[3:0]=4’b1000/4’b1011,测试数据流为:tdi à group_func_io àtdo;

20、(3)test_mode[3:0]=4’b1001/4’b1010,测试数据流为:tdi à tdo,与ieee1149.1规定的旁路方式不同的是,该配置下不需要再对指令寄存器进行配置,电路数据流无需通过旁路寄存器;

21、(4)test_mode[3:0]=4’b1100,测试数据流为:tdi à group_e_tx à tdo;

22、(5)test_mode[3:0]=4’b1101,测试数据流为:tdi à group_w_rx à tdo;

23、(6)test_mode[3:0]=4’b1110,测试数据流为:tdi à group_e_rx à tdo;

24、(7)test_mode[3:0]=4’b1111测试数据流为:tdi à group_w_tx à tdo。

25、在一种实施方式中,在进行功能端口测试时,将待测芯粒中test_mode[3:0]配置为4’b1000或4’b1011,向指令寄存器输入相应指令,完成相应io的测试;互连端口测试时,根据需求进行如下配置:

26、片间互联测试的数据路径按照传输方向分为direction_0与direction_1,步骤如下:

27、s1:direction_0方向测试模式配置寄存器配置,即向测试电路中串行输入1’b1,1’b0,1’b1,1’b1,1’b0,1’b0,1’b1,1’b1,此时chiplet_0中test_mode[3:0]=4’b1100,chiplet_1中test_mode[3:0]=4’b1101,direction_0接入测试电路,tdo串行输出1’b1,1’b1,1’b0,1’b0,1’b1,1’b1,1’b0,1’b0;

28、s2:direction_0方向指令寄存器配置,即向测试电路中串行输入1’b1,1’b0,1’b1,1’b0,1’b1,1’b0,1’b0,1’b0,此时chiplet_0中instruction[3:0]=4’0001,chiplet_1中instruction[3:0]=4’0101,tdo串行输出1’b1,1’b0,1’b0,1’b0,1’b1,1’b0,1’b0,1’b0;

29、s3:direction_0方向数据移位,即向测试电路chiplet_0中group_e_tx、chiplet_1中group_w_rx串行输入奇/偶向量,比较tdo与预期的结果是否一致;

30、s4:direction_1方向测试模式配置寄存器配置,即向测试电路中串行输入1’b1,1’b1,1’b1,1’b1,1’b0,1’b1,1’b1,1’b1,此时chiplet_0中test_mode[3:0]=4’b1110,chiplet_1中test_mode[3:0]=4’b1111,direction_1接入测试电路,tdo串行输出1’b1,1’b1,1’b0,1’b0,1’b1,1’b1,1’b0,1’b0;

31、s5:direction_1方向指令寄存器配置,即向测试电路中串行输入1’b1,1’b0,1’b0,1’b0,1’b1,1’b0,1’b1,1’b0,此时chiplet_0中instruction[3:0]=4’0101,chiplet_1中instruction[3:0]=4’0001,tdo串行输出1’b1,1’b0,1’b0,1’b0,1’b1,1’b0,1’b0,1’b0;

32、s6:direction_1方向数据移位,即向测试电路chiplet_0中group_e_rx、chiplet_1中group_w_ex串行输入奇/偶向量,由于观测组为group_e_rx,在最后一次移位前配置chiplet_1中test_mode[3:0]=4’1010,即共需数据移位周期cycle=2n+2n+n=5n,比较tdo与预期的结果是否一致。

33、本发明提供的一种面向2.5d双芯粒互连封装系统的测试电路,在不增加测试端口和测试向量冗余的前提下实现了兼容原有单芯粒封装情况、及双芯粒互联封装后(a+b+c+d)个功能io端口、及2n对片间互连传输端口的测试,通过增加8bit配置向量实现对双芯粒系统的快速配置。重定向后仅需10n个数据移位周期即可完成2n对互联端口的测试,相比原有测试向量长度2[a+b+2(c+d)+8n]bit,节省测试向量长度为2[a+b+2(c+d)+3n]bit,即对互联端口进行测试时,将所输入的奇、偶向量重定向到互连数据传输的rx/tx端口组,不再经过系统的功能io端口组。

- 还没有人留言评论。精彩留言会获得点赞!