芯片及其测试电路的制作方法

本技术涉及芯片测试,特别涉及一种芯片及其测试电路。

背景技术:

1、目前,mcu(micro-controller unit,微控制单元)一般通过内置的ldo(lowdropout regulator,低压差线性稳压器)为整个芯片提供稳定的电源。当芯片进入ate(auto-test-equipment,自动试验设备)测试的时候,为了节约测试时间和成本,需要将内部的ldo关断,直接通过外部pmic电源供电,以进行有效快速的测试。但是,相关技术中是在外部pmic电源输入后,再关断内部的ldo,这种方式无法避免内部ldo和外部pmic电源同时驱动对拉的情况,可能会对芯片造成意外的伤害。

技术实现思路

1、本发明旨在至少在一定程度上解决相关技术中的技术问题之一。为此,本发明的第一个目的在于提出一种芯片的测试电路,在芯片需要进入测试模式时,控制内部的第一供电单元停止供电,然后外部pmic电源才给电压可关断区域供电,避免了内部电源和外部pmic电源同时驱动对拉的情况发生,从而避免对芯片内部造成损害。

2、本发明的第二个目的在于提出一种芯片。

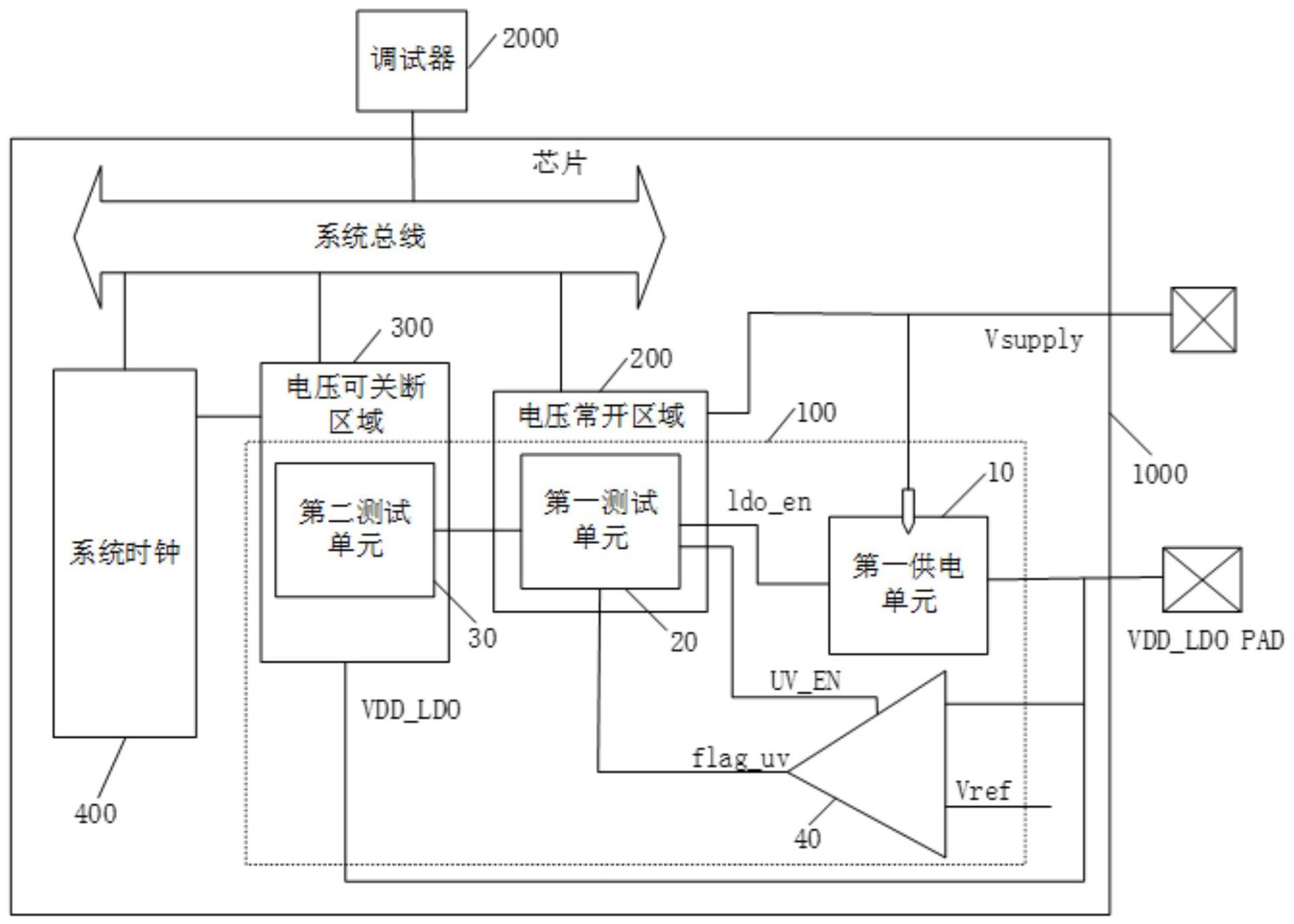

3、为达上述目的,根据本发明第一方面实施例提出了一种芯片的测试电路,芯片包括电压常开区域和电压可关断区域,测试电路包括:第一供电单元,第一供电单元适于连接芯片的系统电源,以给电压可关断区域供电,其中,系统电源还适于给电压常开区域供电;位于电压常开区域的第一测试单元,第一测试单元被配置为在芯片需进入测试模式的情况下,控制第一供电单元停止工作,以便外部pmic电源给电压可关断区域供电。

4、根据本发明实施例的芯片的测试电路,包括第一供电单元和第一测试单元,第一供电单元适于连接芯片的系统电源,以给电压可关断区域供电,其中,系统电源还适于给电压常开区域供电,因此,第一供电单元是芯片的内部电源,第一测试单元被配置为在芯片需进入测试模式的情况下,控制第一供电单元停止工作,以便外部pmic电源给电压可关断区域供电,因此,在外部pmic电源输入前,芯片内部的第一供电单元已经停止工作,所以不存在内部电源和外部pmic电源同时驱动对拉的情况,从而避免对芯片内部造成损害。

5、根据本发明的一个实施例,测试电路还包括:位于电压可关断区域的第二测试单元,第二测试单元配置为生成电源关断信号,以使第一测试单元根据电源关断信号控制第一供电单元停止工作,并在外部pmic电源输入后,根据预先配置的测试需求生成测试模式。

6、根据本发明的一个实施例,测试电路还包括:电压比较单元,电压比较单元的第一输入端分别与第一供电单元的输出端和外部pmic电源相连,电压比较单元的第二输入端适于输入预设阈值电压,电压比较单元的输出端与第一测试单元相连,电压比较器被配置为根据预设阈值电压、第一供电单元输出的电压和外部pmic电源生成电压检测信号,其中,电压检测信号用于第一测试单元和第二测试单元之间进行信号隔离传输。

7、根据本发明的一个实施例,在系统电源直接给电压常开区域供电的情况下,第二测试单元包括:测试模式预设寄存器堆,被配置为根据测试需求生成测试数值;测试模式控制状态机,测试模式控制状态机与测试模式预设寄存器堆相连,测试模式控制状态机被配置为根据测试数值生成测试模式、电源关断信号和测试使能信号;第一与门,第一与门的第一输入端与测试模式控制状态机的第二输出端相连。

8、根据本发明的一个实施例,第一测试单元包括:上升沿产生模块,上升沿产生模块的输入端与测试模式控制状态机的第一输出端相连,上升沿产生模块被配置为根据测试使能信号生成脉冲信号;dff,dff的控制端与上升沿产生模块的输出端相连,dff的输入端与第一与门的输出端相连,dff的第二输出端与第一与门的第二输入端相连;第一电平转换器,第一电平转换器的输入端与dff的第二输出端相连;第一锁存器,第一锁存器的第一输入端与第一电平转换器的输出端相连,第一锁存器的第二输入端适于输入电压检测信号,第一锁存器的输出端与第一供电单元的使能端相连;第二电平转换器,第二电平转换器的输入端与dff的第一输出端相连;第二锁存器,第二锁存器的第一输入端与第二电平转换器的输出端相连,第二锁存器的第二输入端与电压比较单元的输出端相连,第二锁存器的输出端与电压比较单元的使能端相连。

9、根据本发明的一个实施例,测试电路还包括:第二供电单元,第二供电单元适于连接系统电源,以给电压常开区域供电。

10、根据本发明的一个实施例,第二测试单元包括:测试模式预设寄存器堆,被配置为根据测试需求生成测试数值;测试模式控制状态机,测试模式控制状态机与测试模式预设寄存器堆相连,测试模式控制状态机被配置为根据测试数值生成测试模式、电源关断信号和测试使能信号。

11、根据本发明的一个实施例,第一测试单元包括:第一隔离缓存模块,第一隔离缓存模块的第一输入端与测试模式控制状态机的第一输出端相连,第一隔离缓存模块被配置为对测试使能信号进行隔离传输和电平转换,生成隔离测试使能信号;上升沿产生模块,上升沿产生模块的输入端与第一隔离缓存模块的输出端相连,上升沿产生模块被配置为根据隔离测试使能信号生成脉冲信号;第二隔离缓存模块,第二隔离缓存模块的第一输入端与测试模式控制状态机的第二输出端相连,第二隔离缓存模块被配置为对电源关断信号进行隔离传输和电平转换,生成隔离电源关断信号;第一与门,第一与门的第一输入端与第二隔离缓存模块的输出端相连;dff,dff的控制端与上升沿产生模块的输出端相连,dff的输入端与第一与门的输出端相连,dff的第一输出端与电压比较单元的使能端相连,dff的第二输出端分别与第一供电单元的使能端和第一与门的第二输入端相连;第二与门,第二与门的第一输入端与dff的第一输出端相连,第二与门的第二输入端与电压比较器的输出端相连,第二与门的输出端分别与第一隔离缓存模块的第二输入端相连和第二隔离缓存模块的第二输入端相连,第二与门被配置为根据dff的第一输出端输出的信号和电压检测信号生成隔离信号和复位信号,其中,复位信号用于对测试模式预设寄存器堆和测试模式控制状态机进行复位。

12、根据本发明的一个实施例,第二测试单元适于连接调试器,第二测试单元还被配置为接收调试器发送的解锁保护序列,并在接收调试器发送的解锁保护序列之后,接收调试器发送的测试需求。

13、根据本发明的一个实施例,第二测试单元适于连接系统时钟,以接收系统时钟输出的时钟信号。

14、为达上述目的,根据本发明第二方面实施例提出了一种芯片,包括前述任一实施例的芯片的测试电路。

15、根据本发明实施例的芯片,通过采用上述的芯片的测试电路,在芯片需要进入测试模式时,控制内部的第一供电单元停止供电,然后外部pmic电源才给电压可关断区域供电,避免了内部电源和外部pmic电源同时驱动对拉的情况发生,从而避免对芯片内部造成损害。

16、本发明附加的方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本发明的实践了解到。

- 还没有人留言评论。精彩留言会获得点赞!