一种多通道数字隔离芯片的隔离测试方法与流程

本发明涉及精密电子设备及集成电路数字隔离芯片输出信号隔离测试领域,适用于一种多通道数字隔离芯片的隔离测试方法。

背景技术:

1、随着集成电路技术的不断进步,多通道数字隔离芯片实现了更高的集成度。现代的多通道数字隔离芯片可以在一个单一芯片上实现多个输入通道和输出通道,降低了系统复杂性和成本,随着数字通信和数据处理的需求增加,多通道数字隔离芯片的传输速率也得到提升。现在的多通道数字隔离芯片支持更高的数据传输速率,满足了高速通信系统的需求,随着对能源效率要求的提高,多通道数字隔离芯片的功耗也逐渐降低。低功耗设计使得芯片适用于低能耗设备和便携式设备,延长了电池寿命,多通道数字隔离芯片在抵御外部干扰方面有了显著的改进。现代的芯片结构和设计使其能够有效地抑制电磁干扰和噪声,提供更可靠的数据隔离和传输,安全性:对于一些关键应用领域,如工业控制、医疗设备等,多通道数字隔离芯片的安全性要求越来越高。现代芯片通过采用安全隔离技术和防护措施来保护数据和系统的安全,它们被用于工业自动化、电力系统监控、仪器仪表、医疗设备、电动汽车充电桩等领域,以实现信号隔离、数据传输和系统保护等功能。

2、例如在申请公开号为cn111600593a的专利中公开了提供一种多通道数字隔离芯片的实现方法和实现系统,所述方法包括:在隔离器两端增加相互匹配设置的编、解码器,根据系统传输信号通道的数量配置隔离器的数量;根据系统传输信号通道的数量以及隔离器的数量配置编码器的编码码型数目;其中,n<m,cn>2m,m≥2,m表示系统传输信号通道的数量,n表示隔离器的数量,c表示编码器采用的编码码型数目;数据传输过程中,发送端发送多通道信号源数据,对多通道信号源数据进行编码形成编码信号后发送至隔离器;接收端接收编码信号,并对其进行解码重建恢复为原始的多通道信号后进行输出。该发明通过减少数字隔离器的数量,进而减小数字隔离芯片的尺寸面积。

3、上述专利中存在:只对编码器进行精细改进,并没有过多的考虑环境因素影响,也没有对温度进行严格把控,这样数字隔离信号很容易受到外界电磁影响或者温度影响,从而影响编码和解码效率,甚至会影响编码和解码的准确性。

4、本发明的优势:降低低频信号下的外部干扰信号问题,调制编码器将通过滤波器出去毛刺的输入信号分离出上升、下降沿,滤波器电路处理外部输入信号上诸如毛刺等干扰信号,以免影响脉冲生成电路,还可以根据内部定时电路的计时来定时给入刷新信号至脉冲产生电路,避免在信号周期较大的情况下外部干扰信号对脉冲产生的影响。

技术实现思路

1、本部分的目的在于概述本发明的实施例的一些方面以及简要介绍一些较佳实施例。在本部分以及本技术的说明书摘要和发明名称中可能会做些简化或省略以避免使本部分、说明书摘要和发明名称的目的模糊,而这种简化或省略不能用于限制本发明的范围。

2、为解决上述技术问题,本发明的主要目的在于提供一种多通道数字隔离芯片的隔离测试方法;

3、能够有效解决背景技术中的问题:只对编码器进行精细改进,并没有过多的考虑环境因素影响,也没有对温度进行严格把控,这样数字隔离信号很容易受到外界电磁影响或者温度影响,从而影响编码和解码效率,甚至会影响编码和解码的准确性。

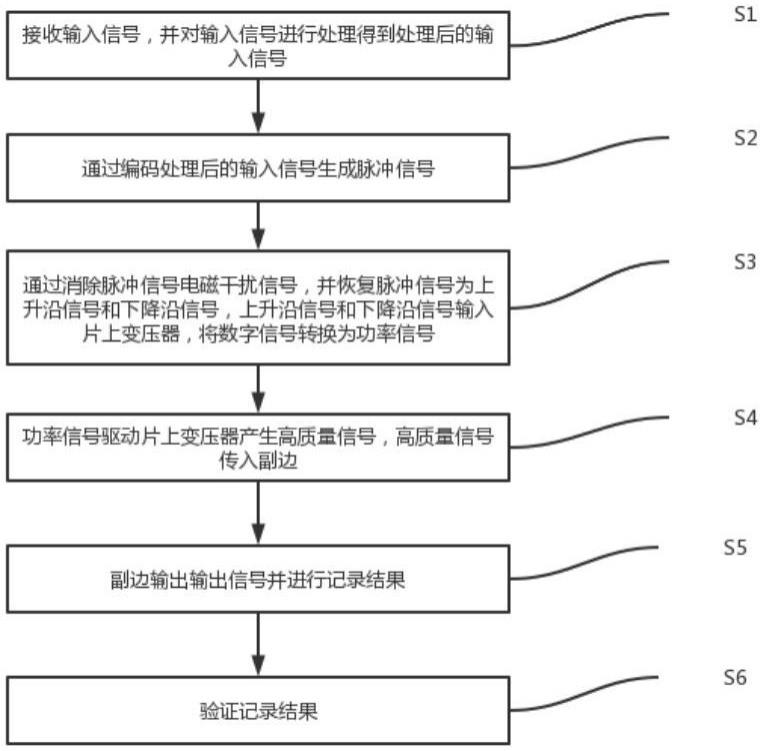

4、为实现上述目的,发明了一种多通道数字隔离芯片的隔离测试方法:

5、s1、接收输入信号,并对输入信号进行处理得到处理后的输入信号;

6、s2、通过编码处理后的输入信号生成脉冲信号;

7、s3、通过消除脉冲信号电磁干扰信号,并恢复脉冲信号为上升沿信号和下降沿信号,上升沿信号和下降沿信号输入片上变压器,将数字信号转换为功率信号;

8、s4、功率信号驱动片上变压器产生高质量信号,高质量信号传入副边;

9、s5、副边输出输出信号并进行记录结果;

10、s6、验证记录结果。

11、作为本发明所述一种多通道数字隔离芯片的隔离测试方法的一种优选方案,其中:

12、通过信号输入处理对输入信号进行消除滤波和整流处理。

13、作为本发明所述一种多通道数字隔离芯片的隔离测试方法的一种优选方案,其中:

14、所述脉冲信号包括双脉冲信号和单脉冲信号;

15、通过编码器接收消除滤波和整流处理后的信号,通过对消除滤波和整流处理后的信号的上升沿和下降沿分别产生双脉冲信号和单脉冲信号。

16、作为本发明所述一种多通道数字隔离芯片的隔离测试方法的一种优选方案,其中:

17、消除脉冲信号中的电磁干扰信号,并恢复脉冲信号为上升沿信号和下降沿信号,通过刷新电路对脉冲信号进行延时调整,通过延时电路来调整延时时间,通过偏置电流电路对上升沿信号和下降沿信号进行温度调整。

18、作为本发明所述一种多通道数字隔离芯片的隔离测试方法的一种优选方案,其中:

19、功率信号驱动片上变压器产生高质量信号,高质量信号传入副边接收模块,包括以下内容;

20、通过变压器中的电感线圈将数字信号进行转化得到所述功率信号;

21、所述高质量信号即通将含有外界电磁信号干扰产生的额外脉冲信号进行宽度限制,进而进行消除外界电磁信号的干扰。

22、作为本发明所述一种多通道数字隔离芯片的隔离测试方法的一种优选方案,其中:

23、所述记录结果包括,输入通道测试结果、输出通道测试结果、隔离性测试结果、响应时间测试结果、抗干扰性测试结果、温度变化测试结果、可靠性测试结果;

24、所述输入通道测试:确定多通道数字隔离芯片的输入通道数量,并测试每个输入通道的功能和性能,输入通道测试内容包括输入电压范围、输入电流、功耗;

25、所述输出通道测试:确定多通道数字隔离芯片的输出通道数量,并测试每个输出通道的功能和性能,输出通道测试内容包括输出电压范围、输出电流、驱动能力;

26、所述隔离性测试:测试多通道数字隔离芯片的输入通道之间的隔离性能,确保输入信号不会相互干扰,通过发送不同信号到各个输入通道并检测输出的信号是否有受到干扰;

27、所述响应时间测试:测试多通道数字隔离芯片的输出通道的响应时间,即输入信号变化后,输出信号的变化时间;

28、所述抗干扰性测试:测试多通道数字隔离芯片对于外部干扰的抗干扰能力,确保在干扰环境下芯片的正常工作;

29、所述温度变化测试:测试多通道数字隔离芯片在不同温度下的工作性能和稳定性,通道测试内容包括输入输出通道的温度漂移、温度影响;

30、所述可靠性测试:测试多通道数字隔离芯片在长时间运行、高负载条件下的可靠性和稳定性,通道测试内容包括持续性测试、高负载测试。

31、作为本发明所述一种多通道数字隔离芯片的隔离测试系统的一种优选方案,其中:

32、发送模块,包括用于接收输入信号并对输入信号进行处理的信号输入处理单元;根据输入信号生成上升沿和下降沿对应的脉冲信号的编码器;用于解决长时间输入信号为高电平或者低电平导致片上变压器的两端会长时间保持为低/高电平的刷新电路单元;用于产生零温电流的偏置电流单元;

33、副边接收模块,包括用于对产生电磁信号干扰产生额外脉冲进行宽度限制的单稳态单元;脉冲恢复单元用于将双脉冲信号和单脉冲信号分别变换为上升沿信号和下降沿信号,从而将信号恢复成被编码前的形状,当输入信号的一个沿来到后,计时单元用于每隔固定时间,生成放电流速度相等的窄的计时脉冲,当新的沿信号到来后,其计数脉冲的累积时长都会清零,从而重新开始;用于接收报错信号并发出报错指示灯的报错单元;

34、片上变压器驱动模块用于编码生成的数字信号转变为功率信号,从而驱动片上变压器将信号高质量的传递到副边,变压器中的电感线圈将数字信号进行转化得到所述功率信号。

35、作为本发明所述一种多通道数字隔离芯片的隔离测试系统的一种优选方案,其中:

36、所述信号输入处理单元通过施密特触发器正负翻转电平的阈值不同对输入信号进行整流,滤除叠加在输入信号的干扰信号,经过处理后的滤波信号通过sr锁存器进行复位;

37、所述编码器通过接收消除干扰信号和复位后的输入信号并根据输入信号的上升沿和下降沿分别产生双脉冲和单脉冲信号;

38、所述刷新电路单元产生用于刷新信号的脉冲,分别对应输入信号的上升沿和下降沿,其默认值为“1”,其中刷新电路单元还包括延时电路,通过调节电容的大小来控制延时时间;

39、所述偏置电流单元包括计时电路,计时电路通过接收一路ctat电流和一路ptat电流产生零温电流,vdda启动至超过pmos导通电压,r1一直在下拉m1栅极,m1管打开,导通电流,m2删电压提高,电压至m2导通电压值时,m2导通,下拉m4-m7-m12-m13 的栅电压,从而m4-m7-m12-m13 开始有电流通过,产生ptat电流,电路完全导通。

40、作为本发明所述一种多通道数字隔离芯片的隔离测试系统的一种优选方案,其中:

41、所述单稳态单元将输入端收到外界电磁信号的干扰产生的额外脉冲进行宽度限制,in 连接至施密特触发器的输出,电容充电计时模块的两个复位端若外部信号不变,则触发器输出不变,若输入信号有上升沿时,d 触发器输出上一个状态下的值;

42、所述脉冲恢复单元接收单稳态单元生成的时钟信号,将输入的单脉冲信号和双脉冲信号分别转化为下降沿和上升沿,最终将信号恢复成编码前的形状;

43、所述报错单元,对超过8μs都没有到来的输入信号,全部视为输入信号错误,报错单元触发错误模式,输出高电平点亮报错指示灯。

44、作为本发明所述一种多通道数字隔离芯片的隔离测试系统的一种优选方案,其中:

45、所述片上变压器驱动模块通过电感线圈将数字信号转变为功率信号,从而将信号传递到副边接收模块,若enb 和 en 均有效,则副边接收模块等效为短路或断路,in 相当于经过以及反相器直接接在 nmos 驱动管上,若in=h,则nmos驱动电压为低电平,pmos驱动管的栅极接接地,vout被输入高电平电流,若in=l,则nmos的栅电压为高电压,nmos的驱动管上拉到vdd,vout输出大电流。

46、一种计算机设备,包括,存储器,用于存储指令;处理器,用于执行所述指令,使得所述设备执行实现一种多通道数字隔离芯片的隔离测试方法。

47、一种计算机可读存储介质,其上存储有计算机程序,该计算机程序被所述处理器执行时,实现一种多通道数字隔离芯片的隔离测试方法。

48、本发明的有益效果:

49、本发明降低低频信号下的外部干扰信号问题,调制编码器将通过滤波器出去毛刺的输入信号分离出上升、下降沿。

50、本发明滤波器电路处理外部输入信号上诸如毛刺等干扰信号,以免影响脉冲生成电路,还可以根据内部定时电路的计时来定时给入刷新信号至脉冲产生电路,避免在信号周期较大的情况下外部干扰信号对脉冲产生的影响。

51、本发明通过设置延时电路,延时的具体长短是可控的,可通过改变电容的大小或者反相器的个数来实现延时时间控制。而在电容后接入施密特触发器同样也是出于避免电容两端电压不稳定带来的不确定性影响。

52、本发明偏置电流偏置单元,产生零温电流,处理了环境温度对输入信号的影响。

53、解决了没有过多的考虑环境因素影响,没有对温度进行严格把控,这样数字隔离信号很容易受到外界电磁影响或者温度影响,从而影响编码和解码效率,甚至会影响编码和解码的准确性。

- 还没有人留言评论。精彩留言会获得点赞!