一种用于芯片管脚间的开路或短路测试方法、系统及平台与流程

本发明属于检测处理,具体涉及一种用于芯片管脚间的开路或短路测试方法、系统及平台。

背景技术:

1、边界扫描自动测试系统软件是一款用于治具行业服务器主板或相对复杂的pcba(电路板)的测试软件,其主要功能是通过分析制板资料,自动查找出测试路径,并根据这些路径生成芯片管脚驱动数据,通过控制器将jtag(一种通讯协议)信号驱动至被测芯片,芯片在得道相应数据后,驱动管脚输出或接收输入,通过对jtag(一种通讯协议)信号的解析,确定有故障的pin(引脚)或路径。

2、现目前,边界扫描自动测试系统分析数据量较大,主要广泛依托于软件集成平台层面上的测试路径分析,而且其分析效率不高,开路或短路测试耗时长,测试效率低。

3、因此,针对以上的技术问题缺陷,急需设计和开发一种用于芯片管脚间的开路或短路测试方法、系统及平台。

技术实现思路

1、为克服上述现有技术存在的不足及困难,本发明之目的在于,针对测试路径分析效率低,开路或短路测试耗时长,测试效率低的技术问题缺陷,而提供一种用于芯片管脚间的开路或短路测试方法、系统及平台,以提高测试路径分析效率和开短路的测试效率。

2、本发明的第一目的在于提供一种用于芯片管脚间的开路或短路测试方法;本发明的第二目的在于提供一种用于芯片管脚间的开路或短路测试系统;本发明的第三目的在于提供一种用于芯片管脚间的开路或短路测试平台。

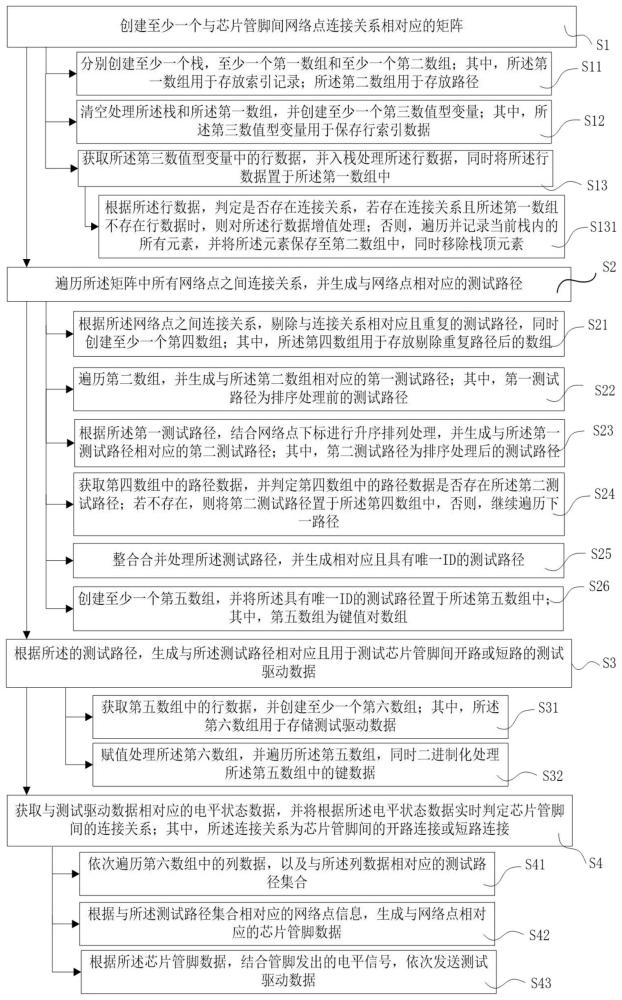

3、本发明的第一目的是这样实现的:所述方法包括如下步骤:

4、创建至少一个与芯片管脚间网络点连接关系相对应的矩阵;

5、遍历所述矩阵中所有网络点之间连接关系,并生成与网络点相对应的测试路径;

6、根据所述的测试路径,生成与所述测试路径相对应且用于测试芯片管脚间开路或短路的测试驱动数据;

7、获取与测试驱动数据相对应的电平状态数据,并将根据所述电平状态数据实时判定芯片管脚间的连接关系;其中,所述连接关系为芯片管脚间的开路连接或短路连接。

8、进一步地,所述创建至少一个与芯片管脚间网络点连接关系相对应的矩阵,还包括:

9、分别创建至少一个栈,至少一个第一数组和至少一个第二数组;其中,所述第一数组用于存放索引记录;所述第二数组用于存放路径;

10、清空处理所述栈和所述第一数组,并创建至少一个第三数值型变量;其中,所述第三数值型变量用于保存行索引数据;

11、获取所述第三数值型变量中的行数据,并入栈处理所述行数据,同时将所述行数据置于所述第一数组中。

12、进一步地,所述获取所述第三数值型变量中的行数据,并入栈处理所述行数据,同时将所述行数据置于所述第一数组中,还包括:

13、根据所述行数据,判定是否存在连接关系,若存在连接关系且所述第一数组不存在行数据时,则对所述行数据增值处理;否则,遍历并记录当前栈内的所有元素,并将所述元素保存至第二数组中,同时移除栈顶元素。

14、进一步地,所述遍历所述矩阵中所有网络点之间连接关系,并生成与网络点相对应的测试路径,还包括:

15、根据所述网络点之间连接关系,剔除与连接关系相对应且重复的测试路径,同时创建至少一个第四数组;其中,所述第四数组用于存放剔除重复路径后的数组;

16、遍历第二数组,并生成与所述第二数组相对应的第一测试路径;其中,第一测试路径为排序处理前的测试路径;

17、根据所述第一测试路径,结合网络点下标进行升序排列处理,并生成与所述第一测试路径相对应的第二测试路径;其中,第二测试路径为排序处理后的测试路径;

18、获取第四数组中的路径数据,并判定第四数组中的路径数据是否存在所述第二测试路径;若不存在,则将第二测试路径置于所述第四数组中,否则,继续遍历下一路径。

19、进一步地,所述遍历所述矩阵中所有网络点之间连接关系,并生成与网络点相对应的测试路径,还包括:

20、整合合并处理所述测试路径,并生成相对应且具有唯一id的测试路径;

21、创建至少一个第五数组,并将所述具有唯一id的测试路径置于所述第五数组中;其中,第五数组为键值对数组。

22、进一步地,所述根据所述的测试路径,生成与所述测试路径相对应且用于测试芯片管脚间开路或短路的测试驱动数据,还包括:

23、获取第五数组中的行数据,并创建至少一个第六数组;其中,所述第六数组用于存储测试驱动数据;

24、赋值处理所述第六数组,并遍历所述第五数组,同时二进制化处理所述第五数组中的键数据。

25、进一步地,所述获取与测试驱动数据相对应的电平状态数据,并将根据所述电平状态数据实时判定芯片管脚间的连接关系,还包括:

26、依次遍历第六数组中的列数据,以及与所述列数据相对应的测试路径集合;

27、根据与所述测试路径集合相对应的网络点信息,生成与网络点相对应的芯片管脚数据;

28、根据所述芯片管脚数据,结合管脚发出的电平信号,依次发送测试驱动数据。

29、本发明的第二目的是这样实现的:所述系统应用于所述的测试方法,所述系统包括:

30、矩阵创建单元,用于创建至少一个与芯片管脚间网络点连接关系相对应的矩阵;

31、第一生成单元,用于遍历所述矩阵中所有网络点之间连接关系,并生成与网络点相对应的测试路径;

32、第二生成单元,用于根据所述的测试路径,生成与所述测试路径相对应且用于测试芯片管脚间开路或短路的测试驱动数据;

33、第一判定单元,用于获取与测试驱动数据相对应的电平状态数据,并将根据所述电平状态数据实时判定芯片管脚间的连接关系;其中,所述连接关系为芯片管脚间的开路连接或短路连接。

34、进一步地,所述矩阵创建单元,还包括:

35、第一创建模块,用于分别创建至少一个栈,至少一个第一数组和至少一个第二数组;其中,所述第一数组用于存放索引记录;所述第二数组用于存放路径;

36、第二创建模块,用于清空处理所述栈和所述第一数组,并创建至少一个第三数值型变量;其中,所述第三数值型变量用于保存行索引数据;

37、第一处理模块,用于获取所述第三数值型变量中的行数据,并入栈处理所述行数据,同时将所述行数据置于所述第一数组中;

38、和/或,所述第一处理模块,还包括:

39、第一判定模块,用于根据所述行数据,判定是否存在连接关系;

40、和/或,所述第一生成单元,还包括:

41、第三创建模块,用于根据所述网络点之间连接关系,剔除与连接关系相对应且重复的测试路径,同时创建至少一个第四数组;其中,所述第四数组用于存放剔除重复路径后的数组;

42、第一生成模块,用于遍历第二数组,并生成与所述第二数组相对应的第一测试路径;其中,第一测试路径为排序处理前的测试路径;

43、第二生成模块,用于根据所述第一测试路径,结合网络点下标进行升序排列处理,并生成与所述第一测试路径相对应的第二测试路径;其中,第二测试路径为排序处理后的测试路径;

44、第二判定模块,用于获取第四数组中的路径数据,并判定第四数组中的路径数据是否存在所述第二测试路径;;

45、和/或,所述第一生成单元,还包括:

46、第三生成模块,用于整合合并处理所述测试路径,并生成相对应且具有唯一id的测试路径;

47、第四创建模块,用于创建至少一个第五数组,并将所述具有唯一id的测试路径置于所述第五数组中;其中,第五数组为键值对数组;

48、和/或,所述第二生成单元,还包括:

49、第五创建模块,用于获取第五数组中的行数据,并创建至少一个第六数组;其中,所述第六数组用于存储测试驱动数据;

50、第二处理模块,用于赋值处理所述第六数组,并遍历所述第五数组,同时二进制化处理所述第五数组中的键数据;

51、和/或,所述第一判定单元,还包括:

52、第一遍历模块,用于依次遍历第六数组中的列数据,以及与所述列数据相对应的测试路径集合;

53、第四生成模块,用于根据与所述测试路径集合相对应的网络点信息,生成与网络点相对应的芯片管脚数据;

54、第一发送模块,用于根据所述芯片管脚数据,结合管脚发出的电平信号,依次发送测试驱动数据。

55、本发明的第三目的是这样实现的:包括处理器、存储器以及用于芯片管脚间的开路或短路测试平台控制程序;其中在所述的处理器执行所述的用于芯片管脚间的开路或短路测试平台控制程序,所述的用于芯片管脚间的开路或短路测试平台控制程序被存储在所述存储器中,所述的用于芯片管脚间的开路或短路测试平台控制程序,实现所述的用于芯片管脚间的开路或短路测试方法。

56、本发明通过方法创建至少一个与芯片管脚间网络点连接关系相对应的矩阵;遍历所述矩阵中所有网络点之间连接关系,并生成与网络点相对应的测试路径;根据所述的测试路径,生成与所述测试路径相对应且用于测试芯片管脚间开路或短路的测试驱动数据;获取与测试驱动数据相对应的电平状态数据,并将根据所述电平状态数据实时判定芯片管脚间的连接关系;以及与所述方法相应的系统、平台,可以提高测试路径分析效率和开短路的测试效率。

57、也就是说,通过本发明方案解决了开短路测试路径查找问题,相比于传统处理方法,分析时间大大减少,软件体验感得到增强,并在一定程度上提高了生产力;此外,本发明涉及的算法过程不依赖于编程语言、操作系统、可以把该过程轻松移植到任何实际需要的开发环境中去。而涉及到的开短路测试驱动数据的生成处理算法,极大的减少了测试次数,在实际生产过程中,直接体现是测试时间大幅缩短,提高了生产效率。

- 还没有人留言评论。精彩留言会获得点赞!