芯片短路校验方法、装置、芯片检测方法、芯片和耗材盒与流程

本技术涉及打印设备,特别是涉及一种芯片短路校验方法、装置、芯片检测方法、芯片和耗材盒。

背景技术:

1、常见的打印设备会安装有可拆卸的耗材盒,以在墨水用尽后方便更换新耗材盒。墨盒、硒鼓、墨袋盒等均属于常见的耗材盒,通常均配备有芯片,芯片中可存储各种信息,并可与打印设备通信。

2、芯片上通常设有电源端子(vdd)、数据端子(data)、时钟端子(clk)、复位端子(rst/ce)和接地端子(gnd)等,由于耗材盒中的墨水可能滴漏到芯片的端子处,或者其他导电材料附着至端子处,若相邻端子通过墨水或者导电材料连通,则芯片甚至打印设备可能出现短路故障甚至烧毁。因此,通常会对芯片进行短路校验,当芯片通过短路校验后,打印设备才会给芯片发送后续的正常通讯命令。

3、目前,在芯片的短路校验阶段,打印设备会先给芯片发送短路校验命令,然后芯片中的数据端子回复一个符合打印设备预期的波形,表明芯片未发生短路,否则认为芯片发生短路。但在实际应用过程中,当芯片功能损坏时,在芯片的短路校验阶段,芯片也无法回复一个符合打印设备预期的波形,从而造成芯片短路校验结果认定出错。

4、针对相关技术中存在芯片的短路校验结果认定出错的问题,目前还没有提出有效的解决方案。

技术实现思路

1、在本实施例中提供了一种芯片短路校验方法、装置、芯片检测方法、芯片和耗材盒,以解决相关技术中存在芯片的短路校验结果认定出错的问题。

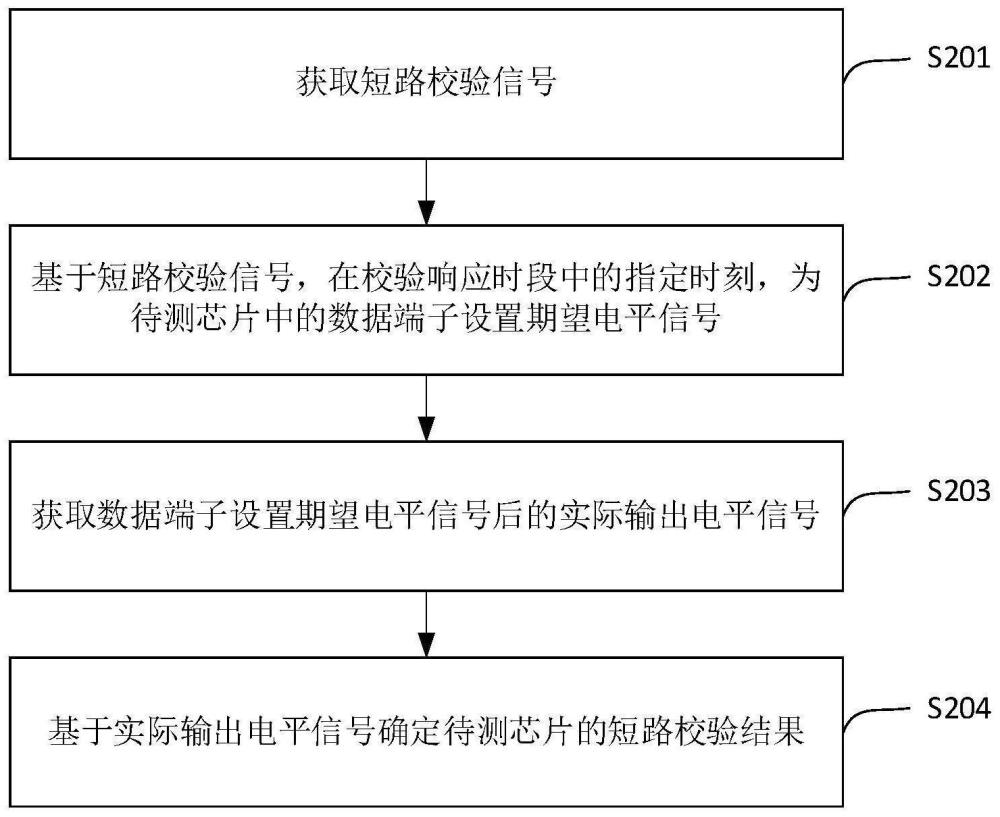

2、第一个方面,在本实施例中提供了一种芯片短路校验方法,包括:

3、获取短路校验信号;

4、基于所述短路校验信号,在校验响应时段中的指定时刻,为待测芯片中的数据端子设置期望电平信号;

5、获取所述数据端子设置期望电平信号后的实际输出电平信号;

6、基于所述实际输出电平信号确定所述待测芯片的短路校验结果,所述短路校验结果包括所述待测芯片功能正常但所述待测芯片中复位端子与除所述复位端子之外的至少一端子存在短路、所述待测芯片功能正常且未短路或所述待测芯片功能损坏。

7、在其中的一些实施例中,所述基于所述实际输出电平信号确定所述待测芯片的短路校验结果,包括:

8、若所述实际输出电平信号与所述期望电平信号不一致,则所述短路校验结果为所述待测芯片功能损坏。

9、在其中的一些实施例中,若所述实际输出电平信号与所述期望电平信号一致,则所述待测芯片功能正常,所述方法还包括:

10、确定所述待测芯片的复位端子的电压,在所述校验响应时间段中是否持续在预设电压范围内;

11、若所述待测芯片的复位端子的电压,在所述校验响应时间段中持续在预设电压范围内,则所述待测芯片未短路;

12、若所述待测芯片的复位端子的电压,在所述校验响应时间段中未持续在预设电压范围内,则所述待测芯片中所述复位端子与除所述复位端子之外的至少一端子存在短路。

13、在其中的一些实施例中,若所述实际输出电平信号与所述期望电平信号一致,则所述待测芯片功能正常,所述方法还包括:

14、在预设通信时间段内确定所述待测芯片是否响应通信指令,所述通信指令为与所述待测芯片通信的打印设备发送的通信指令,所述预设通信时间段在所述校验响应时段之后;

15、若在所述预设通信时间段内,所述待测芯片未响应通信指令,则所述短路校验结果为所述待测芯片功能正常但所述复位端子与除所述复位端子之外的至少一端子存在短路;

16、若在所述预设通信时间段内,所述待测芯片响应通信指令,则所述短路校验结果为所述待测芯片功能正常且未短路。

17、在其中的一些实施例中,所述基于所述短路校验信号,在校验响应时段中的指定时刻,为待测芯片中的数据端子设置期望电平信号,包括:

18、基于所述短路校验信号,确定所述待测芯片中时钟端子的多个时钟时刻;

19、基于多个所述时钟时刻确定校验响应时间段;

20、在所述校验响应时间段中确定所述待测芯片中数据端子对应的指定时刻;

21、在所述数据端子对应的指定时刻设置期望电平信号。

22、在其中的一些实施例中,所述指定时刻包括第一指定时刻、第二指定时刻以及第三指定时刻,所述第一指定时刻早于所述第二指定时刻、所述第二指定时刻早于所述第三指定时刻,所述在所述数据端子对应的指定时刻设置期望电平信号,包括:

23、在所述数据端子对应的所述第一指定时刻设置低电平信号,在所述数据端子对应的所述第二指定时刻设置高电平信号,以及在所述数据端子对应的所述第三指定时刻设置低电平信号。

24、在其中的一些实施例中,所述获取短路校验信号,包括:

25、获取打印设备发送的原始波形数据;

26、若所述原始波形数据存在短路校验标识,则确定所述原始波形数据为短路校验信号。

27、第二个方面,在本实施例中提供了一种芯片短路校验装置,包括:

28、第一获取模块,用于获取短路校验信号;

29、电平信号设置模块,用于基于所述短路校验信号,在校验响应时段中的指定时刻,为待测芯片中的数据端子设置期望电平信号;

30、第二获取模块,用于获取所述数据端子设置期望电平信号后的实际输出电平信号;

31、确定模块,用于基于所述实际输出电平信号确定所述待测芯片的短路校验结果,所述短路校验结果包括所述待测芯片功能正常但所述待测芯片中复位端子与除所述复位端子之外的至少一端子存在短路、所述待测芯片功能正常且未短路或所述待测芯片功能损坏。

32、第三个方面,在本实施例中提供了一种芯片检测方法,所述方法应用在设置有检测部的待测芯片中,所述待测芯片还包括基板、接地端子、时钟端子、数据端子、电源端子以及复位端子;所述检测部,位于所述基板并与所述接地端子电连接,所述检测部包括第一检测线段、第二检测线段以及接地线段,所述第一检测线段通过所述接地线段与所述接地端子连接,所述数据端子和所述复位端子都位于所述第一检测线段的一侧,所述时钟端子和所述电源端子都位于所述第一检测线段的另一侧,所述第二检测线段与所述第一检测线段连接,并将所述时钟端子与所述电源端子间隔布置,所述方法包括:

33、获取短路校验信号;

34、基于所述短路校验信号,在校验响应时段中的指定时刻,为所述待测芯片中的所述数据端子设置期望电平信号;

35、获取所述数据端子设置期望电平信号后的实际输出电平信号;

36、基于所述实际输出电平信号确定所述待测芯片的检测结果,所述待测芯片的检测结果包括所述待测芯片功能正常或所述待测芯片故障。

37、在其中的一些实施例中,所述基于所述实际输出电平信号确定所述待测芯片的检测结果,包括:

38、若所述实际输出电平信号与所述期望电平信号一致,则所述待测芯片的检测结果为所述待测芯片功能正常;

39、若所述实际输出电平信号与所述期望电平信号不一致,则所述待测芯片的检测结果为所述待测芯片故障,所述待测芯片故障包括所述待测芯片中除所述复位端子之外的剩余端子存在短路、所述复位端子与时钟端子和/或电源端子短路、除所述复位端子之外的任一端子与所述检测部短路以及所述待测芯片功能损坏中的至少一种。

40、在其中的一些实施例中,若所述实际输出电平信号与所述期望电平信号一致,所述方法还包括:

41、确定所述待测芯片的复位端子的电压,在所述校验响应时间段中是否持续在预设电压范围内;

42、若所述待测芯片的复位端子的电压,在所述校验响应时间段中持续在预设电压范围内,则所述待测芯片未短路;

43、若所述待测芯片的复位端子的电压,在所述校验响应时间段中未持续在预设电压范围内,则所述待测芯片中所述复位端子与数据端子或接地端子存在短路。

44、第四个方面,在本实施例中提供了一种芯片,包括时钟端子、数据端子、电源端子、接地端子、复位端子和处理单元,所述处理单元用于执行上述第一方面任一项所述的芯片短路校验方法或执行上述第三方面任一项所述的芯片检测方法。

45、第五个方面,在本实施例中提供了一种耗材盒,所述耗材盒包括上述第四方面所述的芯片。

46、与相关技术相比,在本实施例中提供的芯片短路校验方法,在芯片接收到短路校验信号后,芯片进入短路校验阶段,并在短路校验阶段的校验响应时间段中的指定时刻为待测芯片中的数据端子设置期望电平信号,从而可以根据数据端子的实际输出电平信号确定出待测芯片的功能是否损坏的短路校验结果,从而避免芯片在短路校验过程中,无法确定芯片的功能是否损坏导致短路校验结果认定出错的问题。

47、本技术的一个或多个实施例的细节在以下附图和描述中提出,以使本技术的其他特征、目的和优点更加简明易懂。

- 还没有人留言评论。精彩留言会获得点赞!