电能误差检定方法、芯片及误差板与流程

本技术涉及电能误差测量,尤其涉及一种电能误差检定方法、芯片及误差板。

背景技术:

1、在对电能误差进检定时一般会使用到误差板,误差板同时接收标准电能表的标准电能脉冲和被检电能表的被检电能脉冲,然后再结合标准电能表的脉冲常数和被检电能表的脉冲常数,能够计算被检电能表的电能误差。为了使得电能误差的检定更加准备,需要确保检定过程中脉冲计数的准确性和计数同步的准确性。传统技术一般是用标准脉冲和被检脉冲分别出发mcu的外部中断,然后在对应的中断响应函数中对各自的脉冲计数值进行累加。但是,mcu每次在在中断函数中执行判断命令会带来一定的延迟,使得电能误差的计算值与实际值出现偏差。

技术实现思路

1、本技术实施方式主要解决的技术问题是传统技术中电能误差的计算值与实际值存在偏差。

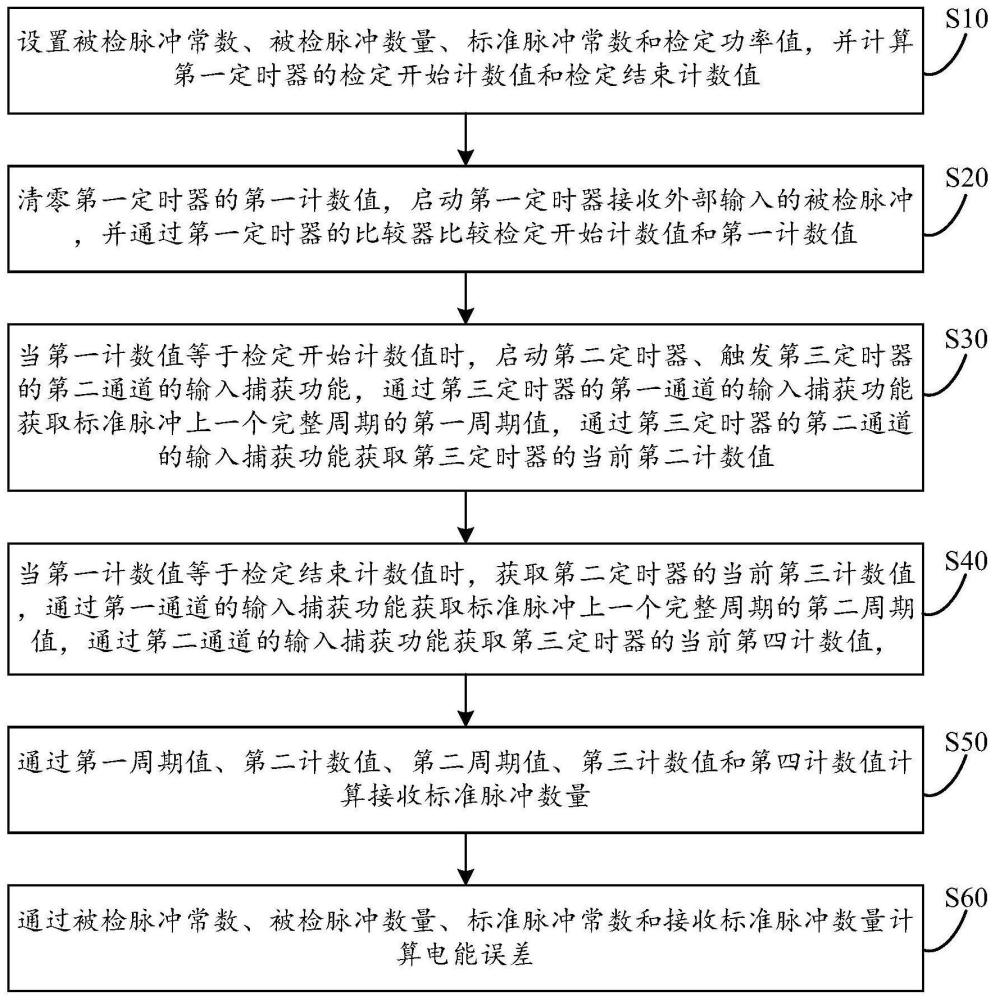

2、为解决上述技术问题,本技术实施方式采用的第一个技术方案是:提供一种电能误差检定方法,包括:设置被检脉冲常数、被检脉冲数量、标准脉冲常数和检定功率值,并计算第一定时器的检定开始计数值和检定结束计数值;清零所述第一定时器的第一计数值,启动所述第一定时器接收外部输入的被检脉冲,并通过所述第一定时器的比较器比较所述检定开始计数值和所述第一计数值,其中,所述第一计数值表示所述第一定时器接收的被检脉冲的数量;当所述第一计数值等于所述检定开始计数值时,启动第二定时器、触发第三定时器的第二通道的输入捕获功能,通过所述第三定时器的第一通道的输入捕获功能获取标准脉冲上一个完整周期的第一周期值,通过所述第三定时器的第二通道的输入捕获功能获取所述第三定时器的当前第二计数值,其中,所述第二定时器的时钟源为标准脉冲,所述第三定时器的时钟源为内部时钟;当所述第一计数值等于所述检定结束计数值时,获取所述第二定时器的当前第三计数值,通过所述第一通道的输入捕获功能获取标准脉冲上一个完整周期的第二周期值,通过所述第二通道的输入捕获功能获取所述第三定时器的当前第四计数值;通过所述第一周期值、所述第二计数值、所述第二周期值、所述第三计数值和所述第四计数值计算接收标准脉冲数量;通过所述被检脉冲常数、所述被检脉冲数量、所述标准脉冲常数和所述接收标准脉冲数量计算电能误差。

3、可选地,所述启动所述第一定时器接收外部输入的被检脉冲,并通过所述第一定时器的比较器比较所述检定开始计数值和所述第一计数值的步骤之后,还包括:若所述检定结束计数值大于所述第一定时器的最大计数值,设置所述检定结束计数值的溢出部分作为所述第一定时器的待溢出次数;当所述被检脉冲数量大于所述第一定时器的最大计数值,且所述第一计数值等于所述检定开始计数值时,关闭所述比较器的比较匹配事件输出功能;当所述第二定时器发生溢出时,将所述第二定时器的溢出计数值加1;当所述第一定时器发生溢出时,判断所述第一定时器的待溢出次数是否大于0,若大于0,则将所述待溢出次数减1;若所述第一定时器的比较匹配事件输出功能被关闭,则在所述第一定时器的后续比较匹配中断响应函数中判断所述第一定时器的待溢出次数是否小于或等于1,若小于或等于1,则重新开启所述比较器的比较匹配事件输出功能。

4、可选地,所述计算第一定时器的检定开始计数值和检定结束计数值的步骤,包括:根据公式(1)计算所述检定开始计数值:

5、

6、其中,p表示所述检定功率值,c表示所述被检脉冲常数,t表示所述检定开始前的同步准备时间,nstart表示所述检定开始计数值;根据公式(2)计算所述检定结束计数值,nstart为大于0且小于所述第一定时器的溢出值之间的整数:

7、nend=nstart+nset (2)

8、其中,nset表示所述被检脉冲数量,nend表示所述检定结束计数值。

9、可选地,所述通过所述第一周期值、所述第二计数值、所述第二周期值、所述第三计数值和所述第四计数值计算接收标准脉冲数量的步骤,包括:根据公式(3)计算所述接收标准脉冲数量的整数部分值:

10、cntstdint=ovft2*novf+cntt2 (3)

11、其中,ovft2表示所述第二定时器的溢出计数值,novf表示所述第二定时器的溢出次数,cntt2表示所述第三计数值,cntstdint表示所述接收标准脉冲数量的整数部分值;根据公式(4)计算所述接收标准脉冲数量的小数部分值:

12、

13、其中,per1表示所述第一周期值,cap1表示所述第二计数值,per2表示所述第二周期值,cap2表示所述第三计数值,cntstddec表示所述接收标准脉冲数量的小数部分值;根据公式(5)计算所述接收标准脉冲数量:

14、cntstd=cntstdint+cntstddec (5)

15、其中,cntstd表示所述接收标准脉冲数量。

16、可选地,所述通过所述被检脉冲常数、所述被检脉冲数量、所述标准脉冲常数和所述接收标准脉冲数量计算电能误差的步骤,包括:

17、根据公式(6)计算所述电能误差:

18、

19、其中,e表示所述电能误差,c1表示所述被检脉冲常数,c2表示所述标准脉冲常数,n表示所述被检脉冲数量,m表示所述接收标准脉冲数量。

20、可选地,所述第三定时器的时钟源频率和标准脉冲的频率满足公式(7):

21、ft3≤fstd*2m (7)

22、其中,ft3表示所述第三定时器的时钟源频率,fstd表示标准脉冲的频率,m表示所述第三定时器的位数。

23、可选地,所述第一定时器的位数等于所述第二定时器的位数,所述第三定时器的位数大于或等于32。

24、为解决上述技术问题,本技术实施方式采用的第二个技术方案是:提供一种电能误差检定芯片,包括第一定时器、第二定时器和第三定时器;所述第一定时器的外部时钟输入端口连接于外部被检脉冲,所述第一定时器的计数值用于累计被检脉冲的数量,当所述第一定时器的计数值等于计算得到的检定开始计数值时,触发所述第一定时器的比较匹配中断以输出检定开始信号,当所述第一定时器的计数值等于计算得到的检定结束计数值时,触发所述第一定时器的比较匹配中断输出检定结束信号;所述第二定时器的外部时钟输入端口连接于外部标准脉冲,当接收到所述检定开始信号时启动计数,累计一次检定过程中标准脉冲的整数部分值,当接收到所述检定结束信号时停止计数;所述第三定时器的时钟源为内部时钟,所述第三定时器的第一通道的输入端口连接于外部标准脉冲,通过所述第一通道的输入捕获和自动清零功能持续地获取标准脉冲上一个完整周期的第一周期值,当接收到所述检定开始信号时触发第二通道的输入捕获,获取所述第三定时器的当前计数值;所述电能误差检定芯片通过所述第一定时器、所述第二定时器和所述第三定时器相互配合,以执行如上所述的电能误差检定方法。

25、为解决上述技术问题,本技术实施方式采用的第三个技术方案是:提供一种误差板,包括如上所述的电能误差检定芯片

26、为解决上述技术问题,本技术实施方式采用的第四个技术方案是:提供一种非易失性计算机可读存储介质,所述非易失性计算机可读存储介质存储有计算机可执行指令,当所述计算机可执行指令被电子设备执行时,使所述电子设备执行如上所述的电能误差检定方法。

27、区别于相关技术的情况,本技术通过设置被检脉冲数量,计算检定开始计数值和检定结束计数值;启动第一定时器接收被检脉冲;当第一计数值等于检定开始计数值时,启动第二定时器、触发第三定时器的第二通道的输入捕获功能,通过所述第三定时器的第一通道获取标准脉冲上一个完整周期的第一周期值,通过第三定时器的第二通道获取第三定时器的当前第二计数值;当第一计数值等于检定结束计数值时,获取第二定时器的当前第三计数值,通过第一通道获取标准脉冲上一个完整周期的第二周期值,通过第二通道获取第三定时器的当前第四计数值;通过获得的前述数据依次计算接收标准脉冲数量、电能误差。不仅进一步简化了用于电能误差检定的电路,使用较少的硬件资源节约了成本,而且通过比较匹配功能界定电能误差检定的开始和结束时刻,并使用内部事件触发功能自动同步,增加了被检脉冲和标准脉冲开始与结束的同步性,进一步提高了电能误差的计算准确度。

- 还没有人留言评论。精彩留言会获得点赞!