一种电流采样电路的制作方法

本技术涉及电路领域,特别涉及一种电流采样电路。

背景技术:

1、目前,在汽车芯片领域,随着汽车芯片的不断发展,尤其例如在汽车微控制单元(mcu,microcontroller unit)开关电源电路中,对开关电源芯片的响应速度提出了更高的要求。

2、相较于采样电压反馈到开关电源芯片中,还需要将电压转换为电流,才能使电源芯片正常工作。直接采样电流反馈到电路电源芯片中,可以提高电路电源芯片的响应速度。

3、因此,电流采样是开关电源电路最重要的单元之一。采样电路采样开关电源电路功率管或电感上的瞬态电流,经过电阻的压降,通过放大器的作用,完成电流采样的过程。

4、然而,传统的电流采样方式是利用电阻采样,受芯片温度和电流以及工艺的影响较大,会引入额外的功率损耗,而且误差较大,不适合汽车微控制单元这种大电流的应用。

5、因此,如何提高开关电源电路中电流采样的精度和速度,实现电路电源芯片的快速准确响应,是本领域需要解决的技术问题。

技术实现思路

1、有鉴于此,提供该

技术实现要素:

部分以便以简要的形式介绍构思,这些构思将在后面的具体实施方式部分被详细描述。该发明内容部分并不旨在标识要求保护的技术方案的关键特征或必要特征,也不旨在用于限制所要求的保护的技术方案的范围。

2、本技术的目的在于提供一种电流采样电路,可以提高开关电源电路中电流采样的精度和速度,实现电路电源芯片的快速准确响应。

3、为实现上述目的,本技术有如下技术方案:

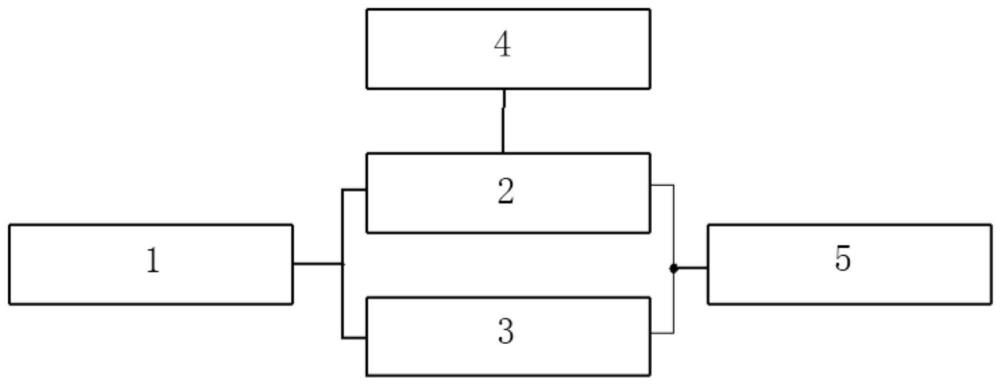

4、第一方面,本技术实施例提供了一种电流采样电路,包括:功率拓扑电路、第一增益电路、第二增益电路、偏置电路和输出电路;

5、所述功率拓扑电路与所述第一增益电路连接,所述功率拓扑电路用于提供开关电源芯片的原始采样电流作为所述第一增益电路的输入;

6、所述第一增益电路与所述第二增益电路连接,所述第一增益电路用于提高所述电流采样电路的单位增益带宽;

7、所述第二增益电路包括源极跟随器,用于控制所述电流采样电路的相位裕度在预设范围内;所述第二增益电路与所述输出电路连接;

8、所述输出电路与所述功率拓扑电路构成镜像电路,用于根据预设比例关系等比例镜像缩小所述原始采样电流,输出镜像采样电流对应的镜像电压;

9、所述偏置电路与所述第一增益电路、所述第二增益电路和所述输出电路分别连接,用于提供所述第一增益电路、所述第二增益电路和所述输出电路的导通电压。

10、在一种可能的实现方式中,所述功率拓扑电路,包括:第一nmos管、第二nmos管、电感、初始电阻和初始电容;

11、所述第一nmos管的漏极与输入电压连接,所述第一nmos管的栅极与第一控制电压连接,所述第一nmos管的源极与第二nmos管和所述电感的负端分别连接;

12、所述第二nmos管的源极与地连接,所述第二nmos管的栅极与第二控制电压连接;

13、所述初始电阻和初始电容并联在所述电感的正端。

14、在一种可能的实现方式中,所述第一增益电路,包括:第三nmos管、第四nmos管、第一pmos管、第二pmos管、第七pmos管、第八pmos管和第一电容;

15、所述第七pmos管、所述第八pmos管、所述第一pmos管和第二pmos管的栅极与所述偏置电路的输出端连接;

16、所述第七pmos管的源极与所述第八pmos管的源极相连于电源电压;

17、所述第七pmos管的漏极与所述第一pmos管的源极相连;所述第八pmos管的漏极与所述第二pmos管的源极相连;

18、所述第一pmos管的漏极、所述第三nmos管的漏极和所述第三nmos管的栅极与所述第四nmos管的栅极相连;

19、所述第三nmos管的源极与所述第二增益电路相连;

20、所述第四nmos管的漏极、所述第二pmos管的漏极与所述第一电容的正端相连作为所述第二增益电路的输入;

21、所述第四nmos管的源极与所述第一电容的负端相连于地。

22、在一种可能的实现方式中,所述第二增益电路,包括:第三pmos管、第四pmos管、第五nmos管和第六nmos管;

23、所述第三pmos管的源极与所述第四pmos管的源极相连于电源电压,所述第三pmos管的栅极与所述偏置电路的输出端连接,所述第三pmos管的漏极与所述第四pmos管的栅极连接;

24、所述第五nmos管的漏极、所述第四pmos管的栅极和所述第三pmos管的漏极相连作为所述第二增益电路的输出,所述第五nmos管的栅极与所述第一增益电路的输出连接,所述第五nmos管的漏极、所述第四pmos管的漏极和所述第六nmos管的漏极相连作为所述第一增益单元的输入;

25、所述第六nmos管的栅极与所述第二控制电压连接,所述第六nmos管的源极与所述功率拓扑电路的输出连接。

26、在一种可能的实现方式中,所述输出电路,包括:第六pmos管、第七nmos管、第八nmos管和第一电阻;

27、所述第七nmos管的漏极与所述第六pmos管的源极相连于电源电压,所述第七nmos管的源极与所述第八nmos管的漏极相连作为所述输出电路的输出;

28、所述第六pmos管的栅极与所述第二增益电路的输出相连接,所述第六pmos管的漏极、所述第一电阻的正端与所述第七nmos管的栅极连接;

29、所述第一电阻的负端和所述第八nmos管的源极均与地连接;所述第八nmos管的栅极与所述偏置电路的输出端连接。

30、在一种可能的实现方式中,所述偏置电路,包括:第九pmos管、第九nmos管、第十nmos管、第十一nmos管、第十pmos管和第十一pmos管;

31、所述第九nmos管的源极与所述第九nmos管的漏极相连于电流源,所述第九nmos管的栅极与所述第九pmos管的栅极相连于使能端;

32、所述第九pmos管的漏极、所述第九nmos管的源极、所述第十nmos管的漏极、所述第十nmos管的栅极与所述第十一nmos管的栅极相连接作为所述第一增益单元的输入;

33、所述第十nmos管的源极与所述第十一nmos管的源极相连于地;

34、所述第十pmos管的栅极、所述第十一pmos管的栅极、所述第十一pmos管的漏极与所述第十一nmos管的漏极相连作为所述偏置电路的输出,所述第十pmos管的源极与电源电压连接,所述第十pmos管的漏极与所述第十一pmos管的源极相连。

35、在一种可能的实现方式中,所述第一增益电路的增益通过以下公式计算得到:

36、av1=gmn4(ron4||ron3);

37、其中,av1为所述第一增益电路的增益,gmn4为所述第四nmos管的跨导,ron4为所述第四nmos管的输出阻抗,ron3为所述第三nmos管的输出阻抗。

38、在一种可能的实现方式中,所述第二增益电路的增益通过以下公式计算得到:

39、

40、其中,av2为所述第二增益电路的增益,gmn5为所述第五nmos管的跨导,ron5为所述第五nmos管的阻抗,ron3为所述第三nmos管的阻抗,rop3为所述第三pmos管的阻抗,ron6为所述第六nmos管的阻抗,rop4为所述第四pmos管的阻抗,gmp4为所述第四pmos管的跨导。

41、在一种可能的实现方式中,所述单位增益带宽通过以下公式计算得到:

42、

43、其中,gbw为所述单位增益带宽,av2为所述第二增益电路的增益,p0为所述第一增益电路的输出频率,c1为所述第一电容的电容值。

44、在一种可能的实现方式中,所述第一增益电路的输出频率通过以下公式计算得到:

45、

46、其中,rop1为所述第一pmos管的输出阻抗。

47、与现有技术相比,本技术实施例具有以下有益效果:

48、本技术实施例提供了一种电流采样电路,包括:功率拓扑电路、第一增益电路、第二增益电路、偏置电路和输出电路;功率拓扑电路与第一增益电路连接,功率拓扑电路用于提供开关电源芯片的原始采样电流作为第一增益电路的输入;第一增益电路与第二增益电路连接,第一增益电路用于提高电流采样电路的单位增益带宽;第二增益电路包括源极跟随器,用于控制电流采样电路的相位裕度在预设范围内;第二增益电路与输出电路连接;输出电路与功率拓扑电路构成镜像电路,用于根据预设比例关系等比例镜像缩小所述原始采样电流,输出镜像采样电流对应的镜像电压;偏置电路与第一增益电路、第二增益电路和输出电路分别连接,用于提供第一增益电路、第二增益电路和输出电路的导通电压。本技术通过提高电流采样电路的单位增益带宽,可以提高开关电源电路中电流采样的速度,通过控制电流采样电路的相位裕度在预设范围内,且将原始采样电流缩小进行采样,可以提高开关电源电路中电流采样的精度和稳定性。

- 还没有人留言评论。精彩留言会获得点赞!