一种芯粒间TSV测试电路及测试方法

本发明属于超大规模集成电路可测性设计领域,具体是涉及一种芯粒间tsv测试电路及测试方法。

背景技术:

1、芯粒(chiplet)技术通过内部tsv等互连技术将多个芯片集成到一个封装中,形成专用功能芯片。芯粒技术的应用避免了过长的连接线问题,实现高性能的片上互连,降低了功耗,拥有更优良的性能。

2、在3d chiplet中,相互堆叠的芯粒通过硅通孔(through silicon via,tsv)连接。在tsv的制造和绑定阶段,由于tsv填充不当或不足,tsv上的微空隙和底部的大空隙,未对准的凸起等,可能会导致各种类型的故障。虽然有些故障可以在绑定前阶段识别,但并非所有tsv故障都可以通过绑定前测试检测出来。此外在芯粒堆叠过程中,还会引入新的缺陷,因此绑定后tsv测试必须进行。但在传统dft测试方法无法在绑定后阶段测试到延迟故障,因为在标准测试访问控制器中数据捕获和数据更新状态之间的间隔超过了一个测试时钟周期,且该测试时钟速率低,因此基于ieee 1149系列的边界扫描测试技术不足以用来检测芯粒间高速互连线的小延迟等故障,并且传统测试方法已不足以满足快速、准确和自动化的需求。此外,给每个tsv配备包装寄存器或者bist的方法需占据大量的面积,生产成本激增。

3、现有技术中也有对此进行的研究,但仍不能达到理想效果;如专利申请tw201101316a,提出了基于bist电路测试tsv的方法,该方法能够实现3d堆叠后对tsv的测试访问,但由于需要对每个待测tsv增添测试电路,导致面积过大;其次,由于该方案同时测试一层中所有tsv,若不将每个tsv的测试响应移出,则无法实现故障定位,但将所有响应移出将导致时间成本激增;最后,该方案只提供了bist测试tsv的电路的方法,bist电路具体如何实现并未进行阐述。

技术实现思路

1、为解决上述技术问题,本发明提供了一种芯粒间tsv测试电路及测试方法,能够检测其连通性、延迟性等,测试过程更加高效,测试时间更短,测试覆盖率更高;内嵌tsv阵列测试控制电路,测试过程高度自动化,对测试机台的依赖性大大降低,芯粒测试成本下降。

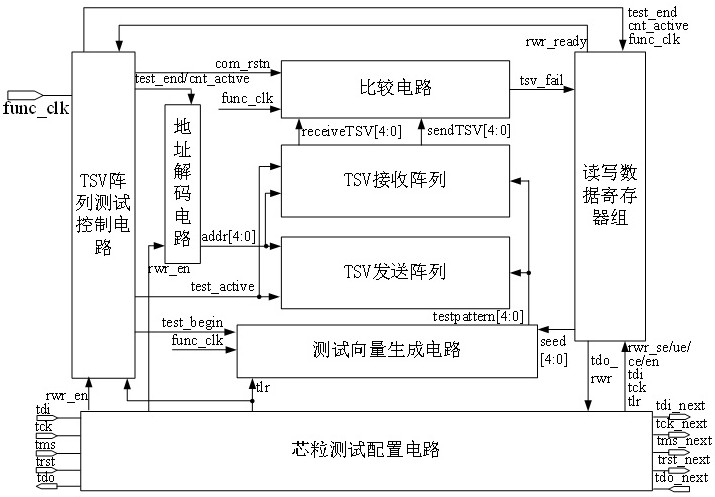

2、本发明所述一种芯粒间tsv测试电路,包括芯粒测试配置电路、读写数据寄存器组、tsv阵列测试控制电路、地址解码电路、测试向量生成电路、比较电路、tsv接收阵列和tsv发送阵列;

3、所述芯粒测试配置电路,与相邻芯粒的测试端口连接,用于配置测试路径、测试指令和读写数据寄存器;

4、所述读写数据寄存器组,用于接收来自外部端口的测试向量和捕获测试响应,对tsv阵列测试控制电路进行激活;

5、所述tsv阵列测试控制电路,在功能时钟func_clk的作用下,控制地址解码电路逐行选择待测tsv,控制tsv测试的初始化、测试、捕获操作;

6、所述测试向量生成电路用于自动生成tsv测试所需的测试向量;

7、所述tsv接收阵列和tsv发送阵列用于控制测试向量在tsv上的发送与接收;

8、所述比较电路用于进行测试结果的判断以及读写数据寄存器组捕获测试响应,并将测试响应传出观测。

9、进一步的,所述读写数据寄存器组由n位具有移位、捕获和更新功能的测试数据寄存器组组成;

10、最低位测试数据寄存器组的测试数据输入端tdi与外部测试数据输入端口相连,功能输入端pi与比较电路的输出端口tsv_fail相连,其余位的测试数据寄存器组的测试数据输入端和功能输入端均与相邻低位的测试数据输出端tdi_rwr相连,最高位的测试数据输出端口tdo_rwr作为读写数据寄存器组的输出端口;

11、测试数据寄存器组中负责更新功能的寄存器ureg输出端口从低位到高位分别作为读写数据寄存器组的输出端口seed[0]-seed[n-1];当seed[n-1:0]=n’b 1时,输出端口rwr_en=1;

12、n位测试数据寄存器组的负责移位和捕获功能的寄存器screg的时钟输入端均与mux4的输出端相连,mux4的数据选择输入端为输入端口cnt_active,0输入端为输入端口tck,1输入端为与门and1的输出端,与门and1的输入端为输入端口test_end,另一个输入端为输入端口func_clk;ureg的时钟输入端均与非门not1的输出端相连,not1的输入端为t输入端口tck。

13、所述读写数据寄存器组,其screg在移位使能信号有效(rwr_se=1)时,移入测试向量或移出测试响应,在捕获使能信号有效(rwr_ce=1)时,最低位从比较电路捕获1位测试响应,其余位捕获相邻低位保存的测试响应, ureg在更新使能信号有效(rwr_ue=1)时,保存测试向量,以便在捕获阶段时,保证测试向量不变。当tsv阵列数据控制电路的输出信号cnt_active=0时,screg的时钟端由外部测试信号tck控制,当cnt_active=1时,screg的时钟输入端为功能时钟func_clk和tsv阵列数据控制电路的输出信号test_end相与,即在tsv阵列数据控制电路处于有效状态时,在行tsv测试的最后一个时钟给screg打入一个时钟脉冲,用于捕获测试响应。ureg的输出端为测试向量生成电路的初始测试向量seed[n-1:0],用于激活测试向量生成电路,当有效测试数据n’b1更新到ureg寄存器组,输出使能信号rwr_ready=1。

14、进一步的,所述tsv阵列测试控制电路,包含三个输入端口func_clk、rwr_ready、tlr,五个输出端口com_rstn、test_begin、test_active、test_end、cnt_active,以及长度为2n+1位的计数器;计数器的复位端为输入端口tlr,时钟输入端为func_clk与rwr_ready相与,即当rwr_ready=1时,计数器在功能时钟func_clk的作用下开始计数,其输出cnt[n:0]为计数值,输出端口cnt_active在开始计数后的(2n +1)×n-1个时钟内为1,否则为0。

15、所述tsv阵列测试控制电路,将tsv测试分为三个阶段,第一个阶段为测试初始化阶段,在第一个计数周期,即cnt=6’b0阶段,输出端口comrst_n=0,此时比较电路的复位端有效,比较电路的值清零;输出端口test_begin=1,此时测试向量生成电路选择读写寄存器组的seed值并行输入,用于初始化测试向量生成电路。在cnt处于第二个到倒数第二个计数周期时,为tsv测试阶段,此时输出端口active_test=1,tsv接收阵列和tsv发送阵列开启测试模式。在cnt处于最后一个计数周期时,为测试捕获阶段,输出端口test_end=1,写寄存器组捕获测试响应且地址解码电路选择下一行tsv以便进行下一次测试。由于tsv阵列为n×n的矩阵,当cnt进行n次2n+1位的计时后便结束计数,并且最后一次捕获由芯粒测试配置电路完成,因此只需工作(2n +1)×n-1个周期,cnt_ative=1用于标记计数器工作状态。

16、进一步的,所述地址解码电路由n位移位计数器构成,移位计数器的时钟输入端口连接与门and2的输出端,and2的一个输入端连到输入端口test_end,另一个接到输入端口func_clk,即在tsv阵列测试控制电路的测试捕获周期打入一个时钟脉冲,将有效值1向高位移动一位,以便开启下一次测试;非门not2的输入端为输入端口cnt_active,输出端口接入与门and3的输入端;与门and3的另一个输入端为输入端口rwr_en,输出端接到移位计数器最低位的置1端;或门or1的一个输入端连接到与门and3的输出端,另一个输入端接到非门not3的输出端,输出端接到移位计数器高n-1位的寄存器的清0端;非门not3的输入端为输入端口rwr_en,输出端接到移位计数器最低位的清0端;输出端口为addr[n-1:0];有效的地址输出值为有且只有一位为1,当addr[t]=1时,则选择第t行tsv开启测试。

17、所述地址解码电路,可以分为三种工作状态,一是未选择tsv测试模式,即rwr_en=0,此时移位计数器的n个寄存器清0端均有效,地址解码电路输出全0,tsv处于正常工作状态;二是已选择tsv测试模式但tsv测试还未进行,即rwr_en=1且cnt_active=0,seed值还没有传入到读写寄存器组,tsv阵列控制电路未开始工作,此时最低位的置1端有效,其余位的清零端有效,地址解码电路输出为n’b1,地址位选择第一行tsv准备进入测试状态;三是tsv测试阶段,即rwr_en=1且cnt_active=1,移位计数器的n个寄存器的置位端均无效,移位计数器开始工作,每测试完一行tsv后,在测试捕获周期,寄存器时钟端打入一个脉冲,有效值1右移,选择下一行tsv准备进入测试状态。

18、进一步的,所述tsv接收阵列由n×n接收tsv构成,包含n(n+1)个与门和n个或门,输入端口为来自地址解码电路的addr[n-1:0]、测试向量生成电路的testpattern[n-1:0]、tsv阵列测试控制电路test_active和来自其他芯粒的输入值tsv[n2-1:0],输出端口为sendtsv[n-1:0]和reveivetsv[n-1:0];

19、所述tsv接收阵列中,每一个接收tsv均与对应第i,0<i<6行的地址解码位addrn相与,用以屏蔽非测试行tsv接收到的值,将每一列的与门输出值相或作为第j,0<j<6列的输出端口receivetsv[j],因此输出端口receivetsv[n-1:0]代表所测行tsv接收到的值;将testpattern[n-1:0]输入值分别于test_active相与作为输出端口sendtsv[n-1:0],代表每一列的测试数据值;将receivetsv[n-1:0]和testpattern[n-1:0]值传入比较电路进行判断是否存在故障。

20、进一步的,所述tsv发送阵列由n×n发送tsv构成,包含n2个二选一数据选择器和n个与门,输入端口为来自地址解码电路的addr[n-1:0]、测试向量生成电路的testpattern[n-1:0]和tsv阵列测试控制电路test_active,输出端口为传到其他芯粒的输出值tsv0[n2-1:0];

21、所述tsv发送阵列中,每一个连接其他芯粒的功能输出值连入二选一数据选择器的0输入端,1输入端连接tsv所在列对应的testpattern与test_active的与值,选择输入端连接tsv所在行的地址解码位,输出端作为输出端口tsv[n2-1:];因此在正常工作模式下,传入tsv的值为原始功能电路输出,在测试模式下,待测行输出测试向量值到tsv开始测试。

22、进一步的,所述比较电路包括n级比较单元和n-1个或门;所述比较单元包括异或门xor1、或门or2、d触发器reg1,输入端口为sendtsv、receivetsv、func_clk、com_rstn,输出端口为tsv_fail;异或门xor1的输入端为输入端口sendtsv和receivetsv,输出端连接到或门or2的输入端;或门or2的另一个输入端连接d触发器reg1的输出端,输出端连接d触发器reg1的d输入端;d触发器reg1的时钟输入端为输入端口func_clk,清零端为输入端口com_rstn,输出端为输出端口tsv_fail;

23、n级比较单元的sendtsv和receivetsv端口从低位到高位分别与来自tsv输出阵列的sendtsv[n-1:0]和receivetsv[n-1:0]连接,func_clk和com_rstn均与输入端口func_clk和com_rstn端口连接;通过n-1个或门将比较单元高位的输出端口与其低位所有输出端的或值相连接,作为比较电路的输出端口tsv_fail;

24、所述比较电路负责判断当前测试的行tsv中是否存在故障,若存在故障则输出端tsv_fail=1,否则tsv_fail=0。阵列控制电路的输出端口com_rstn下,在tsv测试初始化阶段将所有d触发器清0;在tsv测试阶段,将测试行中每一个tsv的发送值和接收值传入对应的比较单元,通过将传播前的值sendtsv和经过tsv传播后的值receivetsv通过异或门比较,存入d触发器中,若sendtsv的值与receivetsv的值不同,则表示该tsv存在故障,否则不存在,最后输出值为每一级比较单元的或值,表示该行是否存在故障。

25、一种芯粒间tsv测试方法,基于所述测试电路实现,包括以下步骤:

26、步骤1、测试电路复位;

27、步骤2、配置测试路径,打开待测tsv所连接的两个芯粒的测试路径;

28、步骤3、配置测试指令,选择tsv测试模式;

29、步骤4、配置读写寄存器,将所需seed通过tdi端口传入读写寄存器组并保持不变;

30、步骤5、tsv测试初始化,比较电路清0,测试向量生成电路打入初始值;

31、步骤6、tsv测试,测试向量生成电路生成伪随机序列进入tsv阵列测试,比较电路判断测试是否通过;

32、步骤7、判断当前测试行是否为第n行,否则进入步骤8、是则进入步骤9;

33、步骤8、在tsv阵列测试控制电路下进行测试响应捕获,测试解码电路更新,返回步骤5;

34、步骤9、在芯粒测试配置电路控制下进行测试响应捕获;

35、步骤10、测试响应移出观测。

36、本发明所述的有益效果为:本发明所述的芯粒间tsv测试电路能够在功能时钟下进行tsv连通性、延迟性等测试,解决了低速测试时钟测试无法覆盖微小缺陷导致延迟故障的问题,测试过程更加高效,测试时间更短,测试覆盖率更高,提高了测试的效率和生产效率;由于采用tsv阵列的方法进行测试,无需对每一个tsv插入测试向量生成单元和测试比较单元,不同行tsv复用同一组测试电路,测试电路在设计上更加紧凑和高集成度,这种集成性减少了电路面积的占用,降低了成本,同时也有利于更好地适应大规模集成的芯粒系统和高性能计算系统的需求;所述测试电路最外部仅由5个jtag端口控制,无需增加新的测试端口,提供了一种标准化的测试方案,解决了来自不同厂商的芯粒难以进行测试控制与访问的问题;由于内嵌tsv阵列测试控制电路,测试过程高度自动化,并且由于不依赖于外部测试向量进行测试,对测试机台的依赖性大大降低,芯粒测试成本下降。

- 还没有人留言评论。精彩留言会获得点赞!