一种CMOS图像传感器芯片测试系统的制作方法

本发明涉及芯片测试系统领域,具体是一种cmos图像传感器芯片测试系统。

背景技术:

1、随着我国工业、航天、交通、消费等领域的迅猛发展,对图像采集设备需求日益旺盛。而cmos图像传感器芯片,作为图像采集设备的核心,出货量极大。

2、目前cmos芯片传统的测试方案一是使用ic封测厂的标准化测试流程,按照ic的测试标准进行高速信号标准的测试,测试流程复杂,费用昂贵。另外一种方案则是直接在产品中试用并测试cmos芯片,这样做一方面测试环境单一,无法对鲁棒性、误码率、丢帧率、错帧率等进行测试。

3、现有技术申请号为202011001452.3的中国专利:一种cmos图像传感器的测试装置,其公开了一种基于fpga主控芯片构建的cmos图像传感器的测试系统,其中fpga主控芯片用于驱动cmos图像传感器工作,以及接收cmos图像传感器产生的图像数据,同时fpga还通过camera-link输出模块输出测试结果和图像数据。该专利中主要是利用fpga可编程的特性,使构建的测试装置能够适用于不同型号的cmos图像传感器。但由于该专利中fpga不仅要驱动cmos图像传感器工作、接收图像数据进行存储和处理,同时fpga还需要向外输出处理结果和图像数据,因此无疑fpga的任务量较重,所需资源较多,会导致成本上升,整体测试周期长的问题。另外,该专利中声称利用fpga的现场编程特性,针对不同型号的cmos图像传感器需要重新做定制化开发,因此除了fpga母板硬件复用外,固件和软件的复用性并不高。而且,该专利所采用的camera-link并不属于pc机的常用接口,需要在机箱中安装额外的图像采集卡来实现图像数据的接收,且需要pc机上开发相应的驱动软件和分析软件,因此pc机成本昂贵。

技术实现思路

1、本发明的目的是提供一种cmos图像传感器芯片测试系统,以解决现有技术cmos图像传感器芯片测试时存在的问题。

2、为了达到上述目的,本发明所采用的技术方案为:

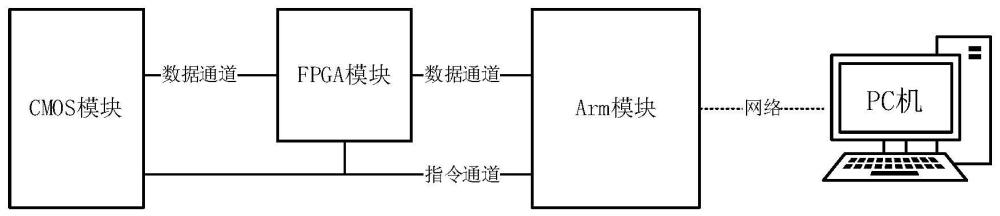

3、一种cmos图像传感器芯片测试系统,包括cmos模块、fpga模块、arm模块,arm模块与fpga模块电连接,所述cmos模块供待测cmos图像传感器芯片电连接,所述arm模块、fpga模块分别通过cmos模块与待测cmos图像传感器芯片电连接,其中:

4、所述arm模块分别向fpga模块、cmos模块传输控制指令数据,所述cmos模块接收控制指令数据时产生相应控制信号并加载至待测cmos图像传感器芯片,使待测cmos图像传感器芯片工作产生原始图像数据;

5、所述fpga模块接收控制指令数据时接收待测cmos图像传感器芯片产生并通过cmos模块传输的原始图像数据,由fpga模块对原始图像数据进行误码率、丢帧率和错帧率的计算;

6、当fpga模块计算的误码率、丢帧率和错帧率三者均为零,则fpga直接将原始图像数据和误码率、丢帧率、错帧率计算结果传输至arm模块;当fpga模块计算的误码率、丢帧率和错帧率其中之一不为零时,则由fpga模块先对原始图像数据重新封装同步码后,再将封装后的图像数据传输至arm模块。

7、进一步的,还包括pc机,所述pc机通过网络连接arm模块。

8、进一步的,所述cmos模块包括cmos芯片接口、cmos芯片控制信号模块、电源模块,其中cmos芯片接口至少包括与待测cmos图像传感器芯片电源端电连接的电源端接口、与待测cmos图像传感器芯片控制信号端电连接的控制端接口、与待测cmos图像传感器芯片数据输出端电连接的数据端接口;

9、cmos模块中,电源模块通过cmos芯片接口的电源端接口与待测cmos图像传感器芯片电源端电连接,由电源模块向待测cmos图像传感器芯片供电;

10、cmos模块中,cmos芯片控制信号模块的输出端通过cmos芯片接口的控制端接口与待测cmos图像传感器芯片的控制信号端电连接,cmos芯片控制信号模块的输入端与arm模块电连接,所述cmos芯片控制信号模块接收arm模块输出的控制指令数据,并由cmos芯片控制信号模块产生控制信号加载至待测cmos图像传感器芯片;

11、所述fpga模块通过cmos芯片接口的数据端接口与待测cmos图像传感器芯片的数据输出端电连接,待测cmos图像传感器芯片产生的原始图像数据通过cmos芯片接口传输至fpga模块。

12、进一步的,所述cmos模块中的cmos芯片控制信号模块包括偏置电压电路、时钟发生器,所述偏置电压电路接收arm模块输出的控制指令数据时产生偏置电压加载至待测cmos图像传感器芯片,所述时钟发生器接收arm模块输出的控制指令数据时产生时钟信号加载至待测cmos图像传感器芯片。

13、进一步的,所述cmos模块中的电源模块为电压可调的电源模块。

14、进一步的,所述cmos芯片接口为掀盖式接口。

15、进一步的,所述fpga模块通过识别原始图像数据中的同步码,结合行同步、场同步以判定行场数据,然后基于行场数据分别计算丢帧率和错帧率;arm模块控制cmos输出测试图像,fpga模块将接收到的图像数据与预存的测试码进行运算得到误码率。

16、进一步的,所述cmos模块、fpga模块、arm模块彼此之间连接排线采用软排线。

17、本发明中,由arm模块分别向cmos模块和fpga模块发送控制指令数据,其中cmos模块基于控制指令数据产生控制信号令待测cmos图像传感器芯片工作,fpga模块基于控制指令数据采集待测cmos图像传感器芯片输出的原始图像数据并进行处理。可见本发明中,对待测cmos图像传感器芯片的实际驱动时由cmos模块进行的,fpga模块负责接收原始图像数据并处理,而原始图像数据和fpga的处理结果由arm模块接收,pc机为非必需模块,当离线测试时需要查看和导出测试结果和图像数据,使用arm查看实时测试结果和图像数据,再通过网络传输至pc机。因此本发明实际上是多核的测试系统,各个核心分别分担相应的工作过程,每个核心的工作任务较轻,处理任务的时间因此较短,因此整体测试效率高。

18、同时,本发明中,fpga基于原始图像数据能够计算得到误码率、丢帧率和错码率,并将计算结果传输至pc机,使pc机能够进一步得到更为准确的测试结果。

19、同时,由于arm模块接收数据时靠的是数据中带有的同步码,当待测cmos图像传感器芯片内部有故障时,可能待测cmos图像传感器芯片连同步码都无法正确输出,这时arm模块是无法进行数据传输的。本发明中针对cmos图像传感器芯片在故障时(即存在误码率、丢帧率和错码率其中至少一者时),arm模块无法传输数据的问题,在fpga模块中增加故障判断,即基于误码率、丢帧率和错码率进行判断,若判断存在故障时(即存在误码率、丢帧率和错码率其中至少一者不为零),由fpga模块对原始图像数据进行重新封装同步码,然后再传输至arm模块,最后由arm模块传输至pc机。通过上述方式,可确保整个数据链路的通畅,不会出现cmos图像传感器芯片故障时无法得到测试结果的问题。

20、相比现有技术,本发明fpga功能明确,且预留了参数配置接口,当需要修改时,只需修改arm模块中json配置文件即可。并且,本发明arm模块做主控,系统可以在不依赖pc机的情况下进行测试,最后通过网络传输给远程pc机,本发明系统尤其适用于狭小密闭空间等无法安装pc机的场景下的测试。arm模块和pc机仅在需要时通过网络传输数据,而网络接口是每个pc机都具备的接口,且图像的处理和计算在fpga模块和arm模块中已经做掉,对pc机的性能要求极低。

21、因此,本发明相比现有技术,具有测试效率高、测试过程可靠、测试准确率高、测试场景丰富(可脱离pc机离线测试)、测试成本低的优点。

- 还没有人留言评论。精彩留言会获得点赞!