一种基于FPGA的星载数字相关器使用资源评估方法与流程

本发明涉及空间微波遥感领域,特别涉及一种基于fpga的星载数字相关器使用资源评估方法。

背景技术:

1、随着科技的发展,二维综合孔径微波辐射计技术被应用于卫星有效载荷,用于对陆地水资源等信息进行观测。该技术利用多个接收天线接收微波信号,并通过综合处理这些信号来获得更高的分辨率。相比较传统的单天线微波辐射计,该技术可以提供更准确的观测结果,并且可以减小有效载荷体积。

2、为了获取较大的观测视场,二维综合孔径阵列单元数量往往较大,因此,相关运算单元数量也较大。考虑到fpga开发的快速性、便利性和灵活性,星载领域的数字相关器一般使用fpga进行开发。为了进一步减少使用资源、降低功耗,星载领域的数字相关器常使用1bit量化值来计算相关系数。尽管如此,由于fpga的运算数量巨大,所产生的功耗也巨大。功耗的增加,会导致芯片温度快速上升,不仅会带来温度的漂移,甚至会造成芯片的损坏。其中,温度漂移会使微波辐射计测得的观测亮温值具有较大的误差。

3、相关计算可通过乘累加方式实现,具体地可利用fpga的dsp48e运算单元来实现,因为dsp48e在运算速率和功耗方面,具有较大的优越性。然而,dsp48e数量相对有限,随着数量的增大,成本呈指数性增长。

4、假设相关器的输入通道为60路,则需要路互相关和自相关计算。其中,每路相关运算包括一个复数乘法器,每个复数乘法器需要消耗4个dsp48e运算单元。对于60通道的数字相关器来说,则至少需要使用7320个dsp48e运算单元。这在成本和资源利用率上都不可接受。

5、发明专利cn106093884a提出了一种改进的基于fpga的多通道相关处理实现方法,发明专利cn112487354a提出了一种基于比较器的fpga的多通道高速实时互相关运算装置。这些专利的核心思想是:(1)采用串并转换累加电路以解决fpga内部逻辑工作时钟频率低于采样时钟频率的问题;(2)使用多级累加器进行数据处理来降低累加运算的逻辑资源使用量。然而上述专利所涉及的方法并没有对使用资源进行理论计算和有效评估。此外,星载领域中的散热方式一般为传导散热,散热条件有限,因此在星载领域需对fpga进行资源评估,以充分利用资源,降低功耗。

技术实现思路

1、为了克服现有技术中的不足,本发明提供一种基于fpga的星载数字相关器使用资源评估方法,为星载微波辐射计数字相关器的前期开发、选型提供理论支撑和指导,该方法不需要提前编写代码并放入fpga开发环境中进行“综合”、“实现”等操作,可有效缩短研发周期、提高效率、降低开发成本。

2、为了达到上述发明目的,解决其技术问题所采用的技术方案如下:

3、一种基于fpga的星载数字相关器使用资源评估方法,包括以下步骤:

4、步骤1:n路中频输入信号为二维综合孔径天线阵列接收的射频信号,经过信号处理变换,再由ad芯片同步采集而输出的数字中频信号;

5、步骤2:控制信号为数字相关器提供积分周期时间戳;

6、步骤3:输出信号将每个积分周期内不同通道之间的相关运算累加值输出到后续处理单元,共路相关数据;

7、步骤4:电源模块为数字相关器单机提供电能。

8、进一步的,步骤3包括以下内容:

9、步骤31:数字相关器接收n路中频输入信号,并实施两两通道之间的相关数据处理计算;

10、步骤32:采用串转并的方式,降低数据处理的速度,将每个通道连续接收的48bit串行数据同时并行处理;

11、步骤33:数字相关器使用控制信号对一个积分周期内所有相关处理运算单元输出的相关值进行累加并输出至后续单元。

12、进一步的,步骤31包括以下内容:

13、步骤311:在数字相关器单机内部,主要实现任意两个通道的复数相关运算,两信号之间的相关运算可以表示为:

14、

15、在星载领域中,一般取τ=0,且x(n)和y(n)为复数离散序列;

16、在fpga实现过程中,一次复数相关运算等同于4次乘法运算和2次加法运算,输入的每路复数信号分别由1bit i路和1bit q路数据组成,将复数相关处理单元采用一个4输入2输出的查找表lut4-2来实现;

17、步骤312:所述4输入2输出查找表的4个输入分别对应i1、q1、i2、q2,当数字相关器使用1bit量化值来计算相关系数时,i1、i2只有两种取值,即1和-1;q1、q2亦只有两种取值,即j和-j,在fpga实现时,i1、i2的两种取值和q1、q2的两种取值都分别用1和0表示;

18、步骤313:所述4输入2输出的查找表的2输出可由2bit数据位表示,即00表示2,01表示-2,10表示2j,11表示-2j。

19、进一步的,步骤32包括以下内容:

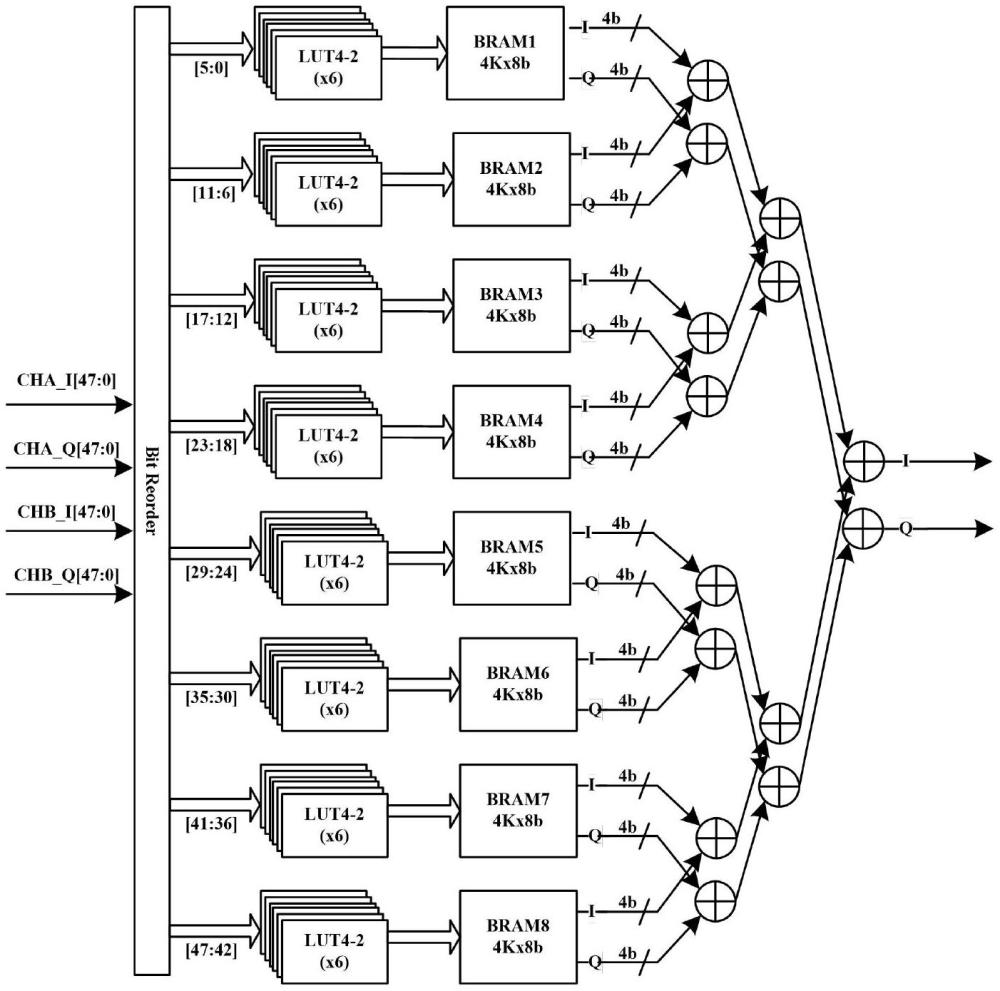

20、步骤321:ch1对应的i1和q1和ch2对应i2和q2均由连续的48bit组成,将48bit数据分为8组,每组6个bit,即数据位[5:0]为第一组,数据位[11:6]为第二组,依此类推,因此,8组中的每一组都需使用6个lut4-2资源,6个lut4-2的输出位数一共为6*2bit=12bit,同时,6个lut4-2输出结果的真实累加值可用8bit来表示,其中,前4位表示实部,后4位表示虚部,继而,6个lut4-2输出结果的累加值可用一个12输入8输出的lut(lut12-8)来表示,而1个lut12-8等效于2^12*8bit的ram,即一个4k*8bit的ram;

21、步骤322:block ram的基本单元为36kb,可以配置为4k*9bit,当用于例化上述4k*8bit的ram时,效率可达88.9%;

22、步骤323:将block ram输出的4bit实部数据和4bit虚部数据分别进行加法运算,采用逐步累加的方式,首先将组1-2,组3-4,组5-6,组7-8的实部和虚部分别进行相加,使用了8个加法器;其次分别将组1-4和组5-8的实部和虚部分别相加,再使用4个加法器;最后将组1-8数据的实部和虚部分别进行相加,再使用2个加法器,一共使用了14个加法器,而fpga内部每个dsp48e资源可实现4个独立的2输入加法器,因此,14个加法器只需要使用4个dsp48e资源;

23、步骤324:每个相关处理运算单元需要使用48个lut4-2,4个dsp48e和8个36kblock ram,或16个18k block ram。

24、进一步的,步骤33包括以下内容:

25、步骤331:假设一片fpga能处理m个复数相关处理运算单元,采用一个深度为m的block ram作为相关累积结果的存储器,每完成一次48个采样点复数相关累加运算,就把对应地址的相关累加结果存储值读出,然后与当前48个采样点复数相关累加结果相加,求和的结果再存入相应地址,即完成累加运算,按照实部和虚部各32bit设计,需要m*64bit的存储器,此存储器可以由t个block ram拼接而成;

26、步骤332:输入通道n、相关处理运算单元m、存储空间位数s、block ram个数t18k(或t36k)的关系如下:

27、

28、s=m×64

29、

30、式中,ceil表示向上取整;

31、步骤333:数字相关器使用所述的控制信号对一个积分周期内m路相关值进行累加,通过时分复用的方式,m路相关值共用2个加法器,每个dsp48e中含有2个加法器,因此整个数字相关器需要额外使用1个dsp48e资源;

32、步骤334:所述基于fpga的星载数字相关器使用的总资源至少为:m*48个lut4-2、m*4+1个dsp48e、m*8+t36k个36k block ram或m*16+t18k个18k block ram。

33、本发明由于采用以上技术方案,使之与现有技术相比,具有以下的优点和积极效果:

34、1、本发明面向fpga的lut、dsp48e和block ram关键资源模块进行相关算法设计,可充分利用fpga的核心资源;

35、2、本发明提出的对输入通道进行串并转换方法,和传统串并转换累加电路相比,转换后的数据不再进行累加,而是使用lut处理,从而降低fpga内部工作时钟频率;

36、3、本发明提出了一种新型数字相关器实现方法,优化了fpga运算逻辑,提高了资源使用率,并对使用资源进行了最优分配;

37、4、本发明为数字相关器fpga使用资源的评估提供了理论支撑和指导性方法,有效缩短了研发周期、提高了效率、降低了开发成本。此外,合理的资源使用率可有效降低fpga的功耗,提高了卫星有效载荷的可靠性。

- 还没有人留言评论。精彩留言会获得点赞!