一种芯片的测试方法与流程

本技术涉及半导体,具体而言,涉及一种芯片的测试方法。

背景技术:

1、先进工艺芯片(例如hbm芯片)在晶圆级测试较为成熟,在芯片级测试则没有很好的方案。

2、以hbm芯片为例,hbm芯片即高带宽内存(high bandwidth memory)芯片,是一种基于3d堆栈工艺的高性能dram,专为满足高性能计算、人工智能和图形处理等领域对内存带宽和容量的高需求而设计。hbm是一种新型的内存芯片技术,通过垂直堆叠多个dram芯片并使用硅通孔(tsv)和微凸块等先进封装技术,实现高速、高带宽的内存访问。

3、hbm芯片的制造过程主要包括:对memory core晶圆进行减薄和凸点形成,再切割得到多个裸片;对逻辑晶圆进行减薄和凸点形成;将多个裸片堆叠在逻辑晶圆上,得到堆叠后晶圆;对堆叠后晶圆进行切割和晶圆解键合或剥离,得到多个堆叠裸芯片,将这些堆叠裸芯片进行卷带包装后进入批量出货的后续流程。

4、现有技术对hbm芯片的测试主要包括:对memory core晶圆的测试,对逻辑晶圆的测试,以及对堆叠后晶圆的测试。然而,hbm芯片的制造过程中,在得到堆叠后晶圆之后,还进行了晶圆切割和晶圆解键合或剥离,这个过程中可能产生不合格的hbm单元,这些不合格的hbm单元被组装到2.5d封装中,导致产品的良率下降。

技术实现思路

1、本技术实施例的目的在于提供一种芯片的测试方法,用以解决现有技术仅进行晶圆级测试,无法检测出晶圆切割后的不合格裸芯片,导致产品的良率下降的技术问题。

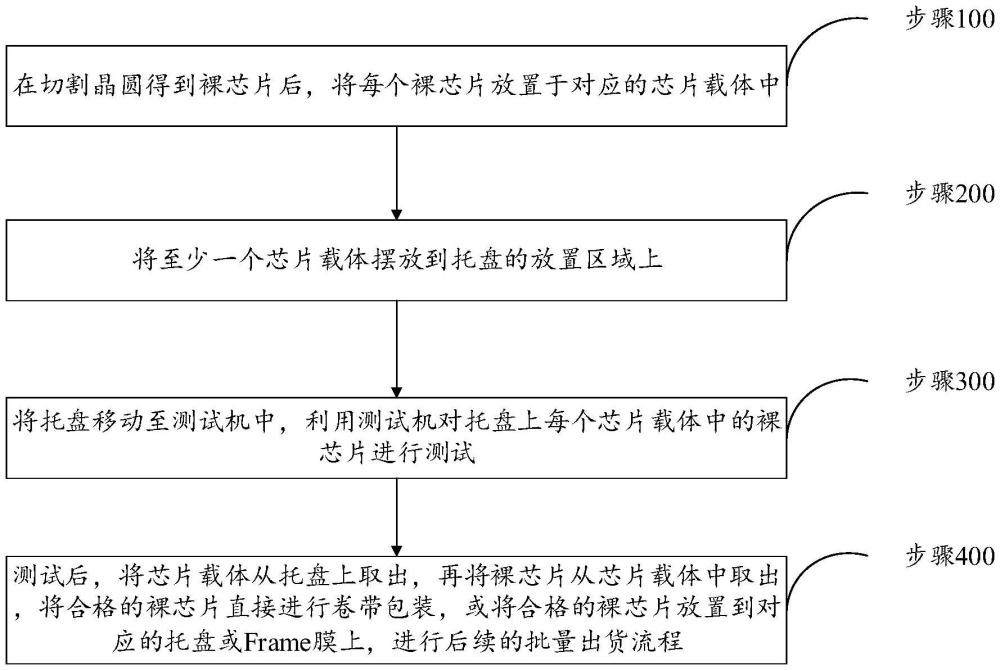

2、本技术实施例提供的一种芯片的测试方法,包括:

3、在切割晶圆得到裸芯片后,将每个裸芯片放置于对应的芯片载体中;其中,裸芯片的凸点或测试焊点之间的间距,小于芯片载体的探测焊盘之间的间距;

4、将至少一个芯片载体摆放到托盘的放置区域上;

5、将托盘移动至测试机中,利用测试机对托盘上每个芯片载体中的裸芯片进行测试。

6、上述技术方案中,通过在晶圆切割后,对单个裸芯片进行测试,能够更准确地识别出那些在晶圆级测试中可能未被发现的缺陷或不合格品。这些缺陷可能是在晶圆切割过程中引入的,如切割损伤、污染等。因此,该测试方法能有效提升最终产品的良率,减少因不合格裸芯片流入后续生产环节而造成的资源浪费和成本增加。将裸芯片放置于芯片载体中,再将芯片载体摆放到托盘上,通过托盘进行批量测试,这种设计使得测试过程更加灵活,可以根据不同的裸芯片设计不同的芯片载体,不同的芯片载体都可以摆放到托盘中,能够兼容不同裸芯片的测试。并且,芯片载体的探测焊盘之间的间距相对较大,使得测试机能够通过探测焊盘来测试裸芯片。

7、在一些可选的实施方式中,利用测试机对托盘上每个芯片载体中的裸芯片进行测试之后,还包括:

8、测试后,将芯片载体从托盘上取出,再将裸芯片从芯片载体中取出,将合格的裸芯片直接进行卷带包装及后续的批量出货流程。

9、上述技术方案中,芯片载体是摆放到托盘上的,非常容易地从托盘上取出芯片载体,并且,裸芯片放置于芯片载体中,也可以从芯片载体中取出裸芯片,托盘和芯片载体都能够重复利用,托盘和芯片载体的可重复利用性显著减少了生产过程中的材料消耗和废弃物产生,符合可持续发展的理念,有助于降低生产成本,并减少对环境的影响。

10、在一些可选的实施方式中,在切割晶圆得到裸芯片后,将每个裸芯片放置于对应的芯片载体中,包括:

11、在切割晶圆得到裸芯片后,对未经过测试的裸芯片进行卷带包装,得到包装结构;

12、将包装结构的至少一个裸芯片取出,将每个裸芯片放置于对应的芯片载体中。

13、上述技术方案中,在切割晶圆得到裸芯片后,先对裸芯片进行卷带包装得到包装结构,再从包装结构中取出裸芯片进行测试。从包装结构中取出裸芯片进行测试,可以根据实际的生产需求和测试计划灵活安排。如果某些裸芯片暂时不需要测试,它们可以保持在包装结构中,等待后续处理。这种灵活性有助于优化生产流程和资源利用。

14、其中,包装结构包括编带。编带是指将芯片封装在一个带状载体上,以便在生产过程中进行自动化处理和装配。编带通常是一个由塑料或其他材料制成的长带,上面有一系列的芯片封装,每个封装之间以固定间距排列。每个封装都通过引脚或焊盘连接到带子上,以便与其他元件(如电路板)连接。编带不仅提高了生产效率和降低了生产成本,还提供了保护芯片安全的功能。芯片封装在编带中可以防止触摸、碰撞和损坏。

15、在一些可选的实施方式中,利用测试机对托盘上每个芯片载体中的裸芯片进行测试之后,还包括:

16、测试后,将芯片载体从托盘上取出,再将裸芯片从芯片载体中取出,将合格的裸芯片放回包装结构,或将合格的裸芯片放置到对应的托盘或frame膜上,并进行后续的批量出货流程。

17、上述技术方案中,通过将合格的裸芯片重新放回包装结构中,可以直接利用原有的包装进行批量出货。这样做不仅简化了出货流程,还避免了因重新包装而可能引入的额外成本和时间消耗。

18、在一些可选的实施方式中,利用测试机对托盘上每个芯片载体中的裸芯片进行测试,包括:

19、对每个芯片载体中的裸芯片进行以下至少一种测试:

20、逻辑芯片测试,动态向量老化应力测试,tsv测试,高速性能测试,phy i/o测试,2.5d sip测试,burn in测试。

21、上述技术方案中,裸芯片包括hbm芯片、3d堆叠芯片或先进制程封装芯片等,对hbm裸芯片的测试包括:逻辑芯片测试,动态向量老化应力测试,tsv测试,高速性能测试,phyi/o测试,2.5d sip测试,burn in测试。

22、其中,逻辑芯片测试:逻辑芯片作为hbm kgsd的核心组件之一,其性能直接影响整个系统的稳定性和可靠性,测试内容包括功能测试、时序测试、功耗测试等,以确保逻辑芯片在各种工作条件下都能正常工作。

23、动态向量老化应力测试:动态向量老化应力测试旨在模拟芯片在长时间使用过程中的老化情况,以评估其寿命和可靠性。具体的测试方法,包括:通过向芯片施加特定的动态向量,观察其在不同应力条件下的性能变化,从而预测其使用寿命。

24、tsv测试:tsv(硅通孔)是hbm实现芯片垂直堆叠的关键技术,其质量直接影响数据传输的速度和稳定性。测试内容包括tsv的电阻、电容、电感等电性能测试,以及tsv与微凸块之间的连接可靠性测试。

25、高速性能测试:hbm设计用于提供极高的数据传输速度,因此高速性能测试是评估其性能的重要指标。具体的测试方法包括:通过专用的高速测试设备,对hbm的带宽、延迟等关键性能指标进行测试。

26、phy i/o测试:phy i/o(物理层输入输出)是hbm与外部设备通信的接口,其性能直接影响数据传输的质量和效率。测试内容包括i/o接口的速率、时序、信号完整性等测试,以确保数据传输的准确性和稳定性。

27、2.5d sip测试:2.5d sip(系统级封装)技术将多个芯片和组件集成在一个封装内,形成紧凑的系统级解决方案。需要对封装内的所有芯片和组件进行全面的测试,包括功能测试、互连测试、热测试等,以确保整个系统的性能和可靠性。

28、burn in测试:burn in测试是一种加速老化测试方法,旨在通过模拟芯片在极端条件下的长时间运行,来快速暴露潜在的制造缺陷或早期失效模式。

29、上述测试不通过的ng芯片则进入修复过程,包括筛选与替换、参数调整、故障分析等。其中,筛选与替换:将测试中发现的不良芯片从生产批次中筛选出来,并用合格的芯片进行替换。参数调整:对于某些可以通过软件或固件调整来优化性能的缺陷,可能会采取调整参数的方式来改善芯片的表现。故障分析:对失效芯片进行详细分析,找出导致失效的根本原因,以便在后续的生产过程中进行改进。

30、在一些可选的实施方式中,芯片载体包括:载体主体和盖板;载体主体包括底板和包围结构,底板和包围结构形成具有开口的空腔;

31、将每个裸芯片放置于对应的芯片载体中,包括:

32、将裸芯片从开口处放入芯片载体的空腔,再利用盖板盖住开口,实现对裸芯片的固定。

33、上述技术方案中,裸芯片直接暴露在外界环境中容易受到物理损伤、污染和静电放电(esd)等问题的影响。通过将裸芯片放置于芯片载体的空腔内,并用盖板封闭开口,可以有效隔绝外部环境对裸芯片的直接影响,提高芯片的物理保护水平,减少损坏风险。并且,这种芯片载体的设计还有利于后续取出裸芯片的步骤。

34、在一些可选的实施方式中,底板上设置有连接器和探测焊盘,连接器设置于包围结构内侧,探测焊盘设置于包围结构外侧;连接器上设置有探针头,用于在裸芯片放置于芯片载体时,裸芯片的凸点和测试焊点接触对应的探针头;连接器还连接到探测焊盘,探测焊盘用于在测试时,测试机通过探测焊盘来测试裸芯片。

35、上述技术方案中,芯片,例如hbm芯片,微凸点的间距为73um,测试焊盘的间距约为165um,这些极小的间距对测试过程中的精度提出了极高的要求,由于间距极小,传统的测试插座(socket)在尝试与ubump或测试焊盘进行准确接触时面临巨大挑战。即使是微小的偏差或错位,都可能导致接触不良或失效。因此,本实施例通过在芯片载体中设置连接器,连接器的探针头与hbm芯片的微凸点或测试焊盘接触,连接器还连接到探测焊盘,探测焊盘的尺寸较大,测试机能够通过探测焊盘来测试hbm芯片。

36、在一些可选的实施方式中,连接器包括:mems pin或pogo pin。

37、其中,mems pin:由于mems技术的高度精确性,mems pin能够提供非常微小的接触点,确保与裸芯片凸点和测试焊点的精确对接。这种高精度的连接有助于减少测试误差,并提升信号传输的质量。

38、pogo pin:pogo pin以其独特的弹簧结构而闻名,这种结构允许针脚在受到压力时自动调整位置,以确保与接触点的最佳接触。这种自适应能力确保了即使在微小的位置偏差下也能实现稳定的连接。pogo pin的弹簧结构不仅提供了良好的接触性能,还赋予了它出色的耐用性。弹簧可以承受多次的插拔和压缩,而不易损坏,这对于需要频繁测试和更换裸芯片的应用场景尤为重要。

39、在一些可选的实施方式中,底板上还设置有对准标记;

40、将裸芯片从开口处放入芯片载体的空腔,包括:

41、利用机械臂,夹持裸芯片并悬停于芯片载体上方,利用对准标记进行定位对准后,将裸芯片垂直放入芯片载体。

42、上述技术方案中,对准标记为机械臂提供了明确的参考点,机械臂能够快速识别并定位到正确的位置,通过机械臂进行裸芯片的夹持、悬停、对准和放置,实现了整个过程的自动化,提高了生产效率,减少了人工操作带来的不确定性和错误。

43、在一些可选的实施方式中,芯片载体还包括:锁紧装置;

44、利用盖板盖住开口,实现对裸芯片的固定之后,还包括:

45、利用锁紧装置,将盖板与载体主体固定连接。

46、上述技术方案中,锁紧装置能够确保盖板与载体主体之间的紧密连接,减少因松动或间隙导致的外部环境对芯片载体的影响,如灰尘、湿气等污染物的侵入。并且,在测试过程中,芯片载体可能会受到各种外力的影响,锁紧装置能够有效防止盖板因振动、冲击等外力而意外脱落,确保裸芯片的稳定性和安全性。同时,锁紧装置的设计也易于拆卸,方便后续取出裸芯片的过程。

47、在一些可选的实施方式中,锁紧装置包括背扣或螺栓锁紧组件。

48、在一些可选的实施方式中,裸芯片包括hbm芯片、3d堆叠芯片或先进制程封装芯片等。

49、在一些可选的实施方式中,托盘上均匀分布有多个放置区域,每一放置区域用于摆放一个芯片载体;测试机对至少两个放置区域上的芯片载体进行并测。

50、在一些可选的实施方式中,裸芯片的凸点之间的间距范围为10~200um,裸芯片的测试焊点之间的间距范围为40~250um,芯片载体的探测焊盘之间的间距范围为200~500um。

51、在一些可选的实施方式中,探针头的按压行程为2~100um。

52、在一些可选的实施方式中,裸芯片的凸点的直径为10~100um;裸芯片的测试焊点为矩形,其长、宽均为30~100um;探测焊盘为矩形,其长、宽均为100~200um。

53、在一些可选的实施方式中,探测焊盘的表面镀金;探测焊盘采用cu、ni和pd中的一种或多种的合金制成。

54、在一些可选的实施方式中,盖板和芯片之间设置弹性材料层,弹性材料层可拆卸地固定在盖板表面。

55、在一些可选的实施方式中,弹性材料层的厚度为0.005-5mm;弹性材料层采用有机树脂、凝胶或柔性金属制成。

56、在一些可选的实施方式中,底板包括基板;探针头生长在基板上,探针头通过基板的内部线路连接到探测焊盘;基板包括硅基板、陶瓷基板或玻璃基板。

- 还没有人留言评论。精彩留言会获得点赞!