一种基于FPGA的精密时间数字转换器及其测量不确定度评定方法

本发明涉及精密时间数字转换器领域,具体是一种基于fpga的精密时间数字转换器及其测量不确定度评定方法。

背景技术:

1、随着集成电路设计、制造和工艺技术的不断发展,高精度、高分辨率的时间间隔测量系统利用专用集成电路(asic)或者现场可编程门阵列(fpga)得以实现,该系统的核心是时间数字转换器(tdc),其性能表现直接决定了它的应用场景,比如,高能物理实验、拉曼光谱、高性能质谱、空间科学仪器等应用系统往往需要亚皮秒甚至飞秒量级分辨率的tdc来提高整个系统的测量分辨率,这通常需要使用基于asic专门设计的高性能tdc,但是随着激光测距、激光扫描仪、正电子发射断层扫描等商业应用需求的增加,面向tdc技术的研究开始追求高通用性、经济性和快速研发与迭代能力,现有基于asic专门设计的高性能tdc其通用性、经济性和迭代能力均无法满足要求。因此,若能够基于fpga实现亚皮秒甚至飞秒量级分辨率的tdc,无疑能够满足高通用性、经济性和快速研发与迭代的要求。

2、目前,大量的研究投入到了基于fpga的tdc设计和实现,设计者最关注的是如何充分利用现有硬件资源提高时间间隔测量的分辨率和精度,其次是如何改善非线性以提升可靠性等指标。虽然大部分研究都给出了基于重复性测量结果的分辨率和精度指标的简单分析与对比,但后来者无法据此进行有效的误差源识别和测量不确定度评定以指导其电路设计和实现。

3、为了确定影响tdc测量分辨率和精度的各种设计因素,大部分研究通过多次测量计算出tdc能够识别的最短时间间隔测量即分辨率,但往往忽略了对其不确定性的评定,而对测量精度这一关键计量参数的评定则是使用误差源的方差的和的平方根来表示,如公式(1):

4、

5、一个典型的单级架构tdc主要有时间间隔数字量化误差(σq)、输入信号引入的误差(σinput)、信号传播过程中产生的误差(σprop)、参考时钟误差(σclk)等最明显的误差源,多次测量获得他们的方差值后求和再取平方根,这是一种评定精度不确定性的快捷方法,但是大部分研究并没有建立典型的精密时间测量系统的不确定性评定体系。

6、现有的不确定度评定方法按照gum法将不确定度分为a类和b类,其中a类不确定度利用统计的方法对大量的测量数据进行评定,b类不确定度根据经验或其他信息所认定的概率分布来评定,最后利用方差合成定理对各个不确定度分量进行合成并按照包含概率确定包含因子从而得到扩展不确定度,但gum法只能适用于重复测量的线性模型中,因此这些方法均无法对目前已经得到最广泛研究和应用的基于抽头延迟链(tdl)插值架构的tdc进行详细的误差源分析和测量不确定度评定。

技术实现思路

1、本发明提供了一种基于fpga的精密时间数字转换器,以解决现有技术基于asic专门设计的高性能tdc其通用性、经济性和迭代能力均无法满足要求的问题。

2、为了达到上述目的,本发明所采用的技术方案为:

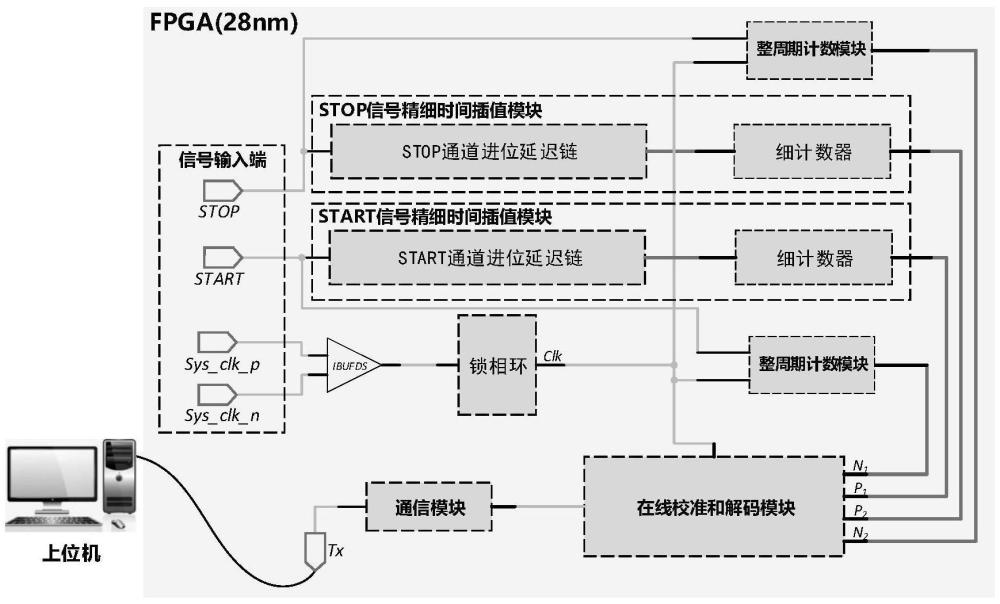

3、一种基于fpga的精密时间数字转换器,包括上位机,以及由fpga实现的双通道精细时间插值模块、解码模块、通信模块、整周期时间计数模块,其中:

4、所述双通道精细时间插值模块包括两条并行的延迟链,以及每条延迟链对应的细计数器;每条延迟链分别由fpga上的多个carry4进位单元依次级联构成,每个carry4进位单元分别引出四个抽头形成四个延迟单元,由每条延迟链通过各自包含的所有延迟单元,对该延迟链上输入的信号进行精细时间插值;每个细计数器分别包括由fpga中的系统时钟驱动实现的触发器阵列,由每个细计数器的触发器阵列采样对应延迟链上所有延迟单元的输出;

5、所述整周期时间计数模块由fpga中的系统时钟驱动实现,由整周期时间计数模块对每条延迟链上输入的信号进行整周期计数;

6、所述解码模块由fpga上的逻辑单元实现,由解码模块统计所述双通道精细时间插值模块中每个细计数器的触发器阵列采样结果的数量,即为每个细计数器对应的延迟链中信号传播的延迟单元的个数,并由解码模块将每条延迟链中信号传播的延迟单元的个数乘以每个延迟单元的延迟时间,即得到每条延迟链上信号的总延迟时间;

7、所述通信单元由fpga上的逻辑单元实现,由通信单元将所述解码模块得到的每条延迟链上信号的精细插值时间,以及整周期时间计数模块得到的每条延迟链上输入的信号的整周期计数,分别传输至上位机;

8、所述上位机根据fpga上通信单元传输的数据进行分析和处理,得到所述双通道精细时间插值模块中两条延迟链上输入的信号的精细时间间隔。

9、进一步的,所述上位机得到所述时间间隔后,进行测量结果不确定度来源分析和评定。

10、进一步的,还包括在线校准模块,所述在线校准模块由fpga的逻辑单元实现,在线校准模块获取上位机得到的测量结果不确定度来源分析和评定结果,并由在线校准模块基于分析和评定结果对解码模块得到的精细时间进行在线校准和补偿。

11、进一步的,所述双通道精细时间插值模块中,同一延迟链上的多个carry4进位单元设于fpga的同一bank中,不同延迟链上的carry4进位单元设于fpga的不同bank。

12、一种上述基于fpga的精密时间数字转换器的测量不确定度评定方法,使用自适应蒙特卡洛方法amcm,包括以下步骤:

13、步骤1、根据所述整周期计数模块测得的一条延迟链上信号的整周期计数值n1,以及另一条延迟链上信号的整周期计数值n2,计算出两条延迟链上信号被测时间间隔的粗时间tcoarse,如下公式所示:

14、tcoarse=(n2-n1)·tclk,

15、其中,tclk为fpga的系统时钟周期值;

16、根据双通道精细时间插值模块中两个延迟链上输入的信号分别与参考时钟上升沿之间的相位差值p1、p2,结合每条延迟链上信号的总延迟时间即精细插值时间,计算出两条延迟链上信号被测时间间隔的精细时间tfine,如下公式所示:

17、tfine=p2·tdelay2-p1·tdelay1,

18、其中,tdelay1和tdelay2分别为两个延迟链上信号的总延迟时间;

19、将粗时间tcoarse,和精细时间tfine,做加法计算,即得出任意i时刻两条延迟链上输入的信号的时间间隔tmi;

20、步骤2、分析测量不确定度来源:

21、基于所述基于fpga的精密时间数字转换器产生的系统误差和随机误差,对所述基于fpga的精密时间数字转换器进行测量不确定性来源分析,由此得到系统误差和随机误差这两种不确定性的来源,其中:

22、系统误差引入的不确定性由信号从进入测量系统中的精密时间数字转换器到测量系统输出测量结果的整个过程中所经历的传播路径的固有差异引起的;

23、随机误差引入的不确定性是与延迟单元的延迟时间抖动相关的不确定性;

24、步骤3、建立分辨率数学模型:

25、根据步骤2确定的系统、随机两种误差类型,将测量不确定度分为a类测量不确定度和b类测量不确定度,基于a类和b类这两类不确定度来源,建立用于评定所述基于fpga的精密时间数字转换器的分辨率性能指标的数学模型;

26、步骤4、进行测量不确定度评定:

27、以步骤1得到的任意i时刻两条延迟链上输入的信号的时间间隔tmi代入步骤3所建立的分辨率数学模型,并采用自适应蒙特卡洛法执行分布传播,分别抽样得到各个输入量xi的离散值xi1,xi2,...,xim,各个输入量xi的离散值通过步骤3建立的数学模型得到输出量的模型值yi,通过得到m个g的估计值计算所述基于fpga的精密时间数字转换器的分辨率性能指标的估计值以及标准不确定度。

28、进一步的,还包括步骤5:使用gum法对所述基于fpga的精密时间数字转换器进行测量不确定度评定,并将步骤4的评定结果与使用gum法得到的不确定度评定结果进行比对和分析,由此得到基于自适应蒙特卡洛法的测量不确定度评定结果的置信度。

29、本发明中,在28nm制程的fpga芯片上基于专用carry4进位资源,设计实现了分辨率和精度优于50ps的时间数字转换器,能够稳定实现优于50ps测量分辨率和精度的tdl插值架构的时间数字转换器具有应用通用性高、经济性好和优化迭代能力强的优点。

30、本发明中还公开了建立的时间数字转换器的测量不确定度评定方法,基于在28nm工艺的fpga芯片上设计和实现的上述最典型tdl架构的时间数字转换器,并通过对被测信号的双通道测量得到时间数字转换器的性能指标数据,然后对影响测量分辨率等指标的不确定度来源进行分析以得到其分布并建立数学模型,将从fpga中获得的测量数据带入所建立的数学模型并采用自适应蒙特卡洛法执行分布传播以完成对所述时间数字转换器的各性能指标的测量不确定度评定。

31、本发明基于从基于fpga实现的精密时间数字转换器获得的测量数据,结合所建立的数学模型,利用基于统计学的自适应蒙特卡洛法(amcm)对tdc的测量不确定度进行不确定度评定。其中,amcm是mcm的一种改良算法,蒙特卡洛试验次数不断增加,直至所需要的不同结果达到统计意义上的稳定。相比于gum法,本发明采用amcm方法能考虑到模型中非线性的影响,并且输入量的分布更能合理地被表征,而不局限于正态分布。amcm为输入量的概率密度函数(pdf)提供了另一种表示方法,由于一般不能确定输出量的pdf的解析表达式,所以本发明中采用amcm方法可以在规定的数值容差下估计出pdf的主要特征量:(1)输出量的估计值;(2)输出量估计值的标准不确定度;(3)约定包含概率的输出量包含区间。

32、综上,本发明中,首次提出将基于amcm应用于提出的tdc架构进行性能指标的不确定度评定,通过在具有代表性的fpga硬件上设计、实现tdl-tdc架构并进行可靠的分析与建模,利用amcm方法完成测量不确定度评定,为如何在更先进的集成电路上设计、实现更复杂的基于tdc的精密时间测量系统提供了有价值的参考。

- 还没有人留言评论。精彩留言会获得点赞!