用于驱动背对背功率开关的功率开关控制器和电子电路的制作方法

1.本公开涉及用于驱动背对背功率开关的功率开关控制器和电子电路。

背景技术:

2.传统的继电器允许模拟或数字信号流在继电器接通时在任意方向上通过继电器路径,并且在继电器关断时阻断这种信号。继电器通常采用基于电磁铁驱动的机械部件来实现。

3.双向开关,也被称为模拟开关或双边开关,以类似的方式作为传统的继电器操作,但是不需要机械部件。通常,模拟开关采用背对背电源金属氧化物半导体场效应晶体管(mosfet)来实现。例如,图 1示出了传统背对背功率开关102和功率开关控制器104的示意图。

4.在正常操作期间,当电压(例如,5v)被施加到电源端子v

cc

时,电流源106和114生成各自的电流i

h

和i

l

,使得电流i

r

流经电阻器108。电流i

r

使得电压v

gs

增加超过功率mosfet 110和112的阈值电压v

th

,从而接通功率mosfet 110和112。当功率mosfet110和112接通时,模拟或数字信号可以从端子va流向端子vb并从端子vb流向端子va。

5.当移除电源端子v

cc

处的电压时(例如,电源端子v

cc

处0v),电压v

gs

下降低于阈值v

th

,从而使得功率mosfet 110和112关断。当功率mosfet 110和112关断时,由于功率mosfet 110和112的本征二极管(未示出)在背对背功率开关102中彼此相对,信号不能从端子va流向端子vb或从端子vb流向va。

技术实现要素:

6.本公开至少解决上述现有背对背功率开关的部分缺点。

7.根据本公开的第一方面,提供了一种用于驱动背对背功率开关的功率开关控制器,背对背功率开关具有栅极端子、源极端子、第一端子和第二端子,功率开关控制器包括:放大器,具有:被配置为接收电源电压的电源端子、被配置为被耦合到背对背功率开关的栅极端子的输出、被配置为被耦合到背对背功率开关的源极端子的第一输入、以及耦合到放大器的输出的第二输入,其中放大器被配置为在放大器的输出处生成输出电压,输出电压是比放大器的第一输入处的电压高的偏移电压。

8.在一些实施例中,放大器包括:第二电源端子,被配置为接收低于电源电压的第二电源电压;第一晶体管,具有耦合到第二电源端子的电流路径;电流镜,耦合到电源端子;第二晶体管,具有耦合到放大器的第一输入的栅极、和耦合在第一晶体管的电流路径和电流镜之间的电流路径;和第三晶体管,具有耦合到放大器的第二输入的栅极、和耦合在第一晶体管的电流路径和电流镜之间的电流路径。

9.在一些实施例中,功率开关控制器进一步包括第四晶体管,第四晶体管具有耦合到电源端子的电流路径,第四晶体管的电流路径被配置为被耦合到背对背功率开关的栅极端子。

10.在一些实施例中,功率开关控制器进一步包括:电流发生器,被配置为生成参考电流;和偏移发生器,被配置为基于参考电流生成偏移电压。

11.在一些实施例中,偏移发生器被耦合在第一晶体管的电流路径和第三晶体管的电流路径之间。

12.在一些实施例中,偏移发生器和电流发生器是匹配电路。

13.在一些实施例中,电流发生器包括第一晶体管和与第一晶体管串联耦合的第一电阻器。

14.在一些实施例中,电流发生器包括第四晶体管和与第四晶体管串联耦合的第一电阻器,其中偏移发生器包括第五晶体管和与第五晶体管串联耦合的第二电阻器,并且其中第一电阻器具有等于第二电阻器的第二电阻的第一电阻。

15.在一些实施例中,功率开关控制器,进一步包括:第二电流镜,耦合到电流发生器;和第三电流镜,耦合到第二电流镜,第三电流镜包括第一晶体管。

16.在一些实施例中,功率开关控制器进一步包括第三电源端子,第三电源端子被配置为接收高于第二电源电压并且低于电源电压的第三电源电压,其中第二电流镜被耦合到第三电源端子。

17.在一些实施例中,第二电流镜包括2比1的电流比。

18.在一些实施例中,第一晶体管、第二晶体管和第三晶体管是n型晶体管。

19.在一些实施例中,功率开关控制器被配置为接收参考电压,并且其中放大器被配置为基于参考电压生成偏移电压。

20.在一些实施例中,电源电压高于参考电压。

21.在一些实施例中,放大器被配置为:当参考电压在第一电压处时接通背对背功率开关;和当参考电压在第二电压处时关断背对背功率开关。

22.在一些实施例中,第一电压高于第二电压。

23.在一些实施例中,参考电压是带隙电压。

24.根据本公开的第二方面,提供了一种电子电路,包括:第一端子,被配置为被耦合到背对背功率开关的栅极端子;第二端子,被配置为被耦合到背对背功率开关的源极端子;第一电源端子,被配置为接收第一电源电压;第二电源端子,被配置为接收低于第一电源电压的第二电源电压;第一晶体管,具有耦合到第二电源端子的电流路径;电流镜,耦合到第一电源端子;第二晶体管,具有耦合到第二端子的栅极、和耦合在第一晶体管的电流路径和电流镜之间的电流路径;第三晶体管,具有耦合到第二端子的栅极、和耦合在第一晶体管的电流路径和电流镜之间的电流路径;电流发生器,被配置为生成参考电流;和偏移发生器,被配置为基于参考电流生成偏移电压,偏移发生器耦合在第三晶体管的电流路径和第一晶体管的电流路径之间。

25.在一些实施例中,电子电路进一步包括背对背功率开关,背对背功率开关的栅极端子耦合到第一端子,源极端子耦合到第二端子,背对背功率开关还包括第三端子和第四端子。

26.在一些实施例中,背对背功率开关包括:n型的第一扩散型金属氧化物半导体晶体管;和n型的第二扩散型金属氧化物半导体晶体管,第一扩散型金属氧化物半导体晶体管和第二扩散型金属氧化物半导体晶体管具有耦合到栅极端子的相应的栅极、以及耦合到源极

端子的相应的源极,其中第一扩散型金属氧化物半导体晶体管的漏极被耦合到第三端子并且第二扩散型金属氧化物半导体晶体管的漏极被耦合到第四端子。

27.在本实用新型的实施例中,功率开关控制器能够保持背对背功率开关处于接通状态,由背对背功率开关从功率开关控制器的电源端子提供或吸收的电流基本为零。功率开关控制器还能够在功率开关上保持稳定接通电位,使得功率开关的导通电阻产生微小偏差。

附图说明

28.为了更全面地理解本实用新型及其优点,现在结合附图参考以下描述,其中:

29.图1示出了传统背对背功率开关和功率开关控制器的示意图;

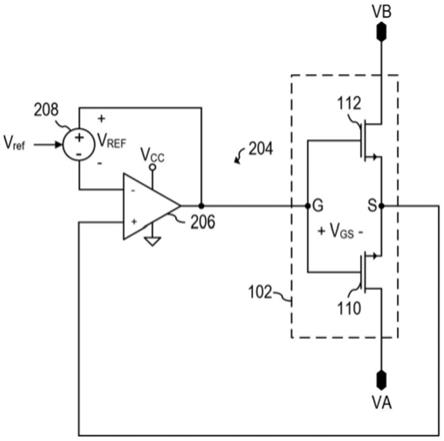

30.图2示出了根据本实用新型的实施例的背对背功率开关和功率开关控制器的示意图;

31.图3a示出了根据本实用新型的实施例的功率开关控制器的示意图;

32.图3b示出了根据本实用新型的实施例的由图3a的功率开关控制器在不同温度和工艺变化下施加到功率开关的v

gs

的仿真波形;

33.图4示出了根据本实用新型的实施例的功率开关控制器的示意图;和

34.图5示出了根据本实用新型的实施例的功率开关控制器的示意图。

35.除非明确指出,否则不同图中对应的数字和符号通常表示对应的部分。这些图是为了清楚地说明优选实施例的相关方面而绘制的,并不一定按比例绘制。

具体实施方式

36.根据一个实施例,一种用于驱动背对背功率开关的功率开关控制器包括:放大器,具有:被配置为接收电源电压的电源端子的放大器、被配置为耦合到背对背功率开关的栅极端子的输出、被配置为耦合到背对背功率开关的源极端子的第一输入和耦合到放大器的输出处的第二输入。该放大器被配置为在放大器的输出处生成输出电压,该输出电压是比放大器的第一输入处的电压高的偏移电压。

37.根据一个实施例,一种电路包括:被配置为耦合到背对背功率开关的栅极端子的第一端子;被配置为耦合到背对背功率开关的源极端子的第二端子;被配置为接收第一电源电压的第一电源端子;被配置为接收低于第一电源电压的第二电源电压的第二电源端子;具有耦合到第二电源端子的电流路径的第一晶体管;耦合到第一电源端子的电流镜;具有耦合到第二端子的栅极和耦合在第一晶体管的电流路径和电流镜之间的电流路径的第二晶体管;具有耦合到第二端子的栅极和耦合在第一晶体管的电流路径和电流镜之间的电流路径的第三晶体管;被配置为生成参考电流的电流发生器;和被配置为基于参考电流生成偏移电压的偏移发生器。该偏移发生器耦合在第三晶体管的电流路径和第一晶体管的电流路径之间。

38.根据一个实施例,一种用于驱动背对背功率开关的方法包括:接收参考电压;接收高于参考电压的电源电压;基于参考电压生成参考电流;基于参考电流生成偏移电压;以及利用放大器将偏移电压施加在背对背功率开关的栅极端子和背对背功率开关的源极端子之间,该放大器包括耦合到栅极端子的输出和耦合到源极端子的第一输入。

39.下文详细讨论所公开的实施例的制造和使用。然而,应当理解,本实用新型提供许多可应用的实用新型概念,可以在各种具体的上下文中体现。所讨论的具体实施例仅仅说明了制造和使用本实用新型的具体方法,而不限制本实用新型的范围。

40.本说明书在下文说明了各种具体细节以便根据本说明书深入了解一些示例实施例。可以在没有一个或多个具体细节的情况下获得实施例,或者通过其他方法、部件、材料等获得实施例。在其他情况下,没有详细示出或描述已知的结构、材料或操作,以免混淆实施例的不同方面。本说明书中对“实施例”的引用是指与实施例有关的具体的配置、结构或特征包括在至少一个实施例中。因此,可能出现在本说明书的不同位置的诸如“在一个实施例中”的短语不一定明确指同一个实施例。此外,在一个或多个实施例中可以以任意合适的方式组合具体的构造、结构或特征。

41.本实用新型的实施例将在具体的上下文中描述,例如用于iddq 测试应用的零电流接通背对背功率开关控制器。本实用新型的实施例可以用于其他应用,诸如可以受益于背对背功率开关的零电流接通的其他应用等。

42.在本实用新型的实施例中,功率开关控制器能够保持背对背功率开关处于接通状态,由背对背功率开关从功率开关控制器的电源端子提供或吸收的电流基本为零。功率开关控制器还能够在功率开关上保持稳定接通电位,使得功率开关的导通电阻产生微小偏差。在一些实施例中,由功率开关控制消耗的电流可以被调节到非常小的值。

43.如图1所示,功率开关控制器104包括电流源106和114,以及电阻器108。当电流源106和114产生的电流ih和il分别失配时(例如,当电流ih高于电流il时,或者当电流il高于电流ih时),在背对背功率开关102接通时,背对背功率开关102提供或吸收额外电流。

44.一些应用依赖于吸收/提供的基本为零的电流,来接通背对背功率开关,以正常操作。这种应用的一个示例是iddq测试。在iddq测试期间,通过测量ic的电流消耗(例如流经电源端子v

cc

的电流),检测集成电路(ic)是否存在制造缺陷。在iddq测试中一些制造缺陷表现为较高的电流。在iddq测试期间,如果流经电源端子v

cc

的电流高于预定的阈值(例如,可能有几μa或几ma,这取决于应用), ic可能会检测失败。因此,具有零电流接通的背对背功率开关,有利地允许例如在iddq测试期间使用功率开关,而基本不会影响iddq 测试期间的电流测量,从而增加iddq测试在检测制造缺陷方面的有效性。

45.在本实用新型的实施例中,背对背功率开关从功率开关控制器吸收或提供的零电流是通过使用一级放大器缓冲器实现的,该一级放大器缓冲器用于驱动背对背功率开关的晶体管的栅极。该一级放大器缓冲器的正向输入耦合到背对背功率开关的晶体管的源极。偏移电压被引入到一级放大器缓冲器的反向输入和一级放大器缓冲器的输出之间。

46.图2示出了根据本实用新型的实施例的背对背功率开关102和功率开关控制器204的示意图,功率开关控制器204包括放大器206和偏移发生器208。

47.在正常操作期间,偏移发生器生成偏移电压v

ref

,并且放大器 206作为偏移的缓冲器,其中该偏移等于偏移电压v

ref

。因此,放大器206在节点g处施加高于节点s处电压的电压v

ref

,从而保持恒定电压v

gs

等于v

ref

,而不考虑端子va和vb之间流动的信号的电压。

48.如图2所示,放大器206的输出驱动高阻抗节点,因为放大器206 的输出驱动功率mosfet 110和112的栅极。如图2所示,功率 mosfet 110和112的源极耦合到放大器206的正向输入,该输入为高阻抗输入。因此,功率开关控制器204有利地能够保持功率开关102 接

通,而不使功率开关102从功率开关控制器204处吸收或提供电流。

49.在正常操作期间,放大器206接收电源电压v

cc

。放大器206通过接通偏移发生器208来接通功率开关102,并通过关断偏移发生器 208来关断功率开关102。当偏移发生器208接通时,偏移发生器208 生成足够高的电压vref以在饱和模式下接通晶体管110和112,从而使功率mosfet 110和112的导通电阻最小。

50.在一些实施例中,电源电压v

cc

至少是高于端子va和vb的最大电压的电压v

ref

。例如,如果功率开关102被配置为在端子va和 vb处接收0v至3v的电压,并且如果功率晶体管110和112被配置为在其各自电压v

gs

为3.3v时处于饱和模式下,那么电压v

ref

为 3.3v,并且电源电压v

cc

至少为6.3v。应当理解,由于应用和晶体管技术的不同(例如,1.8v晶体管、3.3v晶体管、5v晶体管等), v

cc

、v

ref

的电压以及端子va和vb的最大电压可能不同。本领域的技术人员将会了解如何修改该电压以适应具体的技术和应用。

51.在一些实施例中,当电源电压vcc被移除时(例如,0v),功率开关102关断。

52.背对背功率开关102可以用n型晶体管功率mosfet 112和110 实现。在一些实施例中,功率mosfet 110和112用扩散型mos (dmos)晶体管实现,诸如垂直dmos(vdmos)或横向dmos (ldmos)。还可以使用其他晶体管类型的功率晶体管,诸如p型功率晶体管。

53.如图2所示,偏移发生器208可以接收从外部电路(未示出)参考电压v

ref

,其中电压v

ref

和v

ref

相等。在一些实施例中,这种外部电路是带隙电路,其产生的电压在温度范围内基本稳定。在其他实施例中,参考电压v

ref

是从带隙电路导出的,诸如通过使用诸如ldo 的稳压器,该稳压器使用带隙生成的电压作为参考电压。

54.在一些实施例中,偏移电压v

ref

不同与参考电压v

ref

。例如,在一些实施例中,偏移电压v

ref

是参考电压v

ref

的缩减版。

55.在一些实施例中,偏移发生器208可以通过选通参考电压v

ref

来关断。在一些实施例中,外部信号可以用于关断偏移发生器208。在一些实施例中,如果参考电压v

ref

由ldo提供,那么可以关断ldo 来关断偏移发生器208。其他实现也是可能的。

56.图3a示出了根据本实用新型的实施例的功率开关控制器304的示意图。功率开关控制器304包括一级放大器缓冲器306。一级放大器缓冲器306包括晶体管314、320、322、324和326。晶体管320 的栅极可以理解为一级放大器306的正向输入,晶体管322的栅极可以理解为一级放大器306的反向输入,并且晶体管322的漏极可以理解为一级放大器306的输出。在图3a、图4和图5的实施例中,偏移电压v

ref

等于参考电压v

ref

。

57.功率开关控制器304还包括电流发生器307和偏移发生器315。电流发生器307和偏移发生器315是匹配电路。换言之,电阻器316 和310是匹配的并且晶体管308和318是匹配的(例如工艺变化和温度变化以类似的方式影响电阻316和310并以类似的方式影响晶体管 318和308)。匹配电路可以通过布局放置或本领域已知的任意其他方式实现。

58.在正常操作期间,当电源端子v

cc

有电时(例如,6v),并且当参考电压v

ref

较低时(例如,0v),功率开关102关断(即,断开)。当v

ref

从低(例如,0v)到高(例如,3.3v)转换时,晶体管328 完全接通(即,处于饱和模式),从而将节点g拉高到v

cc

并接通功率开关102。当功率开关102接通时(即,闭合),节点s的电压基本类似于端子va和vb的电压(因为在接通时功率mosfet 110和 112的导通电阻非常小,诸如几mω)。在启动后,节点g到达电压 v

ref

或更高,使得晶体管328关断。

59.当电压v

ref

较高时(例如,3.3v),晶体管308完全接通,使得参考电流i

ref1

流经晶体管308。电流i

ref1

通过电流镜329镜像到电流 i

ref2

。如图所示,电流镜329的比率为2比1,使得电流i

ref2

是电流 i

ref1

的两倍。电流i

ref2

通过电流镜311镜像到电流i

ref3

。如图所示,电流镜311的比率是1比1,使得电流i

ref3

等于i

ref2

。

60.由于电流i

ref3

是电流i

ref1

的两倍,如果晶体管318和308具有相同的大小(例如,相似的宽和长)并且电阻器310和316具有相同的电阻,那么一级放大器306保持节点g的电压v

ref

高于节点s,从而在正常操作期间保持v

gs

恒定。

61.在电流发生器307和偏移发生器315为匹配电路的实施例中,功率开关控制器304在操作温度和工艺变化下有利地保持基本恒定的 v

gs

。例如,图3b示出了根据本实用新型的实施例的由功率开关控制器304在不同温度和工艺变化下施加到功率开关102的v

gs

的仿真波形350。曲线352示出了第一工艺拐角处-40℃下的v

gs

。曲线354示出了第一工艺拐角处25℃下的v

gs

。曲线356示出了第一工艺拐角处 150℃下的v

gs

。曲线358示出了第二工艺拐角处-40℃下的v

gs

。曲线360示出了第二工艺拐角处25℃下的v

gs

。曲线362示出了第二工艺拐角处150℃下的v

gs

。曲线364示出了第三工艺拐角处-40℃下的v

gs

。曲线366示出了第三工艺拐角处25℃下的v

gs

。曲线368示出了第三工艺拐角处150℃下的v

gs

。

62.如曲线352所示,-40℃下v

gs

在第一工艺拐角(typ拐角)处为2.94v。如曲线354所示,25℃下v

gs

在第一工艺拐角处为2.97v。如曲线356所示,150℃下v

gs

在第一工艺拐角处为3.02v。如曲线 358所示,-40℃下v

gs

在第二工艺拐角(max拐角)处为3.01v。如曲线360所示,25℃下v

gs

在第二工艺拐角处为3.05v。如曲线 362所示,150℃下v

gs

在第二工艺拐角处为3.14v。如曲线364所示,-40℃下v

gs

在第三工艺拐角(min拐角)处为2.91v。如曲线 366所示,25℃下v

gs

在第三工艺拐角处为2.93v。如曲线368所示, 150℃下v

gs

在第三工艺拐角处为2.97v。

63.图4示出了根据本实用新型的实施例的功率开关控制器404的示意图。功率开关控制器404以与功率开关控制器304类似的方式操作。然而,功率开关控制器404具有独立的电源端子v

dd

为电流镜329供电。

64.在一些实施例中,独立的电源端子v

dd

接收低于电源端子v

cc

的电压。例如,在一些实施例中,电源端子可以接收6.3v或更高的电压,而独立的电源端子v

dd

接收3v的电压。使用独立的端子v

dd

可以通过允许使用较小的晶体管(例如,晶体管330和332),在不影响性能的情况下,通过向独立的电源端子v

dd

提供较低的电压,有利地允许降低功耗和硅表面积。

65.图5示出了根据本实用新型的实施例的功率开关控制器504的示意图。功率开关控制器504以与功率开关控制器304类似的方式操作。然而,功率开关控制器504通过使用电流发生器507生成电流i

ref4

。电流发生器507和偏移发生器515是匹配电路。

66.偏移发生器515通过电阻两倍于电阻器510的电阻器516和大小两倍(例如,两倍宽度和相同长度)于晶体管508的晶体管518生成 v

ref

的偏移。

67.应当理解,所公开的实施例的修改是可能的。例如,关于图2,偏移发生器208可以耦合到放大器206的正向输入而不是放大器206 的反向输入。在一些实施例中,偏移发生器208可以作为两个或更多耦合到放大器206的反向和/或正向输入的偏移发生器来实现。另外的非限制性示例,关于图3a,电流镜329、311和323可以具有不同的缩放比率,可以通过修改电压v

ref

、电阻器310和316和/或功率开关控制器304的一个或多个晶体管的晶体管大小

进行补偿。其他的修改也是可能的。

68.这里总结了本实用新型的示例实施例。其他实施例也可以从本文提出的说明书和权利要求的整体中理解。

69.示例1.一种用于驱动背对背功率开关的功率开关控制器,所述背对背功率开关包括栅极端子、源极端子、第一端子和第二端子,所述功率开关控制器包括:放大器:具有被配置为接收电源电压的电源端子、被配置为耦合到所述背对背功率开关的所述栅极端子的输出、被配置为耦合到所述背对背功率开关的所述源极端子的第一输入和耦合到所述放大器的所述输出处的第二输入。所述放大器被配置为在所述放大器的所述输出处生成输出电压,所述输出电压是比所述放大器的所述第一输入处的电压高的偏移电压。

70.示例2.示例1所述的功率开关控制器,其中所述放大器包括:被配置为接收低于所述电源电压的第二电源电压的第二电源端子;具有耦合到所述第二电源端子的电流路径的第一晶体管;耦合到所述电源端子的电流镜;第二晶体管,具有耦合到所述放大器的所述第一输入的栅极和耦合在所述第一晶体管的所述电流路径和所述电流镜之间耦合的电流路径;以及第三晶体管,具有耦合到所述放大器的所述第二输入的栅极和耦合在所述第一晶体管的所述电流路径和所述电流镜之间的电流路径。

71.示例3.示例1或2中的一个示例所述的功率开关控制器,进一步包括具有耦合到所述电源端子的电流路径的第四晶体管,所述第四晶体管的所述电流路径被配置为耦合到所述背对背功率开关的所述栅极端子。

72.示例4.示例1至3中的一个示例所述的功率开关控制器,进一步包括:被配置为输出参考电流的电流发生器;和被配置为基于所述参考电流生成所述偏移电压的偏移发生器。

73.示例5.示例1至4中的一个示例所述的功率开关控制器,其中所述偏移发生器耦合在所述第一晶体管的所述电流路径和所述第三晶体管的所述电流路径之间。

74.示例6.示例1至5中的一个示例所述的功率开关控制器,其中所述偏移发生器和所述电流发生器是匹配电路。

75.示例7.示例1至6中的一个示例所述的功率开关控制器,其中所述电流发生器包括所述第一晶体管和与所述第一晶体管串联耦合的第一电阻器。

76.示例8.示例1至7中的一个示例所述的功率开关控制器,其中所述电流发生器包括第四晶体管和与所述第四晶体管串联耦合的第一电阻器,其中所述偏移发生器包括第五晶体管和与所述第五晶体管串联耦合的第二电阻器,并且其中所述第一电阻器的电阻等于所述第二电阻器的电阻。

77.示例9.示例1至8中的一个示例所述的功率开关控制器,进一步包括:耦合到所述电流发生器的第二电流镜;和耦合到所述第二电流镜的第三电流镜,所述第三电流镜包括所述第一晶体管。

78.示例10.示例1至9中的一个示例所述的功率开关控制器,进一步包括被配置为接收高于所述第二电源电压并且低于所述电源电压的第三电源电压,其中所述第二电流镜耦合到所述第三电源端子。

79.示例11.示例1至10中的一个示例所述的功率开关控制器,其中所述第二电流镜包括2比1的电流比。

80.示例12.示例1至11中的一个示例所述的功率开关控制器,其中所述第一晶体管、所述第二晶体管和所述第三晶体管是n型晶体管。

81.示例13.示例1至12中的一个示例所述的功率开关控制器,其中所述功率开关控制器被配置为接收参考电压,并且其中所述放大器被配置为基于所述参考电压生成所述偏移电压。

82.示例14.示例1至13中的一个示例所述的功率开关控制器,其中所述电源电压高于所述参考电压。

83.示例15.示例1至14中的一个示例所述的功率开关控制器,其中所述放大器被配置为:当所述参考电压处于第一电压时接通所述背对背功率开关;并且当所述参考电压处于第二电压时关断所述背对背功率开关。

84.示例16.示例1至15中的一个示例所述的功率开关控制器,其中所述第一电压高于所述第二电压。

85.示例17.示例1至16中的一个示例所述的功率开关控制器,其中所述参考电压是带隙电压。

86.示例18.一种电路包括:被配置为耦合到背对背功率开关的栅极端子的第一端子;被配置为耦合到所述背对背功率开关的源极端子的第二端子;被配置为接收第一电源电压的第一电源端子;被配置为接收低于所述第一电源电压的第二电源电压的第二电源端子;具有耦合到所述第二电源端子的电流路径的第一晶体管;耦合到所述第一电源端子的电流镜;第二晶体管,具有耦合到所述第二端子的栅极和耦合在所述第一晶体管的所述电流路径和所述电流镜之间耦合的电流路径;第三晶体管,具有耦合到所述第二端子的栅极和耦合在所述第一晶体管的所述电流路径和所述电流镜之间耦合的电流路径;被配置为生成参考电流的电流发生器;和被配置为基于参考电流生成偏移电压的偏移发生器,所述偏移发生器耦合在所述第三晶体管的所述电流路径和所述第一晶体管的所述电流路径之间。

87.示例19.示例18所述的电路,进一步包括所述背对背功率开关、耦合到所述第一端子的所述背对背开关的所述栅极端子、耦合到所述第二端子的所述源极端子,所述背对背开关还包括第三端子和第四端子。

88.示例20.示例18或19所述的电路,其中所述背对背功率开关包括:n型的第一扩散型金属氧化物半导体(dmos)晶体管;和所述 n型的第二dmos晶体管,所述第一和第二dmos晶体管各自的栅极耦合到所述栅极端子,并且各自的源极耦合到所述源极端子,其中所述第一dmos晶体管的漏极耦合到所述第三端子并且所述第二 dmos晶体管的漏极耦合到所述第四端子。

89.示例21.一种驱动背对背功率开关的方法,所述方法包括:接收参考电压;接收高于所述参考电压的电源电压;基于所述参考电压生成参考电流;基于所述参考电流生成偏移电压;以及利用放大器将所述偏移电压施加在所述背对背功率开关的栅极端子和背对背功率开关的源极端子之间,所述放大器包括耦合到所述栅极端子的输出和耦合到所述源极端子的第一输入。

90.示例22.示例21所述的方法,进一步包括:通过将所述偏移电压增加到第一电压来接通所述背对背功率开关;和通过将所述偏移电压降低到第二电压来关断所述背对背功率开关。

91.示例23.示例21或22所述的方法,其中所述第一电压高于所述第二电压,并且其中所述第二电压为0v。

92.示例24.示例21至23所述的方法,进一步包括:在电源端子处接收所述电源电压;将所述参考电压从第一电压增加到第二电压;当所述参考电压在所述第二电压处时利用所述参考电压接通第一晶体管,所述第一晶体管具有耦合在所述电源端子和所述栅极端子之间的电流路径;以及基于所述参考电压的所述增加来增加所述偏移电压;以及当所述偏移电压到达所述第二电压时关断所述第一晶体管。

93.尽管本实用新型已经参考说明性实施例进行了描述,但是本说明书不旨在限制意义上进行解释。参考本说明书,本实用新型的说明性实施例以及其他实施例的各种修改和组合对于本领域的技术人员来说是显而易见的。因此,所附权利要求包含任何此类修改或实施例。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1