一种低温漂的高阶温度补偿MOS带隙基准电路

一种低温漂的高阶温度补偿mos带隙基准电路

技术领域

1.本发明涉及微电子技术领域,具体地说,是一种低温漂的高阶温度补偿mos带隙基准电路。

背景技术:

2.带隙基准电路是现代模拟集成电路、数模混合集成电路的重要模块,其性能特性直接影响整个电路的性能,这就要求提高带隙基准电路的性能特性。

3.图1为一种传统的带隙基准电路结构,其基本思路是利用具有负温度特性的pnp型三极管q1发射极

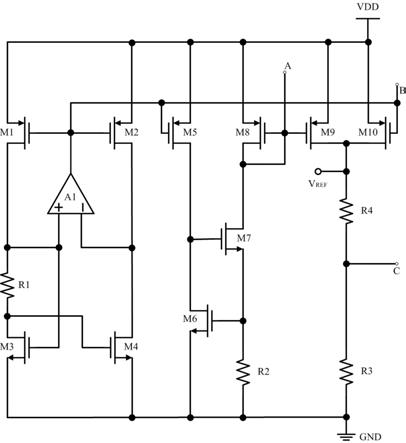

‑

基极电压veb1与具有正温度特性的两个pnp型三极管的发射极

‑

基极电压之差进行加权,获得零温度特性的基准电压。其中电阻r1与电阻r2采用相同材料,pmos管m1、pmos管m2及pmos管m3具有相同的沟道宽长比,pnp型三极管q2发射极面积是pnp型三极管q1和pnp型三极管q3发射极面积的n倍。则,传统的带隙基准电路的输出电压v

ref

为:式中,v

t

是有正温度系数的热电压,v

eb3

是pnp型三极管q3的发射

‑

基极电压,r1、r2是阻抗值。通过调节电阻r1、电阻r2及参数n可以使得输出电压v

ref

在一定温度范围内具有零温度特性。由于v

eb3

具有非线性,使得传统的一阶带隙基准电路输出电压具有高温度系数的缺点,因此传统的一阶带隙基准电路在高精度系统中的应用受到了很大的限制。

技术实现要素:

4.本发明的目的在于解决上述已有技术问题,设计了一种低温漂的高阶温度补偿mos带隙基准电路。

5.本发明通过下述技术方案实现:一种低温漂的高阶温度补偿mos带隙基准电路,包括一阶mos带隙基准电路、高温区域补偿电路、低温区域补偿电路及启动电路,所述一阶mos带隙基准电路的信号输出端分别电连接高温区域补偿电路的信号输入端、低温区域补偿电路的信号输入端及启动电路的信号输入端,所述启动电路的信号输出端电连接一阶mos带隙基准电路的启动信号输入端,所述一阶mos带隙基准电路产生低温度系数的带隙参考电压,所述高温区域补偿电路与低温区域补偿电路对所述一阶mos带隙基准电路所产生的带隙参考电压进行温度补偿,所述启动电路为一阶mos带隙基准电路提供启动信号。

6.进一步的为更好地实现本发明,特别采用下述设置方式:所述一阶mos带隙基准电路采用工作在亚阈值区的nmos管的栅极

‑

源极电压产生具有负温度系数的电压v

ctat

,两个工作在亚阈值区的nmos管的栅极

‑

源极电压之差产生具有正温度系数的电压v

ptat

,电压v

ctat

和电压v

ptat

加权获得一阶带隙基准电压。

7.进一步的为更好地实现本发明,特别采用下述设置方式:所述一阶mos带隙基准电路包括pmos管m1、pmos管m2、pmos管m5、pmos管m8、pmos管m9、pmos管m10、nmos管m3、nmos管m4、nmos管m6、nmos管m7、电阻r1、电阻r2、电阻r3、电阻r4、误差放大器a1,pmos管m1的源极分别与pmos管m2的源极、pmos管m5的源极、pmos管m8的源极、pmos管m9的源极、pmos管m10的

源极及外部电源vdd相连,pmos管m1的漏极分别与误差放大器a1的正向输入端及电阻r1的一端相连,电阻r1的另一端分别与nmos管m4的栅极、nmos管m3的漏极相连,pmos管m1的栅极分别与误差放大器a1的输出端、pmos管m2的栅极、pmos管m5的栅极、pmos管m10的栅极、高温区域补偿电路、低温区域补偿电路及启动电路相连接,pmos管m2的漏极分别与误差放大器a1的反向输入端及nmos管m4的漏极相连,pmos管m5的漏极分别与nmos管m6的漏极及nmos管m7的栅极相连,pmos管m8的栅极分别与pmos管m8的漏极、pmos管m9的栅极、nmos管m7的漏极相连接,nmos管m7的源极分别与nmos管m6的栅极及电阻r2的一端相连,电阻r2的另一端与外部地线gnd相连,pmos管m9的漏极分别与pmos管m10的漏极及电阻r4的一端相连,且pmos管m9的漏极和pmos管m10的漏极相连接的节点还作为带隙基准输出端vref,电阻r4的另一端通过电阻r3接入外部地线gnd;pmos管m8的栅极与pmos管m9的栅极共接的节点接入高温区域补偿电路和低温区域补偿电路,误差放大器a1的输出端及电阻r3和电阻r4共接的节点接入高温区域补偿电路、低温区域补偿电路及启动电路。

8.进一步的为更好地实现本发明,特别采用下述设置方式:所述nmos管m3、nmos管m4及nmos管m6都工作在亚阈值区,pmos管m10的漏极电流在电阻r3和电阻r4上产生电压v

ptat

,且pmos管m9的漏极电流在电阻r3与电阻r4上产生电压v

ctat

,且式(1)和式(2)中,q是电子电荷,k是玻尔兹曼常数,t是绝对温度,m为nmos管m4的沟道宽长比与nmos管m3的沟道宽长比的比值,β2为pmos管m10的沟道宽长比与pmos管m1的沟道宽长比的比值,β3为pmos管m9的沟道宽长比与pmos管m8的沟道宽长比的比值,v

gs6

为nmos管m6的栅极

‑

源极电压,且v

gs6

具有负温度特性,电压v

ctat

具有负温度特性。

9.作为优选的设置方案,所述pmos管m1与pmos管m2具有相同的沟道长度,nmos管m6与nmos管m7具有相同的沟道长度,nmos管m4的沟道宽长比是nmos管m3的m倍,pmos管m5的沟道宽长比是pmos管m1的β1倍,pmos管m10的沟道宽长比是pmos管m1的β2倍,pmos管m9的沟道宽长比是pmos管m8的β3倍,nmos管m3、nmos管m4及nmos管m6都工作在亚阈值区,pmos管m10的漏极电流在电阻r3和电阻r4上产生电压v

ptat

,且式中,r1、r3与r4分别为电阻r1、电阻r3与电阻r4的阻值,q是电子电荷,k是玻尔兹曼常数,t是绝对温度;所有电阻采用相同材料,电压v

ptat

具有正温度特性。

10.pmos管m8和pmos管m9具有相同的沟道宽长,pmos管m9的漏极电流i9在电阻r3与电阻r4上产生电压v

ctat

,且式中,r2为电阻r2的阻值,v

gs6

为nmos管m6的栅极

‑

源极电压,且v

gs6

具有负温度特性,电压v

ctat

具有负温度特性。

11.进一步的为更好地实现本发明,特别采用下述设置方式:所述高温区域补偿电路包括pmos管m11、pmos管m14、pmos管m17、pmos管m20、nmos管m12、nmos管m13、nmos管m15、nmos管m16、nmos管m18、nmos管m19、nmos管m21及nmos管m22,所述pmos管m11的栅极连接pmos管m8的栅极及pmos管m17的栅极,pmos管m11的源极分别与pmos管m14的源极、pmos管m17的源极、pmos管m20的源极及外部电源vdd相连,pmos管m11的漏极分别与nmos管m12的栅极、nmos管m12的漏极及nmos管m13的栅极相连,nmos管m12的源极分别与nmos管m13的源极、

nmos管m15的源极、nmos管m16的源极、nmos管m18的源极、nmos管m19的源极、nmos管m21的源极、nmos管m22的源极及外部地线gnd相连,pmos管m14的漏极分别与nmos管m13的漏极、nmos管m15的栅极、nmos管m15的漏极及nmos管m16的栅极相连,nmos管m16的漏极分别与电阻r3和电阻r4的共接节点及nmos管m22的漏极相连,pmos管m17的漏极分别与nmos管m18的漏极、nmos管m18的栅极及nmos管m19的栅极相连,pmos管m20的漏极分别与nmos管m19的漏极、nmos管m21的漏极、nmos管m21的栅极及nmos管m22的栅极相连,pmos管m14的栅极、pmos管m20的栅极皆与误差放大器a1的输出端相连接,nmos管m22的漏极连接电阻r3和电阻r4的共接节点。

12.进一步的为更好地实现本发明,特别采用下述设置方式:所述nmos管m16的漏极电流i

16

在电阻r4上产生的电压v

nl1

为:nmos管m22的漏极电流i

22

在电阻r4上产生的电压v

nl2

为:为:式(3)和式(4)中,β4为pmos管m11的沟道宽长比与pmos管m8的沟道宽长比的比值,β5为pmos管m14的沟道宽长比与pmos管m1的沟道宽长比的比值,β6为nmos管m16的沟道宽长比与nmos管m15的沟道宽长比的比值,β7为pmos管m17的沟道宽长比与pmos管m8的沟道宽长比的比值,β8为pmos管m20的沟道宽长比与pmos管m1的沟道宽长比的比值,β9为nmos管m22的沟道宽长比与nmos管m21的沟道宽长比的比值,q是电子电荷,k是玻尔兹曼常数,t是绝对温度,m为nmos管m4的沟道宽长比与nmos管m3的沟道宽长比的比值,v

gs6

为nmos管m6的栅极

‑

源极电压,t

r1

为参考温度且大于室温,t

r2

为参考温度且大于参考温度t

r1

。

13.作为优选的设置方案,所述高温区域温度曲率补偿电路中pmos管m11的沟道宽长比是pmos管m8的β4倍,pmos管m14的沟道宽长比是pmos管m1的β5倍,nmos管m16的沟道宽长比是nmos管m15的β6倍,nmos管m12与nmos管m13具有相同的沟道宽长,pmos管m17的沟道宽长比是pmos管m8的β7倍,pmos管m20的沟道宽长比是pmos管m1的β8倍,nmos管m22的沟道宽长比是nmos管m21的β9倍,nmos管m18与nmos管m19具有相同的沟道宽长,nmos管m16的漏极电流i

16

在电阻r4上产生的电压v

nl1

为:nmos管m22的漏极电流i

22

在电阻r4上产生的电压v

nl2

为:式中,t

r1

为参考温度且大于室温,t

r2

为参考温度且大于参考温度t

r1

。

14.进一步的为更好地实现本发明,特别采用下述设置方式:所述低温区域补偿电路包括pmos管m23、pmos管m26、pmos管m29、pmos管m32、nmos管m24、nmos管m25、nmos管m27、nmos管m28、nmos管m30、nmos管m31、nmos管m33及nmos管m34,所述pmos管m23的源极分别与pmos管m26的源极、pmos管m29的源极、pmos管m32的源极以及外部电源vdd相连,pmos管m23的栅极分别与误差放大器a1的输出端及pmos管m29的栅极相连接,pmos管m23的漏极分别与

nmos管m24的栅极、nmos管m24的漏极及nmos管m25的栅极相连,nmos管m24的源极分别与nmos管m25的源极、nmos管m27的源极、nmos管m28的源极、nmos管m30的源极、nmos管m31的源极、nmos管m33的源极、nmos管m34的源极以及外部地线gnd相连,pmos管m26的栅极翻白眼pmos管m32的栅极及pmos管m8的栅极相连接,pmos管m26的漏极分别与nmos管m25的漏极、nmos管m27的栅极、nmos管m27的漏极以及nmos管m28的栅极相连,nmos管m28的漏极分别与电阻r3和电阻r4的共接节点及nmos管m34的漏极相连接,pmos管m29的漏极分别与nmos管m30的漏极、nmos管m30的栅极及nmos管m31的栅极相连,pmos管m32的漏极分别与nmos管m31的漏极、nmos管m33的漏极、nmos管m33的栅极以及nmos管m34的栅极相连接。

15.进一步的为更好地实现本发明,特别采用下述设置方式:所述nmos管m28的漏极电流i

28

在电阻r4上产生的电压v

nl3

为:所述nmos管m34的漏极电流i

34

在电阻r4上产生的电压v

nl4

为为式(5)和式(6)中,β

10

为pmos管m23的沟道宽长比与pmos管m1的沟道宽长比的比值,β

11

为pmos管m26的沟道宽长比与pmos管m8的沟道宽长比的比值,β

12

为nmos管m28的沟道宽长比与nmos管m27的沟道宽长比的比值,β

13

为pmos管m29的沟道宽长比与pmos管m1的沟道宽长比的比值,β

14

倍为pmos管m32的沟道宽长比与pmos管m8的沟道宽长比的比值,β

15

为nmos管m34的沟道宽长比与nmos管m33的沟道宽长比的比值,q是电子电荷,k是玻尔兹曼常数,t是绝对温度,m为nmos管m4的沟道宽长比与nmos管m3的沟道宽长比的比值,v

gs6

为nmos管m6的栅极

‑

源极电压,t

r3

为参考温度且小于室温,t

r4

为参考温度且小于参考温度t

r3

;

16.作为优选的设置方案,所述pmos管m23的沟道宽长比是pmos管m1的β

10

倍,pmos管m26的沟道宽长比是pmos管m8的β

11

倍,nmos管m28的沟道宽长比是nmos管m27的β

12

倍,nmos管m24与nmos管m25具有相同的沟道宽长,pmos管m29的沟道宽长比是pmos管m1的β

13

倍,pmos管m32的沟道宽长比是pmos管m8的β

14

倍,nmos管m34的沟道宽长比是nmos管m33的β

15

倍,nmos管m30与nmos管m31具有相同的沟道宽长,则nmos管m28的漏极电流i

28

在电阻r4上产生的电压v

nl3

为:nmos管m34的漏极电流i

34

在电阻r4上产生的电压v

nl4

为:式中,t

r3

为参考温度且小于室温,t

r4

为参考温度且小于参考温度t

r3

。

17.进一步的为更好地实现本发明,特别采用下述设置方式:所述启动电路包括pmos管ms1、pmos管ms2、nmos管ms3以及nmos管ms4,pmos管ms1的源极与外部电源vdd相连,pmos管ms1的栅极分别与pmos管ms1的漏极以及pmos管ms2的源极相连,pmos管ms2的栅极分别与pmos管ms2的漏极、nmos管ms3的栅极及nmos管ms4的漏极相连接,nmos管ms3的源极分别与nmos管ms4的源极以及外部地线gnd相连,nmos管ms3的漏接连接误差放大器a1的输出端,

nmos管ms4的栅极连接电阻r3和电阻r4的共接节点。

18.进一步的为更好地实现本发明,特别采用下述设置方式:所述低温漂的高阶温度补偿mos带隙基准电路的输出电压为v

ref

,且v

ref

=v

ptat

+v

ctat

‑

v

nl1

‑

v

nl2

‑

v

nl3

‑

v

nl4

,其中,v

ptat

为具有正温度系数电压,v

ctat

为具有负温度系数电压,v

nl1

和v

nl2

为高温区具有温度曲率特性电压,v

nl3

和v

nl4

为低温区具有温度分段特性电压。

19.本发明与现有技术相比,具有以下优点及有益效果:

20.本发明采用工作在亚阈值区的nmos管的栅极

‑

源极电压产生负温度系数的电压v

ctat

,两个工作在亚阈值区的nmos管的栅极

‑

源极电压之差产生正温度系数的电压v

ptat

,两者加权获得一阶带隙基准电压,高温区域温度曲率补偿电路(高温区域补偿电路)中nmos管m16的漏极电流在电阻r4上产生电压v

nl1

与nmos管m22的漏极电流在电阻r4上产生的电压v

nl2

在高温区域对带隙基准电压进行补偿,低温区域温度分段补偿电路(低温区域补偿电路)中nmos管m28的漏极电流在电阻r4上产生的电压v

nl3

与nmos管m34的漏极电流在电阻r4上产生的电压v

nl4

在低温区域对带隙基准电压进行补偿,从而获得高阶温度补偿的带隙基准电压。

21.本发明一阶带隙基准利用工作在亚阈值区的nmos管的栅极

‑

源极电压产生负温度系数的电压v

ctat

,两个工作在亚阈值区的nmos管的栅极

‑

源极电压之差产生正温度系数的电压v

ptat

,两者加权获得一阶带隙基准电压,利用随着温度t升高而呈曲线增加的电压v

nl1

和v

nl2

以及随着温度t升高而呈曲线降低的电压v

nl3

和v

nl4

对带隙基准电压进行高阶补偿,以此有效地降低基准电压的温度系数。

附图说明

22.图1为传统的带隙基准电路结构。

23.图2为本发明的电路结构图(一阶mos带隙基准电路部分)。

24.图3为本发明的电路结构图(高温区域补偿电路部分)。

25.图4为本发明的电路结构图(低温区域补偿电路及启动电路部分).

26.图5为一阶带隙基准电压曲线。

27.图6为本发明的mos管实现高阶温度补偿带隙基准电路的输出电压曲线示意图。

28.图7为本发明的mos管实现高阶温度补偿带隙基准电路的输出电压温度特性仿真。

29.其中,图2、图3和图4中的a、b、c为单个电路之间相互连接的节点。

具体实施方式

30.下面结合实施例对本发明作进一步地详细说明,但本发明的实施方式不限于此。

31.为使本发明实施方式的目的、技术方案和优点更加清楚,下面将结合本发明实施方式中的附图,对本发明实施方式中的技术方案进行清楚、完整地描述,显然,所描述的实施方式是本发明一部分实施方式,而不是全部的实施方式。基于本发明中的实施方式,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施方式,都属于本发明保护的范围。因此,以下对在附图中提供的本发明的实施方式的详细描述并非旨在限制要求保护的本发明的范围,而是仅仅表示本发明的选定实施方式。

32.在本发明的描述中,需要理解的是,术语等指示的方位或位置关系为基于附图所

示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的设备或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。

33.此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本发明的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

34.在本发明中,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”、“固定”等术语应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或成一体。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本发明中的具体含义。

35.在本发明中,除非另有明确的规定和限定,第一特征在第二特征之“上”或之“下”可以包括第一和第二特征直接接触,也可以包括第一和第二特征不是直接接触而是通过它们之间的另外的特征接触。而且,第一特征在第二特征“之上”、“上方”和“上面”包括第一特征在第二特征正上方和斜上方,或仅仅表示第一特征水平高度高于第二特征。第一特征在第二特征“之下”、“下方”和“下面”包括第一特征在第二特征正下方和斜下方,或仅仅表示第一特征水平高度小于第二特征。

36.值得注意的是:在本申请中,某些需要应用到本领域的公知技术或常规技术手段时,申请人可能存在没有在文中具体的阐述该公知技术或/和常规技术手段是一种什么样的技术手段,但不能以文中没有具体公布该技术手段,而认为本申请不符合专利法第二十六条第三款的情况。

37.实施例1:

38.一种低温漂的高阶温度补偿mos带隙基准电路,如图2~图4所示,特别采用下述设置方式:包括一阶mos带隙基准电路、高温区域补偿电路、低温区域补偿电路及启动电路,所述一阶mos带隙基准电路的信号输出端分别电连接高温区域补偿电路的信号输入端、低温区域补偿电路的信号输入端及启动电路的信号输入端,所述启动电路的信号输出端电连接一阶mos带隙基准电路的启动信号输入端,所述一阶mos带隙基准电路产生低温度系数的带隙参考电压,所述高温区域补偿电路与低温区域补偿电路对所述一阶mos带隙基准电路所产生的带隙参考电压进行温度补偿,所述启动电路为一阶mos带隙基准电路提供启动信号。

39.实施例2:

40.本实施例是在上述实施例的基础上进一步优化,与前述技术方案相同部分在此将不再赘述,如图2~图4所示,进一步的为更好地实现本发明,特别采用下述设置方式:所述一阶mos带隙基准电路采用工作在亚阈值区的nmos管的栅极

‑

源极电压产生具有负温度系数的电压v

ctat

,两个工作在亚阈值区的nmos管的栅极

‑

源极电压之差产生具有正温度系数的电压v

ptat

,电压v

ctat

和电压v

ptat

加权获得一阶带隙基准电压。

41.实施例3:

42.本实施例是在上述任一实施例的基础上进一步优化,与前述技术方案相同部分在此将不再赘述,如图2~图4所示,进一步的为更好地实现本发明,特别采用下述设置方式:所述一阶mos带隙基准电路包括pmos管m1、pmos管m2、pmos管m5、pmos管m8、pmos管m9、pmos管m10、nmos管m3、nmos管m4、nmos管m6、nmos管m7、电阻r1、电阻r2、电阻r3、电阻r4、误差放

大器a1,pmos管m1的源极分别与pmos管m2的源极、pmos管m5的源极、pmos管m8的源极、pmos管m9的源极、pmos管m10的源极及外部电源vdd相连,pmos管m1的漏极分别与误差放大器a1的正向输入端及电阻r1的一端相连,电阻r1的另一端分别与nmos管m4的栅极、nmos管m3的漏极相连,pmos管m1的栅极分别与误差放大器a1的输出端、pmos管m2的栅极、pmos管m5的栅极、pmos管m10的栅极、高温区域补偿电路、低温区域补偿电路及启动电路相连接,pmos管m2的漏极分别与误差放大器a1的反向输入端及nmos管m4的漏极相连,pmos管m5的漏极分别与nmos管m6的漏极及nmos管m7的栅极相连,pmos管m8的栅极分别与pmos管m8的漏极、pmos管m9的栅极、nmos管m7的漏极相连接,nmos管m7的源极分别与nmos管m6的栅极及电阻r2的一端相连,电阻r2的另一端与外部地线gnd相连,pmos管m9的漏极分别与pmos管m10的漏极及电阻r4的一端相连,且pmos管m9的漏极和pmos管m10的漏极相连接的节点还作为带隙基准输出端vref,电阻r4的另一端通过电阻r3接入外部地线gnd;pmos管m8的栅极与pmos管m9的栅极共接的节点接入高温区域补偿电路和低温区域补偿电路,误差放大器a1的输出端及电阻r3和电阻r4共接的节点接入高温区域补偿电路、低温区域补偿电路及启动电路。

43.实施例4:

44.本实施例是在上述任一实施例的基础上进一步优化,与前述技术方案相同部分在此将不再赘述,如图2~图4所示,进一步的为更好地实现本发明,特别采用下述设置方式:所述nmos管m3、nmos管m4及nmos管m6都工作在亚阈值区,pmos管m10的漏极电流在电阻r3和电阻r4上产生电压v

ptat

,且pmos管m9的漏极电流在电阻r3与电阻r4上产生电压v

ctat

,且式(1)和式(2)中,q是电子电荷,k是玻尔兹曼常数,t是绝对温度,m为nmos管m4的沟道宽长比与nmos管m3的沟道宽长比的比值,β2为pmos管m10的沟道宽长比与pmos管m1的沟道宽长比的比值,β3为pmos管m9的沟道宽长比与pmos管m8的沟道宽长比的比值,v

gs6

为nmos管m6的栅极

‑

源极电压,且v

gs6

具有负温度特性,电压v

ctat

具有负温度特性。

45.实施例5:

46.本实施例是在上述任一实施例的基础上进一步优化,与前述技术方案相同部分在此将不再赘述,如图2~图4所示,进一步的为更好地实现本发明,特别采用下述设置方式:所述高温区域补偿电路包括pmos管m11、pmos管m14、pmos管m17、pmos管m20、nmos管m12、nmos管m13、nmos管m15、nmos管m16、nmos管m18、nmos管m19、nmos管m21及nmos管m22,所述pmos管m11的栅极连接pmos管m8的栅极及pmos管m17的栅极,pmos管m11的源极分别与pmos管m14的源极、pmos管m17的源极、pmos管m20的源极及外部电源vdd相连,pmos管m11的漏极分别与nmos管m12的栅极、nmos管m12的漏极及nmos管m13的栅极相连,nmos管m12的源极分别与nmos管m13的源极、nmos管m15的源极、nmos管m16的源极、nmos管m18的源极、nmos管m19的源极、nmos管m21的源极、nmos管m22的源极及外部地线gnd相连,pmos管m14的漏极分别与nmos管m13的漏极、nmos管m15的栅极、nmos管m15的漏极及nmos管m16的栅极相连,nmos管m16的漏极分别与电阻r3和电阻r4的共接节点及nmos管m22的漏极相连,pmos管m17的漏极分别与nmos管m18的漏极、nmos管m18的栅极及nmos管m19的栅极相连,pmos管m20的漏极分别与nmos管m19的漏极、nmos管m21的漏极、nmos管m21的栅极及nmos管m22的栅极相连,pmos

管m14的栅极、pmos管m20的栅极皆与误差放大器a1的输出端相连接,nmos管m22的漏极连接电阻r3和电阻r4的共接节点。

47.实施例6:

48.本实施例是在上述任一实施例的基础上进一步优化,与前述技术方案相同部分在此将不再赘述,如图2~图4所示,进一步的为更好地实现本发明,特别采用下述设置方式:所述nmos管m16的漏极电流i

16

在电阻r4上产生的电压v

nl1

为:为:nmos管m22的漏极电流i

22

在电阻r4上产生的电压v

nl2

为:式(3)和式(4)中,β4为pmos管m11的沟道宽长比与pmos管m8的沟道宽长比的比值,β5为pmos管m14的沟道宽长比与pmos管m1的沟道宽长比的比值,β6为nmos管m16的沟道宽长比与nmos管m15的沟道宽长比的比值,β7为pmos管m17的沟道宽长比与pmos管m8的沟道宽长比的比值,β8为pmos管m20的沟道宽长比与pmos管m1的沟道宽长比的比值,β9为nmos管m22的沟道宽长比与nmos管m21的沟道宽长比的比值,q是电子电荷,k是玻尔兹曼常数,t是绝对温度,m为nmos管m4的沟道宽长比与nmos管m3的沟道宽长比的比值,v

gs6

为nmos管m6的栅极

‑

源极电压,t

r1

为参考温度且大于室温,t

r2

为参考温度且大于参考温度t

r1

。

49.实施例7:

50.本实施例是在上述任一实施例的基础上进一步优化,与前述技术方案相同部分在此将不再赘述,如图2~图4所示,进一步的为更好地实现本发明,特别采用下述设置方式:所述低温区域补偿电路包括pmos管m23、pmos管m26、pmos管m29、pmos管m32、nmos管m24、nmos管m25、nmos管m27、nmos管m28、nmos管m30、nmos管m31、nmos管m33及nmos管m34,所述pmos管m23的源极分别与pmos管m26的源极、pmos管m29的源极、pmos管m32的源极以及外部电源vdd相连,pmos管m23的栅极分别与误差放大器a1的输出端及pmos管m29的栅极相连接,pmos管m23的漏极分别与nmos管m24的栅极、nmos管m24的漏极及nmos管m25的栅极相连,nmos管m24的源极分别与nmos管m25的源极、nmos管m27的源极、nmos管m28的源极、nmos管m30的源极、nmos管m31的源极、nmos管m33的源极、nmos管m34的源极以及外部地线gnd相连,pmos管m26的栅极翻白眼pmos管m32的栅极及pmos管m8的栅极相连接,pmos管m26的漏极分别与nmos管m25的漏极、nmos管m27的栅极、nmos管m27的漏极以及nmos管m28的栅极相连,nmos管m28的漏极分别与电阻r3和电阻r4的共接节点及nmos管m34的漏极相连接,pmos管m29的漏极分别与nmos管m30的漏极、nmos管m30的栅极及nmos管m31的栅极相连,pmos管m32的漏极分别与nmos管m31的漏极、nmos管m33的漏极、nmos管m33的栅极以及nmos管m34的栅极相连接。

51.实施例8:

52.本实施例是在上述任一实施例的基础上进一步优化,与前述技术方案相同部分在此将不再赘述,如图2~图4所示,进一步的为更好地实现本发明,特别采用下述设置方式:所述nmos管m28的漏极电流i

28

在电阻r4上产生的电压v

nl3

为:

所述nmos管m34的漏极电流i

34

在电阻r4上产生的电压v

nl4

为式(5)和式(6)中,β

10

为pmos管m23的沟道宽长比与pmos管m1的沟道宽长比的比值,β

11

为pmos管m26的沟道宽长比与pmos管m8的沟道宽长比的比值,β

12

为nmos管m28的沟道宽长比与nmos管m27的沟道宽长比的比值,β

13

为pmos管m29的沟道宽长比与pmos管m1的沟道宽长比的比值,β

14

倍为pmos管m32的沟道宽长比与pmos管m8的沟道宽长比的比值,β

15

为nmos管m34的沟道宽长比与nmos管m33的沟道宽长比的比值,q是电子电荷,k是玻尔兹曼常数,t是绝对温度,m为nmos管m4的沟道宽长比与nmos管m3的沟道宽长比的比值,v

gs6

为nmos管m6的栅极

‑

源极电压,t

r3

为参考温度且小于室温,t

r4

为参考温度且小于参考温度t

r3

;

53.实施例9:

54.本实施例是在上述任一实施例的基础上进一步优化,与前述技术方案相同部分在此将不再赘述,如图2~图4所示,进一步的为更好地实现本发明,特别采用下述设置方式:所述启动电路包括pmos管ms1、pmos管ms2、nmos管ms3以及nmos管ms4,pmos管ms1的源极与外部电源vdd相连,pmos管ms1的栅极分别与pmos管ms1的漏极以及pmos管ms2的源极相连,pmos管ms2的栅极分别与pmos管ms2的漏极、nmos管ms3的栅极及nmos管ms4的漏极相连接,nmos管ms3的源极分别与nmos管ms4的源极以及外部地线gnd相连,nmos管ms3的漏接连接误差放大器a1的输出端,nmos管ms4的栅极连接电阻r3和电阻r4的共接节点。

55.实施例10:

56.本实施例是在上述任一实施例的基础上进一步优化,与前述技术方案相同部分在此将不再赘述,如图2~图4所示,进一步的为更好地实现本发明,特别采用下述设置方式:所述低温漂的高阶温度补偿mos带隙基准电路的输出电压为v

ref

,且v

ref

=v

ptat

+v

ctat

‑

v

nl1

‑

v

nl2

‑

v

nl3

‑

v

nl4

,其中,v

ptat

为具有正温度系数电压,v

ctat

为具有负温度系数电压,v

nl1

和v

nl2

为高温区具有温度曲率特性电压,v

nl3

和v

nl4

为低温区具有温度分段特性电压。

57.实施例11:

58.一种低温漂的高阶温度补偿mos带隙基准电路,如图2~图4所示,包括一阶mos带隙基准电路、高温区域补偿电路(高温区域温度曲率补偿电路)、低温区域补偿电路(低温区域温度分段补偿电路)及启动电路;

59.其中,一阶mos带隙基准电路的信号输出端分别电连接高温区域温度曲率补偿电路的信号输入端、低温区域温度分段补偿电路的信号输入端以及启动电路的信号输入端,启动电路的信号输出端电连接一阶mos带隙基准电路的启动信号输入端;启动电路使得一阶mos带隙基准电路正常工作并产生带隙基准电压输出,一阶mos带隙基准电路产生正温度系数的电压v

ptat

和负温度系数的电压v

ctat

,同时将电压v

ptat

和电压v

ctat

加权产生低温度系数的带隙基准电压(即整个电路的输出电压)v

ref

,高温区域温度曲率补偿电路中nmos管m16的漏极电流在电阻r4上产生电压v

nl1

与nmos管m22的漏极电流在电阻r4上产生的电压v

nl2

在高温区域对带隙基准电压进行补偿,低温区域温度分段补偿电路中nmos管m28的漏极电流在电阻r4上产生的电压v

nl3

与nmos管m34的漏极电流在电阻r4上产生的电压v

nl4

在低温区域

对带隙基准电压进行补偿,从而获得高阶温度补偿后的带隙基准电压v

ref

。

60.启动电路只在一阶mos带隙基准电路上电时发挥作用,当带隙基准参考电路启动完成后,启动电路停止工作,避免了启动电路对后面电路的影响。

61.作为一种优选的技术方案,如图2~图4所示,一阶带隙基准电路包括:pmos管m1、pmos管m2、pmos管m5、pmos管m8、pmos管m9、pmos管m10、nmos管m3、nmos管m4、nmos管m6、nmos管m7、电阻r1、电阻r2、电阻r3、电阻r4、误差放大器a1;

62.高温区域温度曲率补偿电路包括:pmos管m11、pmos管m14、pmos管m17、pmos管m20、nmos管m12、nmos管m13、nmos管m15、nmos管m16、nmos管m18、nmos管m19、nmos管m21以及nmos管m22;

63.低温区域温度分段补偿电路包括:pmos管m23、pmos管m26、pmos管m29、pmos管m32、nmos管m24、nmos管m25、nmos管m27、nmos管m28、nmos管m30、nmos管m31、nmos管m33以及nmos管m34;

64.启动电路4包括:pmos管ms1、pmos管ms2、nmos管ms3以及nmos管ms4。

65.pmos管m1的源极分别与pmos管m2的源极、pmos管m5的源极、pmos管m8的源极、pmos管m9的源极、pmos管m10的源极、pmos管m11的源极、pmos管m14的源极、pmos管m17的源极、pmos管m20的源极、pmos管m23的源极、pmos管m26的源极、pmos管m29的源极、pmos管m32的源极、pmos管ms1的源极以及外部电源vdd相连接。

66.pmos管m1的漏极分别与误差放大器a1的正向输入端以及电阻r1的一端相连,电阻r1的另一端分别与nmos管m4的栅极、nmos管m3的漏极相连;

67.pmos管m1的栅极分别与误差放大器a1的输出端、pmos管m2的栅极、pmos管m5的栅极、pmos管m10的栅极、pmos管m14的栅极、pmos管m20的栅极、pmos管m23的栅极、pmos管m29的栅极以及nmos管ms3的漏极相连;

68.pmos管m2的漏极分别与误差放大器a1的反向输入端以及nmos管m4的漏极相连,pmos管m5的漏极分别与nmos管m6的漏极以及pmos管m7的栅极相连;

69.pmos管m8的栅极分别与pmos管m8的漏极、pmos管m9的栅极、pmos管m11的栅极、pmos管m17的栅极、pmos管m26的栅极以及pmos管m32的栅极相连,pmos管m7的源极分别与pmos管m6的栅极以及电阻r2的一端相连;

70.pmos管m9的漏极分别与pmos管m10的漏极以及电阻r4的一端相连,且pmos管m9的漏极和pmos管m10的漏极相连接的节点还作为带隙基准输出端vref;

71.电阻r4的另一端分别与nmos管m16的漏极、nmos管m22的漏极、nmos管m28的漏极、nmos管m34的漏极、nmos管ms4的栅极以及电阻r3的一端相连,电阻r3的另一端分别与nmos管m3的源极、nmos管m4的源极、nmos管m6的源极、电阻r2的另一端、nmos管m12是源极、nmos管m13的源极、nmos管m15的源极、nmos管m18是源极、nmos管m19的源极、nmos管m21的源极、nmos管m22的源极、nmos管m24的源极、nmos管m25的源极、nmos管m27的源极、nmos管m28的源极、nmos管m30的源极、nmos管m31的源极、nmos管m33的源极、nmos管m34的源极、nmos管ms3的源极、nmos管ms4的源极以及外部地线gnd相连接。

72.pmos管m11的漏极分别与nmos管m12的栅极、nmos管m12的漏极以及nmos管m13的栅极相连,pmos管m14的漏极分别与nmos管m13的漏极、nmos管m15的栅极、nmos管m15的漏极以及nmos管m16的栅极相连,nmos管m16的漏极分别与电阻r3和电阻r4的共接节点、nmos管m22

的漏极、nmos管m28的漏极、nmos管m34的漏极及nmos管ms4的栅极相连,pmos管m17的漏极分别与nmos管m18的漏极、nmos管m18的栅极以及nmos管m19的栅极相连,pmos管m20的漏极分别与nmos管m19的漏极、nmos管m21的漏极、nmos管m21的栅极以及nmos管m22的栅极相连。

73.pmos管m23的漏极分别与nmos管m24的栅极、nmos管m24的漏极以及nmos管m25的栅极相连,pmos管m26的漏极分别与nmos管m25的漏极、nmos管m27的栅极、nmos管m27的漏极以及nmos管m28的栅极相连,pmos管m29的漏极分别与nmos管m30的漏极、nmos管m30的栅极以及nmos管m31的栅极相连,pmos管m32的漏极分别与nmos管m31的漏极、nmos管m33的漏极、nmos管m33的栅极以及nmos管m34的栅极相连。

74.pmos管ms1的栅极分别与pmos管ms1的漏极以及pmos管ms2的源极相连,pmos管ms2的栅极分别与pmos管ms2的漏极、nmos管ms3的栅极以及nmos管ms4的漏极相连。

75.所述一阶mos带隙基准电路中,工作在亚阈值区的nmos管m4的栅极

‑

源极电压v

gs4

与pnp型三极管的基极与集电极短接时发射极

‑

基极电压具有相似的性能特性,即nmos管m4的栅极

‑

源极电压v

gs4

具有负温度特性;相似地,nmos管m3的栅极

‑

源极电压v

gs3

与pnp型三极管的基极与集电极短接时发射极

‑

基极电压具有相似的性能特性,即nmos管m3的栅极

‑

源极电压v

gs3

具有负温度特性。

76.pmos管m1与pmos管m2具有相同的沟道长度,nmos管m6与nmos管m7具有相同的沟道长度,nmos管m4的沟道宽长比是nmos管m3的m倍,则pmos管m1的漏极电流i1为:

[0077][0078]

式中,r1为电阻r1的阻值,q为电子电荷,k为波尔兹曼常数,t为绝对温度。pmos管m10的沟道宽长比是pmos管m1的β2倍,则pmos管m10的漏极电流i

10

在电阻r3与电阻r4上产生电压v

ptat

为:

[0079][0080]

式中,r3与r4分别为电阻r3与电阻r4的阻值,且本发明中所有电阻采用同一材料实现,则v

ptat

具有正温度特性。pmos管m8的漏极电流i8为:

[0081][0082]

式中,r2为电阻r2的阻值。pmos管m8和pmos管m9构成了一对电流镜,pmos管m9的沟道宽长比是pmos管m8的β3倍,则pmos管m9的漏极电流i9在电阻r3与电阻r4上产生电压v

ctat

有:

[0083][0084]

因而,v

ctat

具有负温度特性。

[0085]

本发明为补偿v

gs6

高温区域非线性,采用高温区域温度曲率补偿电路。pmos管m11的沟道宽长比是pmos管m8的β4倍,pmos管m14的沟道宽长比是pmos管m1的β5倍,nmos管m16的沟道宽长比是nmos管m15的β6倍,nmos管m12与nmos管m13具有相同的沟道宽长,pmos管m17的沟道宽长比是pmos管m8的β7倍,pmos管m20的沟道宽长比是pmos管m1的β8倍,nmos管m22的沟道宽长比是nmos管m21的β9倍,nmos管m18与nmos管m19具有相同的沟道宽长,nmos管m16的漏极电流i

16

在电阻r4上产生的电压v

nl1

为:

[0086][0087]

nmos管m22的漏极电流i

22

在电阻r4上产生的电压v

nl2

为:

[0088][0089]

式中,t

r1

为参考温度且大于室温,t

r2

为参考温度且大于参考温度t

r1

。

[0090]

本发明为补偿v

gs6

低温区域非线性,采用低温区域温度曲率补偿电路。pmos管m23的沟道宽长比是pmos管m1的β

10

倍,pmos管m26的沟道宽长比是pmos管m8的β

11

倍,nmos管m28的沟道宽长比是nmos管m27的β

12

倍,nmos管m24与nmos管m25具有相同的沟道宽长,mos管m29的沟道宽长比是pmos管m1的β

13

倍,pmos管m32的沟道宽长比是pmos管m8的β

14

倍,nmos管m34的沟道宽长比是nmos管m33的β

15

倍,nmos管m30与nmos管m31具有相同的沟道宽长,则nmos管m28的漏极电流i

28

在电阻r4上产生的电压v

nl3

为:

[0091][0092]

nmos管m34的漏极电流i

34

在电阻r4上产生的电压v

nl4

为:

[0093][0094]

式中,t

r3

为参考温度且小于室温,t

r4

为参考温度且小于参考温度t

r3

。

[0095]

由式(一)~式(八)可知,mos管实现高阶温度补偿带隙基准电路输出端vref的输出电压v

ref

为:

[0096]

v

ref

=v

ptat

+v

ctat

‑

v

nl1

‑

v

nl2

‑

v

nl3

‑

v

nl4

ꢀꢀꢀ

(九)

[0097]

由式(九)可知,mos管实现高阶温度补偿带隙基准电路输出电压v

ref

包含v

ptat

、v

ctat

、v

nl1

、v

nl2

、v

nl3

及v

nl4

六个因子,其中v

ptat

与v

ctat

加权构成一阶带隙基准电压,v

nl1

与v

nl2

将补偿v

gs6

高阶温度非线性,v

nl3

与v

nl4

将补偿v

gs6

高阶温度非线性,如图6所示。

[0098]

图7为本发明的mos管实现高阶温度补偿带隙基准电路的输出电压v

ref

的温度特性仿真曲线,其中横坐标为温度,纵坐标为带隙基准的输出电压。仿真结果显示,在

‑

40℃~125℃的温度范围内,mos管实现高阶温度补偿mos带隙基准电路输出电压v

ref

的温度系数为3.1ppm/℃。

[0099]

本发明的上述实施例中,通过提供mos管实现高阶温度补偿带隙基准电路,包括一阶mos带隙基准电路、高温区域温度曲率补偿电路、低温区域温度分段补偿电路及启动电路。本发明的一阶mos带隙基准电路采用工作在亚阈值区的nmos管的栅极

‑

源极电压产生具有负温度系数的电压v

ctat

,两个工作在亚阈值区的nmos管的栅极

‑

源极电压之差产生具有正温度系数的电压v

ptat

,电压v

ctat

和电压v

ptat

两者加权获得一阶带隙基准电压,并将高温区域温度曲率补偿电路中nmos管m16的漏极电流i

16

在电阻r4上产生的电压v

nl1

和nmos管m22的漏极电流i

22

在电阻r4上产生的电压v

nl2

以及低温区域温度分段补偿电路中nmos管m28的漏极电流i

28

在电阻r4上产生的电压v

nl3

和nmos管m34的漏极电流i

34

在电阻r4上产生的电压

v

nl4

引入到一阶带隙基准电压,进而得到高阶温度补偿后的带隙基准电压v

ref

。

[0100]

以上所述,仅是本发明的较佳实施例,并非对本发明做任何形式上的限制,凡是依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化,均在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1