用于处理中断的系统的制作方法

1.本发明涉及电子设备领域,尤其涉及一种中断处理和侦测的系统。

背景技术:

2.现有技术中,电子设备通过一处理器(例如中央处理器cpu、微控制器mcu、或数字信号控制器dsc)实现信号的处理和控制,其通过输入端口获得输入的数据、以及对输入信号进行相应的侦测处理获得相关信息,并输出端口用于输出数据、以及提供特殊的信号,例如,通用型的输入/输出端口(gpio,general purpose input output)既可以作为输入端口使用,也可以作为输出端口使用。有些gpio端口还可被设置执行特殊的功能,以应对日益丰富的应用需求。然而,在侦测adc信号或pwm信号时,由于输入端信号持续提供给gpio端口中断信号(或者说波形的上升沿、下降沿),gpio端口需持续执行侦测,并存储大量信息到暂存器并提供给控制器处理。持续的侦测操作和信息处理给控制器带来很大负担,直接影响了控制器的综合效能。因此,减少对升降沿的侦测,尤其是减少对具有大量连续的升降沿信号的侦测,变得尤为重要。

技术实现要素:

3.本发明的目的在于提供一种先期处理中断信号的系统,其能够大大减少处理器对于对应端口的中断侦测负担,提升处理器的综合效能。

4.为达到上述目的,本发明提供了

…

,包括,【权利要求确认后修改】

5.较佳的,。

6.与现有技术相比,本发明提供的用于处理中断的系统,其通过电路将输入的第一信号在特定的时间段内拉为稳态的高电平或低电平信号,处理器仅在这个时间段以外,通过定时轮询的方式侦测和处理该输入端口的中断需求,这样处理器无需实时进行输入信号的上升沿侦测或下降沿侦测,大大降低了处理器的负担,提升了处理器的综合效能。

附图说明

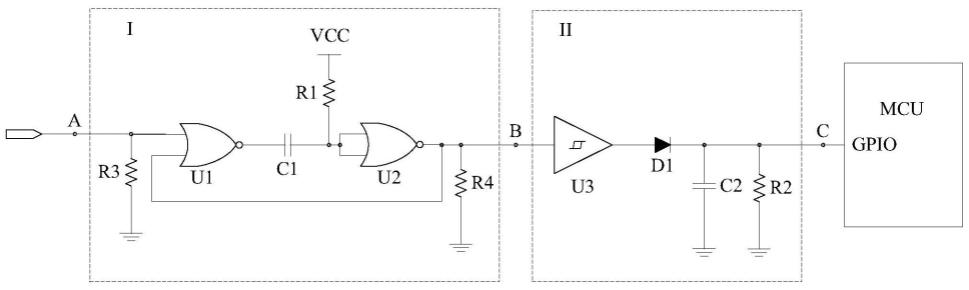

7.图1为本发明第一实施例的用于处理中断的系统的电路示意图;

8.图2为本发明第二实施例的用于处理中断的系统的电路示意图;

9.图3a为图1中a点信号的波形示意图;

10.图3b为图1中b点信号的波形示意图;

11.图3c为图1中c点信号的波形示意图。

具体实施方式

12.为使对本发明的目的、构造、特征、及其功能有进一步的了解,兹配合实施例详细说明如下。

13.在说明书及权利要求书当中使用了某些词汇来指称特定的元件。所属领域中具有

通常知识者应可理解,制造商可能会用不同的名词来称呼同一个元件。本说明书及权利要求书并不以名称的差异来作为区分元件的方式,而是以元件在功能上的差异来作为区分的准则。在通篇说明书及权利要求当中所提及的「包括」为开放式的用语,故应解释成「包括但不限定于」。

14.参照图1所示,揭示了本发明用于处理中断的系统的第一实施例的示意图,该系统包括处理器和用于处理中断的电路。

15.处理器用于中断服务,处理器包括输入端口,并自该输入端口接收中断信号。处理器可以为中央处理器cpu、微控制器mcu、或数字信号控制器dsc,图1中以mcu为例,本发明不以此为限。处理器具有用于输入端口,例如图1中以gpio端口为例,部分gpio端口可以用于接收和侦测中断信息,处理器询问该gpio端口,以侦测接收到的信号中是否存在中断,进而在存在中断时,执行相应的中断服务程序。

16.用于处理中断的电路处于第一信号和输入端口之间,用于对输入的第一信号进行处理,第一信号为沿触发的中断信号,该信号可以为上升沿触发的中断信号和/或下降沿触发的中断信号,处理后获得的信号使得该gpio端口接收到的信号在特定时间段内不存在上升沿和/或下降沿。较佳的,该第一信号为脉冲宽度调制信号pwm或模数转换信号adc,在传统中断处理中,由于这两种中断信号存在过多的上升沿和下降沿,而给中断的侦测或获取带来较大负担。

17.在本实施例中,如图1所示,用于处理中断的电路包括第一电路(见图1中的虚线框i中的电路),第一电路i串接于第一信号(图1中a点的信号,以下以sa表示)和mcu的gpio端口之间,用于将第一信号转换成第二信号(图1中b点的信号,以下以sb表示)并输出。其中,在第一时间段τ内,第一电路i将第一信号sa转换成稳态的电平信号sb1,其可以是稳态的高电平信号,也可以是稳态的低电平信号;在第一时间段τ后的第二时间段内,第一电路i将第一信号sa直接传递到b点处,形成与第一信号sa相同的第二信号sb2。

18.图1还给出了第一电路i的具体实施电路,其在第一时间段内将第一信号sa转换成稳态的高电平的第二信号sb1,图3a给出了图1中a点处的第一信号sa的波形,此处以pwm信号为例,图3b给出了图1中b点处的第二信号sb的波形。以下根据信号传输的方向进行说明:第一或非门u1的第一输入端用于连接第一信号(图1中第一输入端与a点相连接),第一或非门u1的输出端连接第一电容c1的第一端,第一电容c1的第二端连接一上拉的第一电阻r1(或者说,第一电容c1的第二端经由第一电阻r1连接到电源电压vcc),第一电容c1的第二端同时连接第二非门u2的输入端,第二非门u2的输出端连接第一或非门u1的第二输入端,第二非门u2的输出端还输出第二信号。

19.在一实施例中,第二非门u2还可以或非门呈现,此时,第一电容c1的第二端连接该或非门u2的两个输入端,或非门u2的输出端连接第一或非门u1的第二输入端。在另一实施例中,第二非门u2还可以与非门呈现,此时第一电容c1的第二端连接该与非门u2的两个输入端,与非门u2的输出端连接第一或非门u1的第二输入端。

20.在一实施例中,a点处还连接有下拉的第三电阻r3(或者说,a点经由第三电阻r3接地)。在一实施例中,b点处还连接有下拉的第四电阻r4(或者说,b点经由第四电阻r4接地)。

21.在第一时间段τ内,开始时若第一或非门u1输出低电平(以0表示),此时由于上拉的第一电阻r1的存在,第一电容c1开始充电,第一电容c1的两侧可以视为等电平,经过u2的

取反处理后,b点处获得高电平1;此时,第一或非门u1的第二输入端输入高电平1,第一或非门u1经过或非运算后输出低电平1。也就是说,在第一电容c1充电过程中,无论第一或非门u1的第一输入端输入的第一信号sa为高电平1还是低电平0,b点输出的第二信号sb1始终为高电平1。

22.在第一电容c1充电完毕后,第一电阻r1中没有流动的电流,此时第一电容c1的第二端的电压等于vcc,或者说为高电平1,被u2取反后b点处输出的第二信号sb2为低电平0,此时输入到第一或非门u1的第二输入端,第一或非门u1经过或非运算后输出到第一电容c1第一端的信号与第一信号sa相反。这时候,如果第一信号sa为高电平1时,第一电容c1的第一端的信号为低电平0,此时第一电容c1对地放电,第一电容c1的第二端为低电平0,经由u2取反后b点处输出高电平1。如果第一信号sa为低电平0,则第一电容c1的第一端的信号为高电平1,第一电容c1不进行充放电,第一电容c1的第二端为高电平1,经由u2取反后b点处输出低电平0。综上,在第一时间段τ后的第二时间段内,第一电路i直接将第一信号sa传输至b点处,第二信号sb2等同于第一信号sa。

23.综上所述,图1举例了第一电路i,在第一时间段τ内将第一信号sa拉高为稳态高电平,从而在第一时间段τ内mcu的该输入端口不会接收到具有沿触发的中断信号。尤其是对于具有连续多个上升沿和/或下降沿的输入信号而言,其无需对每个上升沿和/或下降沿进行识别,并进行复杂的中断侦测程序,可以节约mcu的资源消耗。

24.在另一实施例中,如图2所示,第一电路i’的具体实施电路,其在第一时间段τ’内将第一信号sa转换成稳态的低电平的第二信号sb1’。以下根据信号传输的方向进行说明:第一与非门u1’的第一输入端用于连接第一信号(图1中第一输入端与a点相连接),第一与非门u1’的输出端连接第一电容c1’的第一端,第一电容c1’的第二端连接一下拉的第一电阻r1’(或者说,第一电容c1’的第二端经由第一电阻r1’接地),第一电容c1’的第二端同时连接第二非门u2’的输入端,第二非门u2’的输出端连接第一与非门u1’的第二输入端,第二非门u2’的输出端还输出第二信号sb’。在一实施例中,第二非门u2’还可以与非门呈现,此时第一电容c1’的第二端连接该与非门u2’的两个输入端,与非门u2’的输出端连接第一与非门u1’的第二输入端。在另一实施例中,第二非门u2’还可以或非门呈现,此时,第一电容c1’的第二端连接该或非门u2’的两个输入端,或非门u2’的输出端连接第一与非门u1’的第二输入端。在一实施例中,a点处还连接有下拉的第三电阻r3(或者说,a点经由第三电阻r3接地)。在一实施例中,b点处还连接有下拉的第四电阻r4(或者说,b点经由第四电阻r4接地)。其中,τ’由r1’和c1’确定。

25.在图2的实施例中,在第一时间段τ’内,在第一电容c1充电过程中,无论第一与非门u1’的第一输入端输入的第一信号sa是高电平1还是低电平0,b点输出的第二信号sb1’始终为低电平0。在第一时间段τ’后的第二时间段内,第一电路i’直接将第一信号sa传输至b点处,第二信号sb2’等同于第一信号sa。

26.图1和图2分别展示了两种第一电路i的实施方式,本发明不以此为限。

27.在一较佳的实施例中,用于处理中断的电路还包括第二电路ii,用来进一步处理第一电路i输出的第二信号sb,使获得的第三信号sc(图1和图2中的c点处的信号)具有坡度的上升沿信号或下降沿信号,从而更适合mcu的gpio端口进行侦测和处理。如图1和3所示,

28.图1和图2还给出了第二电路ii的具体实施电路,以图1为例,第二电路ii串接于第

一电路i与该mcu的该输入端口之间。沿着信号传递的方向,第二电路ii包括:第一二极管d1的p端作为输入端,第一二极管d1的n端连接下拉的第二电容c2和下拉的第二电阻r2,或者说,第一二极管d1的n端通过并联的第二电容c2和第二电阻r2接地;第一二极管d1的n端还输出第三信号sc。这样,第二信号sb为高电平时,第一二极管d1导通,对第二电容c2充电;第二信号sb为低电平时,第一二极管d1不导通,第二电容c2通过第二电阻r2对地放电。设计第二电容c2和第二电阻r2的时间常数大于输入的脉冲信号的周期,这样,在脉冲信号的高电平脉冲区域,第二电容c2始终处于充电状态;在输入的脉冲信号的低电平脉冲区域第二电容c2始终通过第二电阻r2对地放电,从而将输入的具有较陡峭的上升沿和下降沿的脉冲信号转换为具有更为缓和的上升沿信号及下降沿信号,更方便被侦测识别。较佳的,设计第二电容c2和第二电阻r2的时间常数大于1秒。通过第二电路ii的处理,将第二时间段内的图3b中第二信号sb处理为如图3c中对应的第三信号sc。

29.在一较佳的实施例中,在第一二极管d1的p端与b点之间还串接有一施密特触发器u3,施密特触发器u3的输入端连接b点,用于输入第二信号,施密特触发器u3的输出端连接第一二极管d1的p端。施密特触发器u3可以对输入的信号进行缓冲,还可以在输入的第二信号sb为低电平0时,第二电容c2可以更快地释放电荷,保持沿信号的梯度和幅度。

30.在图1和图2所示的实施例中,还可设置处理器mcu仅在第二时间段内询问该输入端口,以侦测接收到的信号中是否存在中断。这样,处理器mcu通过定时轮询的方式处理该输入端口的中断需求,从而大大提高mcu处理器的效能。

31.综上所述,本发明提供的用于处理中断的系统,其通过电路将输入的第一信号在特定的时间段内拉为稳态的高电平或低电平信号,处理器仅在这个时间段以外,通过定时轮询的方式侦测和处理该输入端口的中断需求,这样处理器无需实时进行输入信号的上升沿侦测或下降沿侦测,大大降低了处理器的负担,提升了处理器的综合效能。

32.本发明已由上述相关实施例加以描述,然而上述实施例仅为实施本发明的范例。必需指出的是,已揭露的实施例并未限制本发明的范围。相反地,在不脱离本发明的精神和范围内所作的更动与润饰,均属本发明的专利保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1