一种多通道高分辨率数据采集系统

1.本发明属于数据采集领域,可应用于各种涉及到多通道数据采集的工程中,实现同步、实时、高分辨率的多通道数据采集。

背景技术:

2.数据采集(daq),是指从传感器和其它待测设备等模拟和数字被测单元中自动采集非电量或者电量信号,送到上位机中进行分析,处理。数据采集装置广泛应用于通信、医疗、工业自动化等领域,是一种从被测目标中自动采集并测量数据信息的装置。现代科学技术和工业生产不断发展,数据采集在各种检测领域的应用更加广泛,一个良好的数据采集系统是决定一个检测系统性能优异的关键因素。随着检测目标的复杂化、检测空间范围的扩大、检测精度要求的提高,高性能的多通道数据采集系统在科研工作和工程应用中的需求越来越大。但是由于多通道数据采集系统的设计难度大、成本高,目前市面上的产品依然非常稀少,且性能尚不突出。

技术实现要素:

3.本发明针对现有的数据采集系统通道数少、采样率低、同步性差、成本高等技术的不足,提出了一种多通道高分辨率数据采集系统设计方案,可实现多通道差分信号的同步采集。

4.本发明采用如下技术方案:

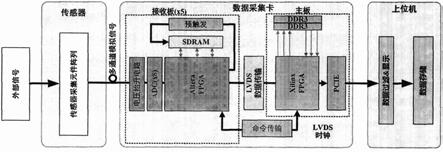

5.一种多通道高分辨率数据采集系统,包括接收板阵列和主板以及上位机软件,所述接收板阵列由5块接收板组成,所述接收板阵列和所述主板采用星型结构进行连接,可根据实际通道数需求进行拆卸与重组。

6.进一步地,所述多通道高分辨率数据采集系统的接收板硬件电路包括电压抬升电路、多通道adc采集电路、fpga控制器、sdram模块、lvds发送电路,所述电压抬升电路连接有多通道ad转换器,所述ad转换器连接有fpga控制器,所述fpga控制器连接有sdram模块与lvds发送电路。

7.进一步地,所述多通道高分辨率数据采集系统的主板硬件电路包括lvds接收电路、fpga控制器、ddr3模块、pcie接口电路、电源接口电路、接收板插槽,所述lvda接收电路连接有fpga控制器,所述fpga控制器连接有ddr3模块与pcie接口电路,并通过pcie接口与上位机软件连接。

8.进一步地,所述多通道高分辨率数据采集系统的接收板通过所述电压抬升电路,将差分输入电压抬升到所述ad转换器的输入范围,所述ad转换器的型号为ltc2320,所述ad转换器将输入的模拟信号转换为数字信号,然后将转换后的数字信号输入到所述接收板的fpga控制器中,所述接收板的fpga控制器芯片为altera ep4ce22f17c8。

9.进一步地,所述多通道高分辨率数据采集系统的多通道adc芯片采集多通道的差分信号,同时利用预触发和窗口采样的设计,减少了无用信号的掺入,减少了数据量。

10.进一步地,所述接收板通过所述接收板fpga控制器将采集的数据存储在sdram中,所述sdram的型号为w9825g6kh,然后通过所述lvds发送电路将数据上传到所述主板,每块所述接收板都通过控制信号线与所述主板连接,采用电平跳变的方式实现所述主板与所述接收板之间控制信号的快速响应。

11.进一步地,所述多通道高分辨率数据采集系统的主板采用fpga作为主控制器,对所述接收板进行控制,并对所述接收板传回的数据进行处理,所述主板的fpga控制器的芯片为xilinx

‑

xc7a35t。

12.进一步地,所述多通道高分辨率数据采集系统的主板fpga控制器接收所述接收板的数据,并将数据存入到ddr3中。

13.进一步地,数据连续采集完成后,将所述ddr3中的数据读出,经过所述pcie上传至上位机软件,上位机软件接收pcie总线传回的数据,进行通道的分离、波形滤波、数据库备份等,最终实现数据的显示与存储。

14.由于采用上述技术方案,本发明具有以下有益效果:

15.本发明针对多通道数据采集系统设计难度大、成本高、性能不突出的缺点进行优化设计,每块接收板上有8块adc芯片,每块adc芯片可以实现8通道信号的采集,从而可以实现多达320个通道数据的同步采集。

16.本发明的接收板与主板之间采用星型结构进行连接,可以根据需要采集的通道数进行自由重组与设计,应用场所更加广泛。

17.本发明采用多种触发方式进行采样,可以实现多种测量场合的要求,同时采样窗口可调可针对采集信号的脉宽以及占空比的因素进行调节,从而可以实现多种信号的测量。

18.本发明采用正弦直方图法对多通道数据采集系统数据信号进行校准,精确地计算每个adc的输出特性曲线,并对每个adc计算相应的校正函数,最后利用上位机软件进行通道的分离、波形滤波、数据库备份等,最终实现波形的显示与存储。

附图说明

19.图1为本发明中一种多通道高分辨率数据采集系统的总体结构图;

20.图2为本发明中一种多通道高分辨率数据采集系统的系统数据流展示图;

21.图3为本发明中一种多通道高分辨率数据采集系统的数据校准正弦直方图;

22.图4为本发明为本发明一种多通道高分辨率数据采集系统的上位机显示界面图。

具体实施方式

23.为使本发明的工作流程、技术方案更加清晰明了,下面结合附图和实施例对本发明作进一步详细说明。应当指出,本发明的应用范围广泛,具体实施例仅为本发明的一个典型应用案例,用于解释本发明。

24.如图1至图4所示,一种多通道高分辨率数据采集系统,包括接收板阵列、主板和上位机软件,接收板阵列由5块接收板组成,接收板阵列和主板采用星型结构进行连接,可根据实际通道数需求进行拆卸与重组。接收板硬件电路包括电压抬升电路、多通道adc采集电路、fpga控制器、sdram模块、lvds发送电路。主板硬件电路包括lvds接收电路、fpga控制器、

ddr3模块、pcie接口电路、电源接口电路、接收板插槽。

25.具体地,实施例针对差分电压数据进行采集,差分电压信号通过电压抬升电路抬升到adc的输入范围,adc的型号为ltc2320,可以实现16位无失码采样,具有8通道差分输入和宽共模范围,每个通道的采样率最大为1.5msps/ch,差动输入范围可以达到8vp_p,adc内置信号选择器,在最大采样率的情况下可以实现8通道同步采样。

26.进一步地,每块所述接收板上共有8个所述adc,每片所述adc可实现8通道数据同步采集,所述多通道高分辨率数据采集系统最多可实现320个差分通道数据的同步采集。

27.进一步地,待有通道被触发,所述主板将控制所述接收板同时开启信号的采样,接收板主控芯片为altera ep4ce22f17c8,具有低功耗,速度快,并行执行的优点,随后主控芯片将采集到的数据通过写入fifo(先入先出存储器)进行缓冲后储存到sdram中。

28.进一步地,所述daq卡的触发方式可以根据需要进行切换,包括边沿触发、电平触发、条件触发等。所述daq卡中加入了预触发和窗口采样的设计,实现了对触发点之前信号的预存,同时减少了无用信号的掺入,减少了数据量。

29.进一步地,所述接收板通过读出fifo(先入先出存储器)进行缓冲后将sdram中的数据读出,采用lvds作为所述接收板与所述主板之间的高速数据传输方式,lvds串化因子为8,每个lvds时钟可以传输8bit数据,采用电平跳变的方式实现主板与接收板之间控制信号的快速响应。利用所述主板向所述接收板发送同步lvds时钟用于同步数据流。

30.进一步地,所述主板接收到数据后,利用主板fpga控制器,通过写入fifo(先入先出存储器)进行缓冲后将数据存入ddr3中。再通过读出fifo(先入先出存储器)进行缓冲后将ddr3中的数据读出。所述主板的fpga控制器的芯片为xilinx

‑

xc7a35t,此款芯片逻辑资源更加丰富,速度更快,功耗更小,成本更加低廉。

31.进一步地,所述多通道高分辨率数据采集系统的主板通过pcie总线接口将数据上传到上位机软件。

32.进一步地,参看图3为本发明的数据校准正弦直方图,所述多通道高分辨率数据采集系统的校准采用正弦直方图法,精确地计算每个所述adc的输出特性曲线,并对每个所述adc计算相应的校正函数,采用三次多项式法对adc的非线性误差进行校准。上位机接收pcie总线传回的数据,进行通道的分离、波形滤波、数据库备份等,最终实现数据的显示与存储。

33.以上仅为本发明的具体实施例,用于解释本发明并不代表本发明的应用范围,实际应用更加广泛。任何以本发明为基础,解决基本相同的技术问题,实现基本相同的技术效果,所做出的简单变化、等同替换或者修饰等,皆涵盖于本发明的保护范围之中。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1