一种相对电源的高压稳压电路的制作方法

1.本发明涉及电源电路技术领域,具体涉及一种相对电源的高压稳压电路。

背景技术:

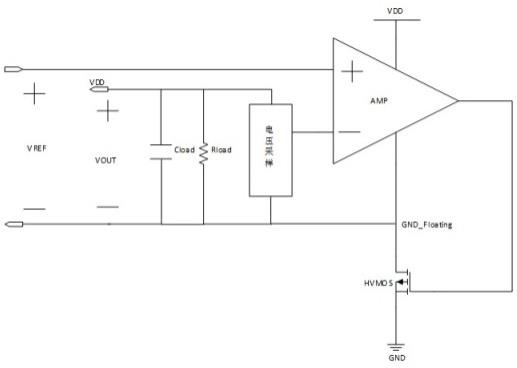

2.电源电压产生电路广泛应用于集成电路设计应用中,根据负载需要设计不同的内部电源电压。传统的技术为设计一种低压差线性稳压电路(ldo),该技术产生电压为相对低的内部电源电压。通过采样输出电压与基准电压进行比较,运算放大器调节输出驱动管的栅极电压,改变驱动管的电流能力以响应负载的变化,从而使输出电压恒定。该技术思路广泛应用于电路中,原理如图1所示。

技术实现要素:

3.为解决上述问题,本发明提出一种相对电源的高压稳压电路,可以高压工作,本发明产生电压相对电源,一端连接电源,另一端对地浮动。随着电源电压升高,产生电源的另一端也跟随电源电压升高,从而保持对电压稳定,所述电路包括mos管p1,mos管p1的漏端连接偏置电流,mos管p1的栅端连接mos管p2的栅端,mos管p2、mos管p3与mos管p4的栅端相连接,mos管p5、mos管p6与mos管p7的栅端相连接。

4.作为本发明的一种改进,所述mos管p5的漏端连接hvpmos管p8的源端,所述mos管p2的漏端连接hvpmos管p9的源端,所述hvpmos管p8的栅端接hvpmos管p9的栅端,p8、p9为高压管,可以阻挡电源的高压施加到下面的低压管n5、n6,mos管p3的漏端连接电阻r1和电阻r2,所述电阻r2接mos管n1的源端,mos管n1的漏端连接mos管p6的漏端,mos管p7的漏端连接mos管n4的漏端,mos管n4的栅端连接mos管n3的栅端,mos管n1的栅端连接mos管n2的栅端,mos管n2的漏端连接mos管p10的漏端,mos管p10的源端接电阻r1和电阻r2,mos管p10的源端连接mos管p11的源端,mos管p11的漏端连接mos管n3的漏端,所述mos管p4的漏端连接mos管p10和mos管p11的源端,所述mos管n2和mos管n3的源端相连且连接hvnmos管n7的漏端。

5.作为本发明的一种改进,所述hvpmos管p8的漏端连接mos管n5的漏端,所述hvpmos管p9的的漏端连接mos管n6的漏端,所述mos管n5的栅端连接mos管n6的栅端,所述hvnmos管n7的栅端连接mos管n6的漏端,所述mos管n5、mos管n6及hvnmos管n7的源端相连。

6.作为本发明的一种改进,所述mos管p11的源端连接电阻r3和电阻r4,电阻r4接mos管n4的源端。

7.作为本发明的一种改进,所述mos管p1、mos管n2、mos管n3及mos管n5的栅端与漏端相连。

8.作为本发明的一种改进,运算放大器的正向输入端为相对gnd_floating的参考电压vref,负向输入端为输出电压vout按比例采样电压,运算放大器的输出端连接调整管hvmos的栅极。当负载突然增加,输出电压vout减小,采样电压减小,运算输出电压变大,hvmos下拉能力增强,gnd_folating电压减小,从而是vout增加。因此产生一个相对电源的恒定电压。同时随着vdd供电电压升高,gnd_floating电压升高,hvmos漏极承担高压,可以

根据耐压需求选择相应的hvmos管。该电路仅需要一个hvnmos和两个hvpmos即可实现在vdd很宽范围内产生一个电源电压。

9.作为本发明的一种改进,随着vdd供电电压升高,gnd_floating电压升高,hvmos漏极承担高压。

10.本发明的有益效果是:本发明提供的一种相对电源的高压稳压电路,其运算放大器的正向输入端为相对gnd_floating的参考电压vref,负向输入端为输出电压vout按比例采样电压,运算放大器的输出端连接调整管hvmos的栅极。当负载突然增加,输出电压vout减小,采样电压减小,运算输出电压变大,hvmos下拉能力增强,gnd_folating电压减小,从而是vout增加。因此产生一个相对电源的恒定电压。同时随着vdd供电电压升高,gnd_floating电压升高,hvmos漏极承担高压,可以根据耐压需求选择相应的hvmos管。该电路仅需要一个hvnmos和两个hvpmos即可实现在vdd很宽范围内产生一个电源电压,本发明相对电源的电压产生电路与传统对地的电压不同,可以应用在地线不稳定的情况,并且仅使用极少高压器件即可实现。

附图说明

11.图1为现有技术中的稳压电路。

12.图2为本发明实施例1中的稳压电路。

13.图3为本发明实施例2中的稳压电路。

具体实施方式

14.下面结合附图和具体实施方式,进一步阐明本发明,应理解下述具体实施方式仅用于说明本发明而不用于限制本发明的范围。

15.实施例1:如图2所示,运算放大器的正向输入端为相对gnd_floating的参考电压vref,负向输入端为输出电压vout按比例采样电压,运算放大器的输出端连接调整管hvmos的栅极。当负载突然增加,输出电压vout减小,采样电压减小,运算输出电压变大,hvmos下拉能力增强,gnd_folating电压减小,从而是vout增加。因此产生一个相对电源的恒定电压。同时随着vdd供电电压升高,gnd_floating电压升高,hvmos漏极承担高压,可以根据耐压需求选择相应的hvmos管。该电路仅需要一个hvnmos和两个hvpmos即可实现在vdd很宽范围内产生一个电源电压。随着vdd供电电压升高,gnd_floating电压升高,hvmos漏极承担高压。

16.实施例2:如图3所示,所述电路包括mos管p1,mos管p1的漏端连接偏置电流,mos管p1的栅端连接mos管p2的栅端,mos管p2、mos管p3与mos管p4的栅端相连接,mos管p5、mos管p6与mos管p7的栅端相连接。所述mos管p5的漏端连接hvpmos管p8的源端,所述mos管p2的漏端连接hvpmos管p9的源端,所述hvpmos管p8的栅端接hvpmos管p9的栅端,mos管p3的漏端连接电阻r1和电阻r2,所述电阻r2接mos管n1的源端,mos管n1的漏端连接mos管p6的漏端,mos管p7的漏端连接mos管n4的漏端,mos管n4的栅端连接mos管n3的栅端,mos管n1的栅端连接mos管n2的栅端,mos管n2的漏端连接mos管p10的漏端,mos管p10的源端接电阻r1和电阻r2,mos管p10的源端连接mos管p11的源端,mos管p11的漏端连接mos管n3的漏端,所述mos管p4的漏端连接mos管p10和mos管p11的源端,所述mos管n2和mos管n3的源端相连且连接hvnmos

管n7的漏端。所述hvpmos管p8的漏端连接mos管n5的漏端,所述hvpmos管p9的的漏端连接mos管n6的漏端,所述mos管n5的栅端连接mos管n6的栅端,所述hvnmos管n7的栅端连接mos管n6的漏端,所述mos管n5、mos管n6及hvnmos管n7的源端相连。所述mos管p11的源端连接电阻r3和电阻r4,电阻r4接mos管n4的源端。所述mos管p1、mos管n2、mos管n3及mos管n5的栅端与漏端相连。

17.在本发明中,基准电流流过r1和r2产生基准电压作为运算放大器的正输入端,输出电压经过r3和r4进行采样反馈回运算放大器的负向输入端,运算放大器的输出调节n7管的栅压,从而调节vout。

18.其中vout电压如下:vout=ibias*r2*(r3+r4)/r4;通过调节r3和r4可以灵活调节相对电源输出电压,很容易将ibias*r2设计为零温度系数,从而vout也为灵温度系数。

19.在本发明的描述中,需要说明的是,术语“上”、“下”、“左”、“右”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制;此外,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本发明中的具体含义。

20.最后应说明的是:以上所述的实施例仅用于说明本发明的技术方案,而非对其限制,尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解其依然可以对前述实施例所记载的技术方案进行修改,或者对其中部分或全部技术特征进行等同替换,而这些修改或替换,并不使相应技术方案的本质脱离本发明实施例技术方案的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1